СОСТАВ И ФУНКЦИОНИРОВАНИЕ МИНИМАЛЬНОЙ ЭВМ С ШИННОЙ ОРГАНИЗАЦИЕЙ

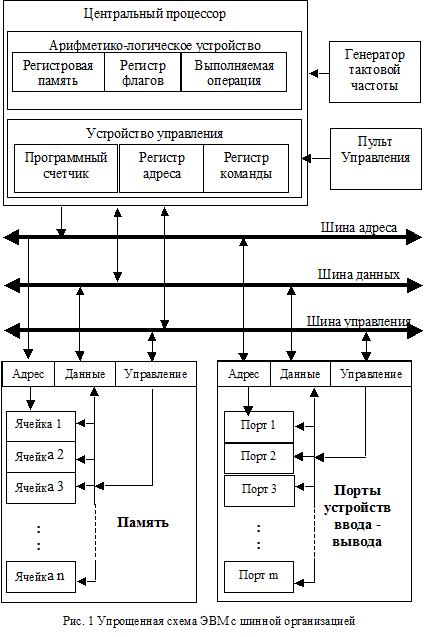

Шинная организация является простейшей формой организации ЭВМ. Подобная ЭВМ имеет в своем составе следующие функциональные блоки (см. рис. 1).

Устройство управления (УУ) - часть центрального процессора (ЦП), вырабатывает последовательность управляющих сигналов, обеспечивающих выборку и выполнение команд. В соответствии с типом реализуемой операции УУ формирует набор команд низкого уровня для арифметико-логического устройства и других устройств. Эти команды задают последовательность простейших низкоуровневых операций, таких, как пересылка данных, сдвиг данных, установка и анализ признаков, запоминание результатов и др. Такие элементарные низкоуровневые операции называют микрооперациями, а команды, формируемые устройством управления, называются микрокомандами. Последовательность микрокоманд, соответствующая одной команде, называется микропрограммой.

В простейшем случае УУ имеет в своем составе три устройства - регистр команды, который содержит код команды во время ее выполнения, программный счетчик, в котором содержится адрес очередной выполн команды, регистр адреса, в котором вычисляются адреса операндов, находящихся в памяти. Для связи пользователя с ЭВМ может быть предусмотрен пульт управления, который позволяет выполнять такие действия как сброс ЭВМ в начальное состояние, просмотр регистра или ячейки памяти, запись адреса в программный счетчик, пошаговое выполнение программы при ее отладке и т. д.

Арифметико-логическое устройство(АЛУ). Обычно формирует по двум входным переменным одну - выходную, выполняя заданную функцию (сложение, вычитание, сдвиг и т. д.). Выполняемая функция определяется микрокомандой, получаемой от устройства управления.

Арифметико-логическое устройство содержит в своем составе устройство, хранящее характеристику результата выполнения операции над данными и называемое флаговым регистром. Отметим пока, что отдельные разряды этого регистра указывают на равенство результата операции нулю, знак результата операции (плюс или минус), правильность выполнения операции (наличие переноса за пределы разрядной сетки или переполнения). Программный анализ флагов позволяет производить операции ветвления программы в зависимости от конкретных значений данных.

Кроме того, в АЛУ имеется набор программно - доступных быстродействующих ячеек памяти, которые называются регистрами процессора. Регистры составляют основу архитектуры процессора. Среди обязательного набора регистров можно отметить следующие. Регистр данных служит для временного хранения промежуточных результатов при выполнении операций. Регистр - аккумулятор содержит данные временного хранения, которые используются в процессе вычислений (например, в нем формируется результат выполнения команды умножения). Регистр - указатель стека используется при операциях со стеком, т. е. такой структурой данных, которая работает по принципу: последним вошел - первым вышел, т.е. последнее записанное в него значение извлекается из него первым. Пока отметим только, что стеки используются для организации подпрограмм. Индексные, указательные и базовые регистры используются для хранения и вычисления адресов операндов в памяти. Регистры - счетчики используются для организации циклических участков в программах. Регистры общего назначения, имеющиеся во многих ЭВМ, могут использоваться для любых целей. Точное назначение такого регистра определяет программист при написании программы. Они могут использоваться для временного хранения данных, в качестве аккумуляторов, а также в качестве индексных, базовых, указательных регистров. Количество регистров и связей между ними оказывает существенное влияние на сложность и стоимость процессора. Однако, с другой стороны, наличие большого количества регистров с богатым набором возможностей упрощает программирование и повышает гибкость программного обеспечения. Кроме перечисленных регистров в состав АЛУ могут входить внутренние системные регистры, недоступные программно и используемые во время внутренних пересылок информации при выполнении команд.

Память (ПАМ) - устройство, предназначенное для запоминания, хранения и выборки программ и данных. Память состоит из конечного числа ячеек, каждая из которых имеет свой уникальный номер или адрес. Доступ к ячейке осуществляется указанием ее адреса. Память способна выполнять два вида операций над данными - чтение с сохранением содержимого и запись нового значения со стиранием предыдущего. Как уже говорилось выше, каждая ячейка памяти может использоваться для хранения либо порции данных, либо команды. В большинстве современных ЭВМ минимально адресуемым элементом памяти является байт - поле из 8 бит. Совокупность битов, которые арифметико-логическое устройство может одновременно поместить в регистр или обработать называют обычно машинным словом. Об организации хранения данных в памяти ЭВМ более подробно будет рассказано в следующих разделах пособия.

Периферийные устройства (ПУ). В их число входят устройства двух типов - устройства внешней памяти, предназначенные для долговременного хранения данных большого объема и программ, и коммуникационные устройства, предназначенные для связи ЭВМ с внешним миром (с пользователем, другими ЭВМ и т. д.). Обмен данными с внешним устройством осуществляется через порты ввода - вывода. Порт (в переводе с английского port - ворота, дверь, отверстие) - это, с точки зрения процессора, адрес. По аналогии с ячейками памяти порты можно рассматривать как ячейки, через которые можно что-либо записать в периферийное устройство или наоборот - прочитать из него. Так же, как и ячейки памяти, порты имеют уникальные номера - адреса портов ввода - вывода.

Объединение функциональных блоков в ЭВМ осуществляется посредством следующей системы шин: шины данных, по которой осуществляется обмен информацией между блоками ЭВМ, шины адреса, используемой для передачи адресов (номеров ячеек памяти или портов ввода - вывода, к которым производится обращение), и шины управления для передачи управляющих сигналов. Совокупность этих трех шин называют системной шиной, системной магистралью или системным интерфейсом. Состав и назначение линий шины, правила их использования, виды передаваемых по шине сигналов и другие характеристики шины могут существенно различаться у разных видов ЭВМ. Однако есть принципиально общие закономерности в организации шин.

Шина состоит из отдельных проводников (линий). Сигналы по линиям шины могут передаваться либо импульсами (наличие импульса соответствует логической единице, а отсутствие импульса – нулю), либо уровнем напряжения (например, высокий уровень - логическая единица, низкий – ноль). Шириной шины называется количество линий (проводников), входящих в состав шины. Ширина шины адреса определяет размер адресного пространства ЭВМ. Если, например, количество линий адреса, используемых для адресации памяти, равно 20, то общее количество адресуемых ячеек памяти составит 220, т.е. примерно один миллион ячеек (точнее 1048576 ячеек).

Обычно на шине в любой момент можно выделить два активных устройства. Одно из них называется задатчиком и инициирует операцию обмена данными (формирует адреса и управляющие сигналы), другое называется исполнителем и выполняет операцию (дешифрирует адреса и управляющие сигналы и принимает или передает данные). В большинстве случаев задатчиком является ЦП. Память всегда выступает только в качестве исполнителя.

Из управляющих линий пока выделим следующие.

Линия занятости. Если она в состоянии “шина свободна”, любой задатчик, включая процессор, может начать операцию обмена данными на шине, иначе задатчику придется ожидать, пока шина не освободится.

Линии выполняемой операции.Указывают, какая именно операция будет выполняться. Как минимум необходим следующий набор операций - чтение (задатчик принимает данные от исполнителя), запись (задатчик передает данные исполнителю).

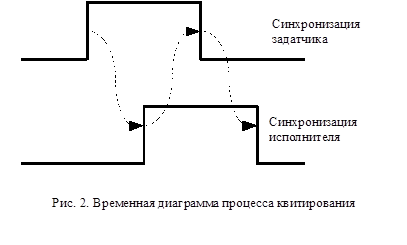

Линии синхронизации.Синхронизация задатчиков и исполнителей может осуществляться по-разному, один из распространенных способов состоит в следующем. Задатчик в процессе операции обмена выставляет на шине сигнал синхронизации задатчика. Сигнал распространяется по шине и через  некоторое время достигает исполнителя. Получив сигнал от задатчика, исполнитель выполняет операцию обмена (передает или принимает данные) и выставляет на шине ответный сигнал синхронизации исполнителя, который также начинает распространяться по шине (рис. 2). Получив ответ от исполнителя, задатчик освобождает шину.

некоторое время достигает исполнителя. Получив сигнал от задатчика, исполнитель выполняет операцию обмена (передает или принимает данные) и выставляет на шине ответный сигнал синхронизации исполнителя, который также начинает распространяться по шине (рис. 2). Получив ответ от исполнителя, задатчик освобождает шину.

Операция “считывание ячейки памяти” будет выполняться следующим образом. Процессор переводит шину в состояние “занято”, на адресную шину помещает адрес требуемой ячейки памяти, устанавливает на шине управления сигнал “чтение”, выдает сигнал синхронизации задатчика. Память принимает адрес, дешифрирует его, находит нужную ячейку и помещает ее содержимое на шину данных. Далее память выдает сигнал синхронизации исполнителя. Получив ответ от памяти, процессор считывает данные с шины, снимает свои управляющие сигналы и освобождает шину.

При операции “запись в память” процессору необходимо выполнить следующие действия. Шина переводится в состояние “занято”, адрес требуемой ячейки памяти помещается на шину адреса. Данные, которые необходимо записать в память, помещаются на шину данных. На шине управления устанавливается сигнал “запись”, выдается сигнал синхронизации задатчика. Память принимает адрес, дешифрирует его, помещает в соответствующую ячейку данные с шины и выдает сигнал синхронизации исполнителя. Получив ответ от памяти, процессор снимает управляющие сигналы и освобождает шину.

Такой способ обмена данными называется асинхронным обменом, а сама операция запроса/подтверждения носит названия квитирования или рукопожатия (handshake) и широко применяется при построении системы шин различного назначения в различных ЭВМ.

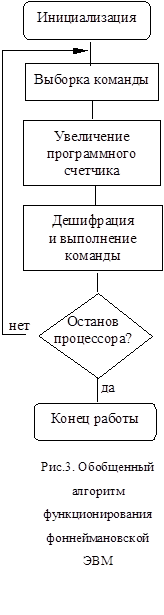

Функционирование ЭВМ с приведенной выше структурой можно описать следующим обобщенным алгоритмом (см. рис. 3).

1.Инициализация. После включения ЭВМ или операции сброса в регистры центрального процессора заносятся некоторые начальные значения. Обычно в процессе инициализации в память ЭВМ помещается программа, называемая первичным загрузчиком. Основное назначение первичного загрузчика - загрузить в память с устройства внешней памяти операционную систему. Эта программа может быть размещена в энергонезависимом устройстве памяти или автоматически считываться с некоторого устройства внешней памяти. Мы не будем здесь подробно останавливаться на механизмах загрузки операционной системы, тем более, что они могут существенно различаться для разных типов ЭВМ. Пока будем полагать, что в памяти некоторым “волшебным” образом оказалась первая из подлежащих выполнению программ. Программному счетчику присваивается начальное значение, равное адресу первой команды программы указанной выше.

2.  Центральный процессор производит операцию считывания команды из памяти. В качестве адреса ячейки памяти используется содержимое программного счетчика.

Центральный процессор производит операцию считывания команды из памяти. В качестве адреса ячейки памяти используется содержимое программного счетчика.

3.Содержимое считанной ячейки памяти интерпретируется процессором как команда и помещается в регистр команды. Устройство управления приступает к интерпретации прочитанной команды. По полю кода операции из первого слова команды устройство управления определяет ее длину, и, если это необходимо, организует дополнительные операции считывания, пока вся команда полностью не будет прочитана процессором. Вычисленная длина команды прибавляется к исходному содержимому программного счетчика, и когда команда полностью прочитана, программный счетчик будет хранить адрес следующей команды.

4.По адресным полям команды устройство управления определяет, имеет ли команда операнды в памяти. Если это так, на основе указанных в адресных полях режимов адресации вычисляются адреса операндов и производятся операции чтения памяти для считывания операндов.

5.Устройство управления и арифметико-логическое устройство выполняют операцию, указанную в поле кода операции команды. Во флаговом регистре процессора запоминаются признаки результата операции (равно нулю или нет, знак результата, наличие переполнения и т. д.).

6.Если это необходимо, устройство управления выполняет операцию записи для того, чтобы поместить результат выполнения команды в память.

7.Если последняя команда не была командой “ОСТАНОВИТЬ ПРОЦЕССОР”, то описанная последовательность действий повторяется, начиная с шага 1.

Описанная последовательность действий центрального процессора с шага 1 до шага 6 называется циклом процессора.

Большинство мини- и микроЭВМ имеют шинную организацию и их поведение описывается приведенным выше алгоритмом. В различных конкретных ЭВМ реализация этого алгоритма может несколько отличаться. Так, например, по-разному может осуществляться синхронизация задатчиков и исполнителей, процессор может считывать из памяти не одну команду, а сразу несколько, и хранить их в специальной очереди команд, часто используемые программой команды и данные могут храниться не в основной памяти ЭВМ, а в быстродействующей буферной памяти и т. д. Однако в рамках данного руководства мы не будем углубляться в подобные детали и ограничимся утверждением, что без учета отдельных деталей.

Дата добавления: 2021-02-19; просмотров: 489;