Транзисторно-транзисторні логічні елементи

2.2.1. Загальна характеристика транзисторно-транзисторних логічних елементів

Елементи ТТЛ з’явилися в результаті розвитку схем ДТЛ у напрямку скорочення числа компонентів, зменшення ємності переходів і врахування специфіки інтегральної технології. На початку важливою особливістю елементів ТТЛ було використання на вході багатоемітерного транзистора (БЕТ) для реалізації операції І. Кожен емітер БЕТ використовується як логічний вхід. Число емітерів визначає коефіцієнт об’єднання за входом NІ=1…8 і більше.

Промисловість випускає такі серії ТТЛ і ТТЛШ:

стандартної середньої швидкодії (ТТЛ) – К133, К155, швидкодіючі – К130, К131, К599 і малопотужні – К134, К158 (1963 р.);

стандартної середньої швидкодії (ТТЛ) – К133, К155, швидкодіючі – К130, К131, К599 і малопотужні – К134, К158 (1963 р.);

стандартні швидкодіючі (ТТЛ) –К530,К531 і малопотужні – К533, К555 (1970 р.);

стандартні швидкодіючі (ТТЛ) –К530,К531 і малопотужні – К533, К555 (1970 р.);

над швидкодіючі (ТТЛ) –КР1530 (тип АS), високої швидкодії – КР1531 (тип FAST) і малопотужні – КР1533 (тип ALS) (1980 р.). У цих серіях застосована ізопланарна технологія на основі іонної імплантації, прецизійної фотолітографії, яка забезпечує малі площі і ємності переходів.

над швидкодіючі (ТТЛ) –КР1530 (тип АS), високої швидкодії – КР1531 (тип FAST) і малопотужні – КР1533 (тип ALS) (1980 р.). У цих серіях застосована ізопланарна технологія на основі іонної імплантації, прецизійної фотолітографії, яка забезпечує малі площі і ємності переходів.

2.2.2. Транзисторно-транзисторний логічний елемент з простим інвертором

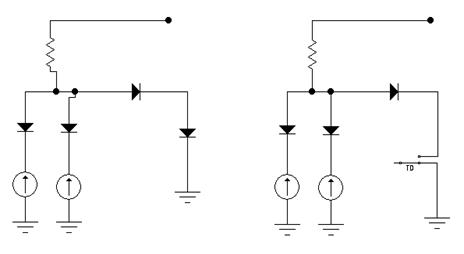

Схема найпростішого ТТЛ містить БЕТ, колектор якого підключено до бази інвертую чого транзистора VT2 рис. 2.11, а).

Багатоемітерний транзистор виконує операцію І, транзистор VT2 – операцію НЕ. Тому елемент в цілому реалізує функцію  . У першому наближенні БЕТ з топологією, показано на рис. 2.11, б, розглядаються як сукупність із n (за кількістю емітерів) окремих транзисторів із спільними базою і колектором. Для виключення взаємного впливу емітерні переходи розташовуються один від одного на відстані 10…15 мкм, що перевищує дифузійну довжину пробігу носіїв у базовому прошарку.

. У першому наближенні БЕТ з топологією, показано на рис. 2.11, б, розглядаються як сукупність із n (за кількістю емітерів) окремих транзисторів із спільними базою і колектором. Для виключення взаємного впливу емітерні переходи розташовуються один від одного на відстані 10…15 мкм, що перевищує дифузійну довжину пробігу носіїв у базовому прошарку.

У схемі ТТЛ елемента БЕТ працює в двох основних режимах – інверсному і насичення. Процеси, що відбуваються в інверсному режимі, відображають еквівалентною схемою (рис. 2. 12. а).

Інверсний режим виникає після подачі на входи високих рівнів напруги UІН. В результаті емітери Е1 і Е2 закриваються, колекторний перехід знаходиться під прямою напругою U*=0,8 В і він інжектує електрони в спільну базу.

З метою зменшення зворотних струмів ІІН, які входять в емітер, технологічними методами спеціально зменшують значення інверсного коефіцієнта передачі струму bІ від бази до емітера до 0,01-0,02. У цьому випадку значення струму ІІН знаходиться з співвідношення

де  - струм бази БЕТ.

- струм бази БЕТ.

На основі схеми рис 2.12., а для струму  , що виходить з колектора БЕТ, справедливий вираз

, що виходить з колектора БЕТ, справедливий вираз

.

.

Струм  знаходиться з рівності

знаходиться з рівності

,

,

де 2U*=1,6 В – сумарне падіння напруги на двох послідовно ввімкнених кремнієвих переходах – колектора БЕТ і бази VT2. Для типових значень UСС=5 В, R=3 кОм, отримаємо:

=(5-1,6)/3*103=1,12 мА;

=(5-1,6)/3*103=1,12 мА;

ІІН=0,02*1,12*10-3=25 мкА;

.

.

Таким чином, значення колекторного струму  достатнє для надійного насичення транзистора VT2, при цьому на виході встановлюється низький рівень напруги UOL≤0,1 В.

достатнє для надійного насичення транзистора VT2, при цьому на виході встановлюється низький рівень напруги UOL≤0,1 В.

Режим насичення виникає при подачі на один з входів (або на обидва), наприклад Х1, низького рівня напруги UІL (рис. 2. 12, б). При цьому емітер Е1 відкривається, оскільки на ньому падіння напруги U*=0,8 В, й інжектує електрони в базу БЕТ.

Колекторний перехід БЕТ також знаходиться під прямим зміщенням. Проте він не може приймати електрони, це рівнозначно появі струму, який входить в колектор, чого не дозволяє база транзистора VT2. Вважають, що у колі колектора БЕТ ввімкнено нескінченно великий опір навантаження, тому в області колектора БЕТ накопичується об’ємний заряд електронів, що характерно для режиму насичення. Транзистор VT2 – закритий і на його колекторі встановлюється високий рівень напруги UOН» UСС.

Значення витікаючого (від’ємного) з відкритого емітера Е1 струму ІІL знаходиться з рівності

IIL=[UCC-(UIL+U*)]/R.

Прийнявши, що UIL=0,4 В, отримаємо ІІL=1,23 мА.

Таким чином, у розглянутій схемі елемента ТТЛ практично постійний струм бази  комутується або в базу транзистора VT2 (інверсний режим), або у відкритий емітер БЕТ (режим насичення).

комутується або в базу транзистора VT2 (інверсний режим), або у відкритий емітер БЕТ (режим насичення).

Дата добавления: 2016-07-27; просмотров: 3183;