Транзисторна логіка

Елементи ДТЛ

| Х1 | Х2 | F |

У цих елементах операції диз’юнкції і кон’юнкції реалізуються за допомогою діодних схем, а операції заперечення виконує інвертор на основі транзисторного ключа. Логіка роботи двоходового елемента НЕ ЧИ подана в табл. 2.4. на основі якої отримуємо вираз для булевої функції

F=

Використовуючи принцип суперпозиції, функцію F можна записати для довільного числа змінних:

F=

Схема ДТЛ-елемента, що реалізує булеву операцію НЕ ЧИ для двох змінних, і його умовне графічне зображення показано на рис. 2.5.

Схему ДТЛ-елемента НЕ ЧИ будують підключенням виходу діодного елемента ЧИ до входу інвертора. Діоди зміщення VD3 і VD4 відіграють роль, як і у схемі, рис. 2.4. а. Через резистор зміщення Rзм протікає струм Ік0. Транзит

тор VT1 відкривається і формує низький рівень вихідної напруги UOL тільки у тому випадку, коли на одному чи обох входах є високий рівень напруги UІН. При цьому вмикаючий струм ІБ1 проходить від джерела вхідних сигналів.

Часові діаграми роботи (ідеалізовані) елемента НЕ ЧИ показані на рис. 2.6. Тривалість перехідних процесів практично визначається швидкодією транзистора.

Логіка роботи двоходового елемента НЕ І зображена в табл. 2.5, на основі якої отримуємо вираз для булевої функції F=  . На основі принципу суперпозиції функцію F можна записати для довільного числа змінних:

. На основі принципу суперпозиції функцію F можна записати для довільного числа змінних:

F=

|

Схема ДТЛ-елемента, що реалізує булеву операцію НЕ І для двох змінних Х1 і Х2 та його графічне позначення показані на рис. 2.7.

| X1 | X2 | F |

Схему ДТЛ-елемента НЕ І створюють підключенням діодного елемента І до входу інвертора. Діоди зміщення VD3 і VD4 відіграють роль, як і у схемі, зображеній на рис 2.4.

Транзистор VT1 відкривається і формує низький рівень вихідної напруги UOL тільки при співпадінні високих рівнів вхідних сигналів UІН на обох входах одночасно. При цьому вмикаючий струм ІБ1 протікає від джерела струму UСС по колу: резистор R, діоди VD3 і VD4 і база транзистора VT1. При подачі хоча б на один з входів (або на обидва) сигналу низького рівня весь струм від джерела живлення UСС проходить по колу: резистор R, VD3 або VD4 (або обидва) на відповідне джерело вхідних сигналів. В результаті цього транзистор VT1 закривається і на виході встановлюється високий рівень напруги UOН. Тривалість пе

ремикання елемента практично визначається швидкодією транзистора. Часові діаграми роботи елемента НЕ І показано на рис. 2.8.

ремикання елемента практично визначається швидкодією транзистора. Часові діаграми роботи елемента НЕ І показано на рис. 2.8.

Транзисторна логіка

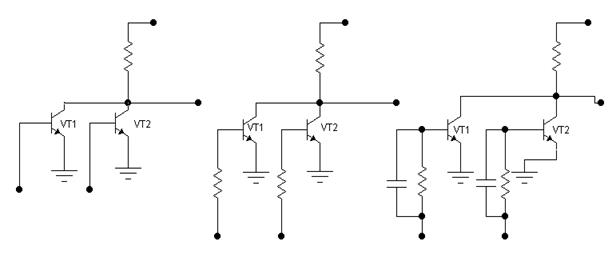

Елементи ТЛ будують паралельним підключенням колекторів транзисторів до спільного колектора навантаження RК. Вихідна напруга знімається з об’єднаних колекторів. Якщо на один із входів подається високий рівень напруги UIH, то відповідний транзистор відкривається і на виході транзистора встановлюється низький рівень напруги UOL. На виході формується високий рівень напруги тільки у випадку подачі на всі входи низьких рівнів UIL.

Логіка роботи елементів ТЛ задана в таблиці 2.4. В елементах ТЛБЗ вхідні сигнали подають безпосередньо на бази транзисторів VT1 і VT2 (рис. 2.9,а). У схемі ТЛРЗ у коло бази транзистора ввімкнено резистори RБ (рис. 2.9, б).

У схемі ТЛРКЗ для прискорення перехідних процесів резистори RБ шунтовані конденсатором СБ. Їхня роль описана при розгляді схеми інвертора (рис. 2.4). Часові діаграми роботи елементів ТЛ збігаються з процесами, зображеними на рис. 2.6.

Інтегральна інжекційна логіка

Різновидом транзисторних схем є елементи інтегральної інжекційної логіки (ІІЛ або І2Л). Схемотехніку І2Л використовують для побудови мікропроцесорних і запам’ятовуючих ВІС (серії К582, К583, К584 та ін.).

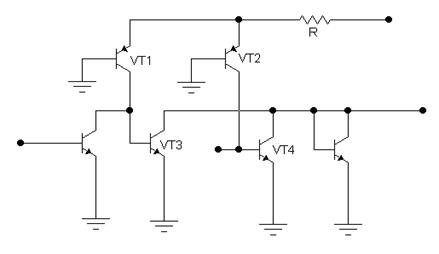

Схема логічного елемента І2Л зображена на рис. 2.10.

Схема вміщує інжекційні p-n-p транзистори VT1 і VT2,ввімкнені за схемою зі спільною базою, і вхідні багатоколекторні n-p-n транзистори VT3 і VT4, увімкнені за схемою зі спільним емітером. Емітери транзисторів VT1 і VT2 називаються інжекторами, а протікаючий через них дірковий струм – інжекційним. Кожен з транзисторів VT1 і VT2 утворює разом із джерелом живлення і зовнішнім резистором R джерело струму, яке живить індивідуальним струмом ІТ входи транзисторів VT3 і VT4.

Особливостями елементів І2Л є:

«безрезисторність», характерна для МОН-структур, яка вперше була реалізована в схемотехніці І2Л;

«безрезисторність», характерна для МОН-структур, яка вперше була реалізована в схемотехніці І2Л;

з’єднання областей бази і колектора інжекційних p-n-p транзисторів відповідно з областями емітера і колектора вхідних n-p-n транзисторів, а також мале число схемних компонентів і з’єднань між ними (число операцій маскування і дифузії в два рази менше в порівнянні з елементами ТТЛ);

з’єднання областей бази і колектора інжекційних p-n-p транзисторів відповідно з областями емітера і колектора вхідних n-p-n транзисторів, а також мале число схемних компонентів і з’єднань між ними (число операцій маскування і дифузії в два рази менше в порівнянні з елементами ТТЛ);

низький рівень напруги UL=0,01 В знімається з колектора насиченого транзистора, а високий рівень напруги UН=0,8 В – з колектора закритого транзистора, причому цей рівень обмежується напругою на базі насиченого транзистора навантаження; використовується режим мікро струмів, в якому струми колектора змінюються від десятків до сотень мікроампер; працездатність елементів зберігається при зміні значення струму в них на декілька порядків;

низький рівень напруги UL=0,01 В знімається з колектора насиченого транзистора, а високий рівень напруги UН=0,8 В – з колектора закритого транзистора, причому цей рівень обмежується напругою на базі насиченого транзистора навантаження; використовується режим мікро струмів, в якому струми колектора змінюються від десятків до сотень мікроампер; працездатність елементів зберігається при зміні значення струму в них на декілька порядків;

на колекторах вхідного транзистора реалізується інверсія змінної, а на сполучених колекторах транзисторів VT3 і VT4 виконується операція НЕ ЧИ.

на колекторах вхідного транзистора реалізується інверсія змінної, а на сполучених колекторах транзисторів VT3 і VT4 виконується операція НЕ ЧИ.

Вхідні транзистори керуються перемиканням струму на їхніх входах. Якщо до входу Х1 підключений колектор лівого насиченого транзистора, то струм ІТ замикається на ньому і не надходить у базу транзистора VT3, який закривається і створює на своїх колекторах режим розімкнутих контактів. Якщо до входу Х1 підключений колектор лівого закритого транзистора, то струм ІТ входить на базу VT3, насичує цього і забезпечує на колекторах режим замкнутих контактів.

Затримка поширення сигналу в елементі І2Л при струмі 100мкА приблизно становить 5-10 нс, потужність споживання – до 20 мкВт, робота перемикання приблизно становить 0,1 пДж (наприклад у ТТЛ серії КР1533 робота перемикання складає :пДж). Зазначені властивості елементів І2Л і ВІС на їх основі надають їм технологічності, компактності, вони мають невисоку вартість при високій швидкодії.

Дата добавления: 2016-07-27; просмотров: 3450;