Тема 17 ЦИФРОВЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА

Краткие теоретические сведения

Номенклатура микросхем ТТЛ и КМОП весьма разнообразна: от простых логических элементов до готовых функциональных узлов – счетчиков, регистров, запоминающих и арифметико-логических устройств. Элементы ТТЛ являются усовершенствованием диодно-транзисторной логики (ДТЛ), заменой диодной сборки многоэмиттерным транзистором (МЭТ). Многоэмиттерный транзистор представляет собой транзисторную структуру, имеющую до восьми эмиттеров, общую базу и общий коллектор, и непосредственно взаимодействующих друг с другом только за счет движения основных носителей.

Эмиттерные переходы МЭТ выполняют функции входных диодов в схемах ДТЛ, а коллекторный переход – роль смещающего диода. Характерной особенностью элементов ТТЛ является высокая помехоустойчивость, большое быстродействие, хорошая нагрузочная способность, малая потребляемая мощность, высокая надежность, малая стоимость.

Принципиальная электрическая схема, условное обозначение и временные диаграммы базового логического элемента ТТЛ, выполняющего операцию И-НЕ (элемент Шеффера), приведены на рис. 1.

Схема базового элемента ТТЛ состоит из двух частей. Входная часть реализует логическую функцию И с помощью VT1 и резистора R1. Выходная цепь реализует функцию НЕ и содержит сложный инвертор на транзисторах VT2…VT4. Сложный инвертор включает в свой состав простой инвертор (VT2, R2) и эмиттерный повторитель (VT3) с динамической нагрузкой (VT4), которая управляется эмиттерным током транзистора VT2. Простой инвертор в этой схеме (VT2) является фазоинверсным каскадом. Если транзистор VT2 открыт, то через него протекает большой эмиттерный ток, который является базовым током транзистора VT4. Транзистор VT4 открывается и переходит в режим насыщения, а транзистор VT3 закрывается низким коллекторным потенциалом транзистора VT2. Выходное напряжение близко к нулю. Если транзистор VT2 закрыт, то транзистор VT3 открыт, поскольку потенциал базы транзистора VT3 близок к Uип, а транзистор VT4 закрыт. Выходное напряжение имеет высокий уровень и соответствует логической единице. При запирании транзистора VT4 ток рассасывания избыточных носителей из базы транзистора VT4 протекает через резистор R3 на землю. Резистор R4 ограничивает ток выходного каскада во время перехода схемы из открытого состояния в закрытое, когда транзистор VT3 уже открылся, а транзистор VT4 находится в режиме насыщения. Диод VD обеспечивает надежное запирание транзистора VT3 при напряжении на входе схемы равном нулю.

Рис. 17.1

Рассмотрим принцип работы схемы. Если хотя бы на один из входов подано напряжение логического нуля, то соответствующий эмиттерный переход многоэмиттерного транзистора VT1 открывается. Ток базы  транзистора VT1 потечет во входную цепь, при этом ток коллектора VT1 уменьшается, коллекторный переход открывается и транзистор VT1 насыщается по коллекторной цепи. Напряжение на базе транзистора VT2 равно сумме входного напряжения и остаточного напряжения на насыщенном транзисторе VT1:

транзистора VT1 потечет во входную цепь, при этом ток коллектора VT1 уменьшается, коллекторный переход открывается и транзистор VT1 насыщается по коллекторной цепи. Напряжение на базе транзистора VT2 равно сумме входного напряжения и остаточного напряжения на насыщенном транзисторе VT1:

.

.

Поэтому транзистор VT2 запирается, а транзистор VT3 и диод VD открываются высоким потенциалом коллектора транзистора VT2. Транзистор VT4 закрыт. Напряжение на выходе имеет высокий уровень и соответствует логический единице ("1").

Если на всех логических входах действуют высокие уровни напряжения, то эмиттерные переходы транзистора VT1 закрываются, VT1 работает в инверсном активном режиме. Ток от источника Uип через R1 и открытый коллекторный переход транзистора VT1 поступает в базу транзистора VT2. Транзисторы VT2, VT4 открываются, и на выходе схемы имеется уровень напряжения, соответствующий логическому нулю ("0"). Транзистор VT3 и диод VD закрыты.

Базовые элементы различных серий ТТЛ различаются только инверторами, которые должны улучшать переходные характеристики, повышать помехоустойчивость и нагрузочную способность.

Наибольшее распространение получили две разновидности логических схем на полевых транзисторах:

МДП-логика с нагрузочным транзистором;

логика на комплементарных транзисторах (КМОП).

Перспективными являются логические схемы, выполненные на комплементарных МОП транзисторах (КМОП-логика). Комбинируя различные включения этих транзисторов, можно получить заданную логическую функцию. Если транзистор с каналом n-типа непосредственно подключен к шине "земля", а транзистор с каналом p-типа – к источнику питания, то логическая схема работает в режиме положительной логики. На рис. 2,а и рис. 2,б представлены схемы КМОП-логики, реализующие логические операции И-НЕ и ИЛИ-НЕ.

Реализация логической функции И-НЕ получается последовательным соединением МОП-транзисторов с каналом n-типа и параллельным соединением МОП-транзисторов с каналом p-типа, которые открыты при напряжениях затворов, близких к нулю. Если на вход 1 (см. рис. 17.2,а) подать сигнал логического нуля, то транзистор VT3 закрыт, а транзистор VT2 открыт и выходное напряжение близко к напряжению источника питания. Если на все входы подать сигнал логической единицы, то транзисторы VT3 и VT4 открыты, а транзисторы VT1 и VT2 закрыты, и выходное напряжение стремится к потенциалу земли, т.е. на выходе схемы – логический нуль.

Для построения схемы ИЛИ-НЕ требуется последовательное включение МОП-транзисторов с каналом p-типа и параллельное включение транзисторов с каналом n-типа (положительная логика) (см. рис. 17.2,б). Схема работает так же, как и предыдущая. Когда на всех входах действует высокий потенциал (логическая единица), транзисторы VT3 и VT4 открываются, а p-канальные транзисторы закрываются. Выходное напряжение определяется падением напряжения на открытых транзисторах и соответствует логическому нулю. Если на один из входов подается сигнал логической единицы, то этот n-канальный транзистор открывается и выходное напряжение определяется падением напряжения на этом открытом транзисторе.

а б

Рис. 17.2

Микросхемы на КМОП-транзисторах потребляют очень малую мощность при сравнительно высоком быстродействии.

Основные параметры являются общими для всех существующих и возможных логических ИМС и позволяют сравнивать между собой микросхемы различных типов.

5.1. Основные параметры и характеристики

К основным параметрам логических схем относят: мощность потребления, уровни выходных напряжений, время задержки распространения сигнала, время задержки включения и выключения, входные токи, статическую помехозащищенность, коэффициент объединения, коэффициент разветвления, передаточную характеристику и ряд других. В некоторых случаях задается максимальная частота переключения.

1. Мощность потребления. В данном случае используют среднюю мощность потребления схемы, которая получается путем усреднения мгновенной мощности за достаточно большой промежуток времени. В большинстве случаев время переключения составляет небольшую часть полного времени работы схемы. При этом среднюю мощность определяют, учитывая только статические состояния, несмотря на то что мощность переключения превышает их:

, (17.1)

, (17.1)

где  и

и  – мощности потребления в состоянии «1» и «0».

– мощности потребления в состоянии «1» и «0».

Для схем, выполненных на полевых транзисторах с изолированным затвором, мощность переключения может в десятки раз превышать мощность потребления. Для них используют оценку средней мощности при максимально допустимой частоте переключения.

Для одной интегральной схемы мощность потребления на один корпус колеблется от долей до сотен милливатт.

2. Уровни выходных напряжений  ,

,  . Эти параметры для потенциальных элементов, у которых сигнал «1» более положителен, чем сигнал «0», показывают следующее: элемент считается годным, если при допустимой нагрузке и в нормированных условиях эксплуатации выходной сигнал «1» у него был не менее

. Эти параметры для потенциальных элементов, у которых сигнал «1» более положителен, чем сигнал «0», показывают следующее: элемент считается годным, если при допустимой нагрузке и в нормированных условиях эксплуатации выходной сигнал «1» у него был не менее  , а сигнал «0» – не более

, а сигнал «0» – не более

. Для ИС эти уровни составляют от долей до единиц вольт (

. Для ИС эти уровни составляют от долей до единиц вольт (  и

и  ).

).

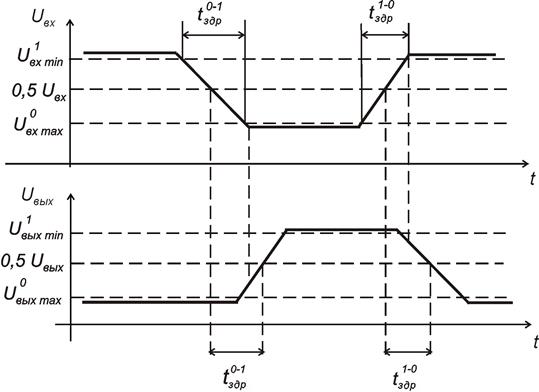

3. Время задержки распространения сигнала  и

и  . Этот параметр определяет быстродействие схем и обычно задается в виде задержки распространения сигналов, представляющих собой интервал времени между сменой уровней входного и выходного сигналов. Для ИС чаще всего применяют метод отсчета по уровню 0,5 (рис.17.3.1). Здесь показаны времена нарастания

. Этот параметр определяет быстродействие схем и обычно задается в виде задержки распространения сигналов, представляющих собой интервал времени между сменой уровней входного и выходного сигналов. Для ИС чаще всего применяют метод отсчета по уровню 0,5 (рис.17.3.1). Здесь показаны времена нарастания  и спада

и спада  .

.

Рис. 17.3

В зависимости от типа ИС времена задержки могут составить от единиц (иногда долей) до сотен наносекунд.

Среднее время задержки определяют следующим образом:

. (17.2)

. (17.2)

Среднее время задержки определяется временем прохождения сигнала через одну микросхему в устройстве. При определении средней задержки в качестве границ временных интервалов обычно берут точки на фронтах, соответствующие половине перепада напряжения, или точки, соответствующие уровням 0,1 и 0,9 этого перепада (рис. 3).

По среднему времени задержки ИС делятся на:

сверхбыстродействующие tзад ср < 5 нс;

быстродействующие 5 нс < tзад ср < 10 нс.

среднего быстродействия 10 нс < tзад ср < 100 нс;

низкого быстродействия tзад ср > 100 нс.

4. Входные токи  ,

,  . Эти параметры определяют нагрузку со стороны схемы на источник сигналов.

. Эти параметры определяют нагрузку со стороны схемы на источник сигналов.

В некоторых случаях схемы потребляют ток по входу, а в других случаях отдают его. Схемы ТТЛ при подаче на вход «0» – отдают ток по входу, а при подаче на вход «1» потребляют его. Наименьшие токи по входу имеют микросхемы на полевых транзисторах, наибольшие – элементы ЭСЛ типа (до единиц миллиампер).

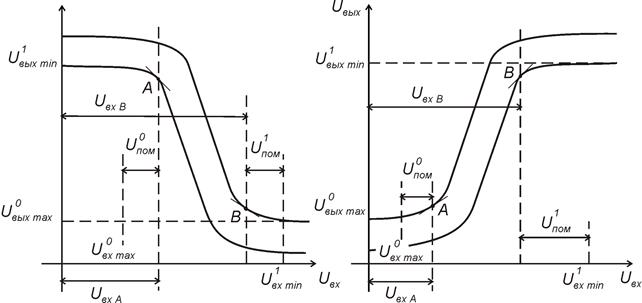

5. Статическая помехозащищенность  . Она характеризуется наибольшим значением напряжения помехи, воздействующей на вход ИС и не вызывающей ее ложного срабатывания. Различают помехоустойчивость по уровню «0» (

. Она характеризуется наибольшим значением напряжения помехи, воздействующей на вход ИС и не вызывающей ее ложного срабатывания. Различают помехоустойчивость по уровню «0» (

) и по уровню «1» (

) и по уровню «1» (  ). Значения

). Значения  и

и  определяются из анализа передаточных характеристик, которые имеют разброс вследствие разброса элементов, входящих в ИС. Поэтому передаточная характеристика представляет не одну кривую, а некоторую пространственную область (рис. 17.4, а – для инвертирующего элемента, рис. 17.4 б – для неинвертирующего).

определяются из анализа передаточных характеристик, которые имеют разброс вследствие разброса элементов, входящих в ИС. Поэтому передаточная характеристика представляет не одну кривую, а некоторую пространственную область (рис. 17.4, а – для инвертирующего элемента, рис. 17.4 б – для неинвертирующего).

а б

Рис. 17.4

Помехоустойчивость  определяется как разность между входным напряжением в точке А, соответствующим перегибу передаточной характеристики, и входным напряжением, соответствующим максимальному уровню логического «0»:

определяется как разность между входным напряжением в точке А, соответствующим перегибу передаточной характеристики, и входным напряжением, соответствующим максимальному уровню логического «0»:  (рис. 17.2, а, б).

(рис. 17.2, а, б).

Помехоустойчивость  находится как разность между напряжением минимального уровня логической «1» и напряжением, соответствующим точке перегиба передаточной характеристики:

находится как разность между напряжением минимального уровня логической «1» и напряжением, соответствующим точке перегиба передаточной характеристики:  .

.

6. Динамическая помехоустойчивость определяется длительностью, амплитудой и формой сигнала помехи, а также статической помехоустойчивостью ИС. Динамическая помехоустойчивость определяется с помощью запоминающего элемента – триггера путем изменения амплитуды и длительности импульсных помех, воздействующих на вход триггера. Критической считается такая длительность помех, при которой амплитуда импульса равна уровню статической помехоустойчивости. Динамическая помехоустойчивость в ТУ на ИС не приводится.

7. Коэффициент объединения по входу характеризует максимальное число входов, при котором еще реализуется заданная логическая функция. Большинство ИС имеет  . Для увеличения коэффициента объединения по входу предусматривают специальные входы для подключения расширителя, который обеспечивает увеличение коэффициента объединения по входу до 10 и более.

. Для увеличения коэффициента объединения по входу предусматривают специальные входы для подключения расширителя, который обеспечивает увеличение коэффициента объединения по входу до 10 и более.

8. Коэффициент разветвления по выходу или нагрузочная способность определяет максимальное число входов других ИС, которое может быть подключено к выходу данной ИС без нарушения ее работоспособности. Однако увеличение числа нагрузок уменьшает быстродействие, ухудшает помехоустойчивость и приводит к увеличению потребляемой мощности. Обычно  . Подключение буферных элементов позволяет получить

. Подключение буферных элементов позволяет получить  .

.

9. Коэффициент объединения по выходу определяет число однотипных микросхем, которые можно объединить выходами для создания дополнительной (монтажной) функции «ИЛИ». Объединение по выходу (т.е. непосредственное соединение выходов нескольких микросхем) допускают логические элементы не всех серий. Объединение по выходу увеличивает потребляемую мощность и уменьшает быстродействие.

ПомехоустойчивостьUп макс – наибольшее значение напряжения на входе микросхемы, при котором еще не происходит изменения уровней выходного напряжения. Помехоустойчивость определяется работоспособностью логического элемента при наличии различных помех, действующих на входе ИМС наряду с полезным сигналом. Помехи могут возникать как в самих логических схемах, так и наводиться от посторонних устройств.

Помехи бывают статические и динамические. Под статическими понимают помехи, длительность которых значительно превышает длительность переходных процессов в логических элементах. К импульсной (динамической) помехе относятся кратковременные импульсы, длительность которых соизмерима с длительностью переходных процессов в логических элементах.

По статической помехоустойчивости логические элементы условно можно разделить на элементы:

с низкой помехоустойчивостью Uп ст = 0,2…0,4 В;

со средней помехоустойчивостью Uп ст = 0,4…0,8 В;

с высокой помехоустойчивостью Uп ст > 0,8 В.

Импульсная помехоустойчивость всегда выше статической. Это вызвано тем, что при коротком импульсе помехи паразитные емкости в логическом элементе не успевают перезарядиться до пороговых уровней переключения микросхемы.

По потребляемой мощности ИМС делятся на:

мощные 25 £ Рср £ 250 мВт (ЭСЛ-схемы);

средней мощности 3 £ Рср £ 25 мВт (ТТЛ-схемы);

маломощные 0,3 £ Рср £ 3 мВт;

микромощные 1 £ Рср £ 300 мкВт (КМОП-схемы);

нановаттные Рср < 1 мкВт (интегральная инжекционная логика).

Потребляемая мощность зависит от напряжения источника питания Uип. Напряжение Uип должно соответствовать одному из значений стандартного ряда напряжений питания: 1,2; 1,6; 2,0; 2,4; 3,0; 4,0; 5,0; 6,3; 9,0; 12,6 В. Для цифровых микросхем на биполярных транзисторах типовые значения Uип составляют 2…5 В, для схем на МДП-транзисторах 5…9 В.

Логические элементы описываются следующими статическими характеристиками:

1. Передаточная характеристика – зависимость выходного напряжения от входного Uвых = f(Uвх), подаваемого на один из входов (рис. 17.5). Она определяется при заданном количестве нагрузок на выходе логического элемента при подаче напряжения на один из входов, на остальные подаются уровни "1" или "0".

2. Входная характеристика – зависимость входного тока от входного напряжения Iвх = f(Uвх) (рис.17.6). Снимается для одного из входов, при заданном количестве нагрузок на выходе, на остальные входы подаются уровни логического "0" или "1" в зависимости от логической функции выполняемой элементом.

Рис. 17.5 Рис. 17.6 Рис. 17.7

3. Выходная характеристика – зависимость выходного тока от выходного напряжения Iвых = f(Uвых) (рис. 17.7). Может быть определена: при низком выходном уровне  и при высоком выходном уровне

и при высоком выходном уровне  .

.

Тема 18. Триггеры

Триггеры представляют собой импульсные электронные устройства, которые могут находиться в одном из двух устойчивых состояний равновесия неопределенно долго до подачи очередного переключающего сигнала и способны скачком переключаться из одного состояния равновесия в другое под действием внешнего сигнала. Триггеры обычно имеют два выхода: основной (прямой) Ơ и инверсный Ỡ. В статических состояниях значения напряжений на выходах Ơ и Ỡ значительно отличаются и в логических устройствах соответствуют уровням логической единицы и логического нуля.

На рис.18.1. приведены два варианта выполнения схемы транзисторного триггера. Резисторы R1 и R2 передают скачки напряжения с коллектора одного транзистора на базу другого. Для обеспечения более устойчивого опрокидывания схемы эти резисторы шунтируются конденсаторами С1 и С2, ёмкость которых превосходит ёмкость эмиттерного перехода, и составляет обычно 200...500 пФ. Источник смещения Eб используется для надежного запирания одного из транзисторов.

|

Рис.18.1.Схемы триггеров с отдельным источником смещения (а) и с автоматическим смещением (б).

Наиболее часто схема выполняется симметричной, для чего выбирают RК1=RК2=RК, R1=R2=R, Rб1=Rб2=Rб, С1=С2=С, а транзисторы VT1 и VT2 с идентичными параметрами.

Рассмотрим процессы, протекающие в симметричной схеме триггера. При подключении источника питания через оба триода могут протекать равные токи IК1 и IК1, однако такое состояние схемы не является устойчивым, и достаточно небольшого изменения одного из этих токов, чтобы вся схема вышла из равновесия, и тогда вследствие развивающегося в ней лавинообразного процесса за весьма короткое время один из транзисторов откроется по обоим переходам и перейдет в насыщенное состояние, а другой транзистор окажется в запертом состоянии. Новое опрокидывание произойдет лишь с приходом запускающего импульса.

Потенциал коллектора запертого транзистора близок к -Ек. Поскольку сопротивление находящегося в насыщенном состоянии транзистора значительно меньше сопротивления резистора RК, то потенциал коллектора открытого транзистора

UК отп = - EК + IКН RК ≈ 0 (18.1)

Определим условия, при обеспечении которых один из транзисторов триггера надежно заперт, в то время как другой транзистор находится в насыщенном состоянии. Потенциал базы запертого транзистора Uб определяется величиной напряжения источника смещения Еб и неуправляемого тока коллекторного перехода Iко, который, проходя по цепи база - коллектор запертого транзистора, создает падение напряжения на резисторе Rб, приложенное отрицательным полюсом к базе транзистора. Поэтому для надежного запирания транзистора необходимо, чтобы при максимальном токе IкоМАХ выполнялось условие

Еб ≥ IкоМАХ Rб

при котором база относительно эмиттера имеет положительный потенциал.

Для надежного насыщения нужно обеспечить ток базы

Iб ≥ Iбн = Iкн / β (18.2)

где Iбн - ток базы транзистора, соответствующий току насыщения коллектора Iкн, а β –коэффициент усиления транзистора по току в схеме общем эмиттером.

Ток базы отпертого транзистора Iб имеет две составляющие. Одна из них Iб‘ создается источником Eб и проходит через резистор Rб и открытый переход база-эмиттер, так что

Iб‘ = Eб / Rб, (18.3)

или, с учетом знака равенстве в предпоследнем соотношении,

Iб‘ = (IкоМАХ / Rб) Rб = IкоМАХ.

Вторая составляющая Iб” проходит от + ЕК через тот же переход в обратном направлении и резистор R1=R2=R к коллектору запертого транзистора, имеющего относительно корпуса потенциал – (ЕК - Iко Rк) поэтому абсолютная величина этого тока

Iб” = (ЕК - IкоМАХ Rк) / R (18.4)

Подставив значения Iкн = ЕК / Rк и Iб = Iб’ - Iб”, получим условие насыщения:

(18.5)

откуда

(18.6)

Чтобы не вводить в схему триггера специальный источник смещения Eб, используют цепочку автоматического смещения RЭСЭ (рис.18.1.б). Ёмкость СЭ выбирают обычно в пределах 1000...5000 пФ, а величина сопротивления резистора RЭ рассчитывается по соотношению

(18.7)

При этом сопротивление резистора R для обеспечения насыщенного состояния транзистора должно быть

(18.8)

В рассматриваемой схеме триггера потенциал эмиттера UЭ через насыщенный транзистор передаётся его коллектору. И вследствие этого потенциал коллектора изменяется в процессе работы триггера приблизительно от – Eк (транзистор закрыт) до - UЭ (транзистор открыт). Амплитуда формируемого импульса

Uвых = Eк - UЭ

Для обеспечения требуемой амплитуды выходных импульсов напряжение источника питания должно составлять величину

Eк = (1,1..1,2) Uвых + UЭ. (18.9)

На работу триггера существенно влияет нагрузка Rн. Чтобы свести к минимуму влияние нагрузки, стараются уменьшить величину сопротивления резистора связи.

Для переключения триггера из одного состояния в другое на базы (или коллекторы) транзисторов подают запускающие импульсы. Различают два режима запуска триггеров - раздельный и счетный.

Режим раздельного запуска может осуществляться двумя способами: при первом - триггер переключается импульсами чередующейся полярности, поступающими, например, на базу одного из транзисторов, а при втором - импульсами одной полярности, поступающими поочередно то на один, то на другой транзистор.

При счетном запуске запускающие импульсы одной полярности поступают сразу на оба транзистора. В приведенной на рис.18.2 схеме триггера положительные импульсы через диоды VD1 и VD2 поступают одновременно на базы обоих транзисторов.

Если в исходном состоянии транзистор VT1 был закрыт, то под действием запускающего импульса положительной полярности закрывается си транзистор VТ2. Тайм образом, пока действует входной сигнал, оба транзистора находятся в закрытом состоянии. По окончании действия запускающего импульса триггер должен обязательно изменить свое состояние, т.е. транзистор VT2 должен закрыться, а транзистор VT1 – открыться.

. Если бы отсутствовали ускоряющие конденсаторы, процесс переключения триггера после окончания входного импульса мог бы развиваться в любом направлении, т.е. возможным был бы сбой триггера.

|

Рис.18.2. Схема триггера с раздельным и счетным запусками (а) и временные диаграммы его работы при различиях режимах запуска (б)

Наличие ускоряющих конденсаторов приводит к тому, что после окончания входного импульса (если он достаточно короткий) симметрия схемы нарушается, так как конденсатор С1 оказывается заряженным почти до напряжения источника питания, а конденсатор С2 почти полностью разряжен. За время действия входного импульса эти напряжения изменяются незначительно. Поэтому в первый момент после окончания запускающего импульса, когда оба транзистора еще находятся в закрытом состоянии, напряжение на конденсаторе C1 направлено встречно напряжению питания и ток через этот конденсатор в базу транзистора VT2 не поступает. В то же время напряжение на конденсаторе С2 хоть и направлено также встречно напряжению питания, но значительно меньше его. Поэтому в базу транзистора VT1 начинает течь ток от источника питания. Это и приводит к открыванию транзистора VT1, что в свою очередь, вызывает разрядный ток от конденсатора C1, поддерживающий закрытое состояние транзистора VT2. В результате чего триггер переходит в противоположное исходному состояние. С приходом следующего импульса триггер перебрасывается в обратном направлении.

Таким образом, конденсаторы C1 и С2 выполняют роль элементов внутренней памяти триггера, запоминая его предыдущее состояние. Вот почему длительность запускающего импульса должна быть небольшой, так как в ином случае за время его действия начальные напряжения на конденсаторах C1 и С2 могут значительно измениться, и окажется возможным сбой триггера.

Из диаграммы выходного напряжения триггера при счетном запуске видно, что частота переключения триггера вдвое меньше частоты следования входных импульсов. Таким образом, триггер со счетным запуском можно использовать в качестве бинарного делителя частоты следования импульсов.

В отличие от раздельного запуска, режим счетного запуска критичен к длительности и амплитуде запускающих импульсов.

Дата добавления: 2020-10-14; просмотров: 695;