Загальна структура та класифікація тригерів

Виходячи iз загальних принципів побудови ПП, узагальнюючу структуру тригера можна зобразити з двох частин - комбінаційної схеми (КС) і елементарного двостанового запам’ятовувача, тобто власне тригера (див рис. 4.2). КС, на яку надходять ззовні або подаютьея по колах додатного зворотного зв’язку різні сигнали, виконує функції керування роботою та формування властивостей всієї схеми тригера. Певна комбінація взаємодії цих входів i визначає відмінність функціонування тригера, а отже, і його тип.

За характером дії вхідних сигналів входи тригера розрізняють: інформаційні і керуючі, які залежно від виконуваної ролі можуть бути дозволяючі та синхронізуючі.

На інформаційні входи тригера подають двійкову інформацію (Хі), яку він має зафіксувати у вигляді нуля або одиниці. На керуючі входи подаються сигнали, які виконують допоміжну функцію – саме з їх допомогою у потрібний момент можна виконати запис чи перезапис та зчитування записаної інформації. Зокрема, на виконавчі входи тригера подаються тактові або синхронізуючі сигнали, які встановлюють у КС момент запису чи зчитування, тобто перемикання тригера

Рис. 4.45 Узагальнююча структурна схема тригера

. Таким чином, встановлення або скидання тригера здійснюється при певній взаємодії вхідних сигналів, які саме роблять його активним або пасивним.

Нижче наведений перелік можливих входів умовного тригера за їх функціональним призначенням.

Інформаційиі входи:

R,K – входи окремого встановлення (скидання) тригера в стан 0 (R - з англ. Reset - скидати, очищувати; K - з aнгл. Kill -раптово вимикати), у даному випадку iз стану 1 в 0;

S,J – входи окремого встановлення тригера у стан 1 (S - з англ. Set – установлювати; J - з англ. Jerk– раптово вмикати), в даному випадку iз стану 0 в 1;

D – вхід встановлення тригера у cтан 1/0 (D - з англ. Delay – затримка);

T – вхід перемикання/встановлення /1/ i скидання /0/ тригера, або лічильний вхід (T - з англ. Toggle – перевертати).

Керуючі входи:

V,E - входи дозволу запису або зчитування iнформації ( V — з англ. Valve – клапан; Е - з aнгл. Епаblе – дозвіл);

С - виконавчий вхід для тактових чи синхронізуючих iмпульсів (С - з aнгл. Сlоск – годинник).

У iнтегральному виконанні тригер - це конструктивно єдиний функціональний вузол, тобто мікросхема, яка може бути виготовлена за певною технологією (ТТЛ, КMОН…). З точки зору схемотехніки тригер – це електронна схема, шо має два стійких стани (високий або низький рівень), які встановлюються при подачі відповідної комбінації сигналів інформації на керуючі входи схеми і які після закінчення дії цих сигналів зберігаються протягом заданого часу.

Тип тригера визначається функціональною залежністю між сигналом нa виході і сигналами на входах. Ця залежність може бути подана різними способами: аналітичнo, графічно, часовими діаграмами, таблицями станів.

У iнтегральному виконанні в основному зустрічаються серед одновходових D- i T-тригери, серед двовходових – RS- і JК -тригери, а серед універсальних - JК(RS) -тригер. Інші типи тригерів, яких досить багато, можуть бути побудовані у базисі різних ЛЕ.

За способом запису iнформації, що характеризує часову діаграму роботи тригера i, отже, визначає хід процесу запису iнформації у тригер, розрізняють дві групи тригерів: асинхронні та синхронні.

Відмінною особливістю асинхронних тригерів е те, що запис iнформації у них здійснюється безпосередньо з надходженням інформаційного сигналу, що подано на інформаційний вхід тригера. У синхронного тригерa, крім iнформаційного, є так званий синхронізуючий вхід для тактових iмпульсів, які дають дозвіл на запис iнформації. Асинхронні тригери застосовуються у колах керування, а також як складова частина більш складних тригерів. Синхронні тригери реагують на iнформаційні сигнали тільки при наявності синхронізуючих сигналів. Вони мають найбільше застосування у ЦТ, бо особливість їх роботи забезпечує відсутність негативних явищ у сигнальних колах. В загальному класифікувати тригери можна за трьома найважливішими ознаками: логікою функціонування; способом запису інформації; типом двостанового запам’ятовувача iнформації [1]:

Рис. 4.46 Класифікація тригерів

Розрізняють два типи цифрових сигналів, часові параметри яких здатні змінити стан тригера: потенціальні та імпульсні (рис. 4.4). Потенціальні сигнали Х змінюють стан тригера при наявності або відсутності рівня напруги X = 0 або Х = 1. Імпульсні - при зміні потенціального сигналу /dХ = 1 тільки при зміні X з одиниці на нуль,  , навпаки, при зміні Х з нуля на одиницю,

, навпаки, при зміні Х з нуля на одиницю,  = 1 - при будь-якій зміні X. Показані нa рис. 4.4 часові параметри цифрових сигналів ідеальні: фронт, зріз та тривалість цих сигналів нескінченно малі.

= 1 - при будь-якій зміні X. Показані нa рис. 4.4 часові параметри цифрових сигналів ідеальні: фронт, зріз та тривалість цих сигналів нескінченно малі.

Рис. 4.47 Ілюстрація типиів цифрових сигналів

Відповідно до розглянутих типів цифрових сигналів, що застосовуються для зміни стану тригерів, розрізняють входи статичні, які керовані потенціальними сигналами, та динамічні, які керовані iмпульсними сигналами, тобто перепадами потенціалів (фронтом чи зрізом).

Залежно від типу застосованого двостанового запам’ятовувача iнформації тригери поділяють на класи: статичні, динамічні та статично-динамічні.

Динамічні тригери в основному будуються на МДH-транзисторaх. Особливість їх у тому, що вони являють собою замкнене коло, в якому циркулюють iмпульси, якщо тригер знаходиться у стані "1". На відміну від динамічних тригерів, параметри яких періодично змінюються, у статичних та статично-динамічних тригерах параметри в одному з двох стійких. станах (1 або 0) незмінні.

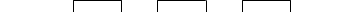

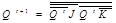

Тригери позначають так, як показано на рис. 4.5.а,б,* де T – одноступеневий, а TT - двоступеневий тригери. При цьому  -тригер, що на рис. 4.5.а, має статичні входи R i S, а універсальний двоступеневий JK -тригер, крім багатовходових інформаційних входів &J і &K, має динамічний синхронізуючий вхід С типу dX = 1, тобто dС = 1, при цьому для позначення динамічного входу типу dC = 1 застосовують додатний нахил риски.

-тригер, що на рис. 4.5.а, має статичні входи R i S, а універсальний двоступеневий JK -тригер, крім багатовходових інформаційних входів &J і &K, має динамічний синхронізуючий вхід С типу dX = 1, тобто dС = 1, при цьому для позначення динамічного входу типу dC = 1 застосовують додатний нахил риски.

Рис. 4.48 Позначення тригерів

Завдяки своїм значним функціональним можливостям тригери належать до найпоширеніших цифрових пристроїв..

Рiзновиди тригерів

Функціональна структура тригера як двостанового запам’ятовувача бінарних сигналів (див. рис.4.2) досить складна, що закономірно, адже крім запам’ятовування одного біта інформації тригер забезпечує його запис і зчитування у потрібний момент часу. Можливість зміни структури обох частин тригера (комбінаційної i власне тригера) та способів пiд’єднання зворотних зв’язкsв зумовлює таку їх різноманітність.

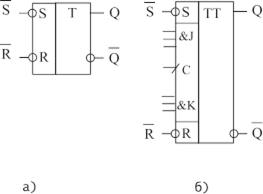

Серед різних структур можна виділити спільну і найпростішу структуру тригера, яку умовно назвемо базовою. Такою базовою схемою двостанового запам’ятовувача є асинхронний RS- або  - тригер, бо на його основі можна будувати практично всі відомі типи тригерів. На рис. 4.6.а,б зображені базові схеми RS- і

- тригер, бо на його основі можна будувати практично всі відомі типи тригерів. На рис. 4.6.а,б зображені базові схеми RS- і  -тригера, що виконані у базисі ЛЕ відповідно двох елементів Пірса (2АБО-НЕ) і двох елементів Шефера (2І-НЕ). Принцип дії цих тригерів пояснюється спрощеними таблицями станів.

-тригера, що виконані у базисі ЛЕ відповідно двох елементів Пірса (2АБО-НЕ) і двох елементів Шефера (2І-НЕ). Принцип дії цих тригерів пояснюється спрощеними таблицями станів.

Таблиця 4.17 Стани RS- і  -тригерів

-тригерів

Рис. 4.49 Базові схеми RS тригерів

Особливість функціонування асинхронних тригерів полягає у тому, що вони змінюють свій стан тільки в момент дії активних інформаційних сигналів. Зокрема, асинхронний RS-тригер, як видно з таблиці його переходів, при R = S = 0 зберігає свій попередній стан Qt, (0 або 1), а при активних входах S=1 aбо R = 1 на його виходах, встановлюється відповідно стан Qt+1 = 1 (Ōt+1 = 0) або навпаки. При R=S=1, тобто при одночасній дії на обидвох входах сигналів встановлення в "1" i скидання в "0", стан тригера стає непередбачуваним. Така комбінація вхідних сигналів для RS-тригерв вважається забороненою ( “~” в табл.4.3), a тому її треба уникати, щоб запобігти можливих збоїв. Для асинхронного  -тригера (див. рис. 4.6,б) розглянута характеристика буде справедливою для випадку інверсних ситуацій. Щоб переконатись у справедливості функціонування обох тригерів за їх таблицями переходів, доцільно самостійно прослідкувати всі логічні зміни сигналів не входах i виходах.

-тригера (див. рис. 4.6,б) розглянута характеристика буде справедливою для випадку інверсних ситуацій. Щоб переконатись у справедливості функціонування обох тригерів за їх таблицями переходів, доцільно самостійно прослідкувати всі логічні зміни сигналів не входах i виходах.

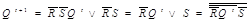

З таблиць переходів RS- або  -тригера можна одержати функцію переходів для RS і

-тригера можна одержати функцію переходів для RS і  -тригера і ця функція переходів матиме однаковий вигляд:

-тригера і ця функція переходів матиме однаковий вигляд:

( 4.0 )

( 4.0 )

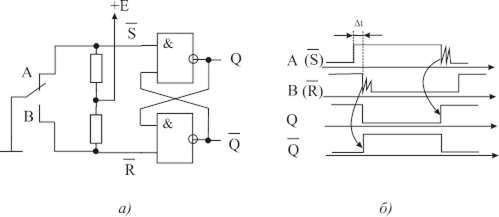

Одним з практичних застосувань асинхронного RS -тригера є ліквідація з його допомогою явища електричного "брязкоту" (вібрації) механічних контактів реле, кнопок, тумблерів, яке викликане ударом під час перемикання. Це негативне явище може викликати небажане спрацювання наступних ЛЕ схеми і привести до збою цифрової системи. Особливо це стосується схем приймання зовнішніх сигналів, наприклад, з клавіатури, кнопок запуску тошо, тобто сигналів, які утворені механічними перемиканнями з високого рівня у низький або навпаки. Вони мають забезпечувати надійний одноразовий перехід пристрою у потрібний стан при першому натисканні механічного перемикача .

На рис.4.7 показана схема придушення явища брязкоту контактів, пояснення роботи якого ілюструють часові діаграми. З допомогою асинхронного  -тригера усуваються численні імпульси "деренчання" і виробляється тільки один iмпульс з моменту натиснення кнопки чи переводу перемикача.

-тригера усуваються численні імпульси "деренчання" і виробляється тільки один iмпульс з моменту натиснення кнопки чи переводу перемикача.

Рис. 4.50 Схема придушення явища брязкоту механічних контактів

Це пояснюється тим (див. рис. 4.7,б), що при зміні положення А перемикача у положення В або навпаки вхід  або

або  протягом часу прольоту контакту ще має високий рівень »E i тригер зберігає попередній стан. Однак при першому дотику рухомого контакту до нового положення тригер під дією активного сигналу перейде у новий стан, усуваючи таким чином небажаний перехідний процес.

протягом часу прольоту контакту ще має високий рівень »E i тригер зберігає попередній стан. Однак при першому дотику рухомого контакту до нового положення тригер під дією активного сигналу перейде у новий стан, усуваючи таким чином небажаний перехідний процес.

На відмiну від асинхронних у синхронних (або тaктових) тригерів стан змінюється при наявності разом з iнформаційними сигналами синхронізуючих сигналів. Будь-який асинхронний тригер можна перетворити на синхронний, якщо доповнити його виконавчим входом С для синхросигнaлів. Останній легко утворити об’єднанням незайнятих входів інвертуючих схем збігу 2І-НЕ тaк, як це подано у табл. 4.4. Тоді лише при С=1 тригер реагуватиме не комбінацію інформаційних сигналів, а при С=0 залишиться у попередньому стані. Синхронні тригери незалежно від функціональних відмінностей за принципом побудови внутрішньої структури можуть бути одно- або двоступеневі. Одноступеневі тригериможуть мати лише статичне керування, бо приймання і зчитування інформації у них відбуваються одночасно при дії активного сигналу синхронізації, тобто при С = 1. Недоліком RS-тригера є наявність заборонених рівнів вхідних сигналів при R = S = 1, що може призвести до неоднозначної його роботи. Такої ситуації можна запобігти, якщо виходи  i

i  -тригера з’єднати із входами відповідно R і S так, як це показано на рисунку табл. 4.4. Тоді така схема при R º K і S º J перетворюється на схему JK-тригера, у якої відсутня заборонена комбінація вхідних сигналів при J=K=1, коли вихідний сигнал JK -тригера стає інверсією попереднього стану.

-тригера з’єднати із входами відповідно R і S так, як це показано на рисунку табл. 4.4. Тоді така схема при R º K і S º J перетворюється на схему JK-тригера, у якої відсутня заборонена комбінація вхідних сигналів при J=K=1, коли вихідний сигнал JK -тригера стає інверсією попереднього стану.

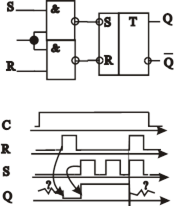

Таблиця 4.18 Синхронні тригери

| Тип тригера | Спрощена таблиця станів | Функція переходів синхронний/асинх. | Схема тригера та часові діаграми | ||

| RS-тригер синхрон. C=var Асинхронний С=1 | S | R | Qt+1 |

|

|

| Qt ~ | |||||

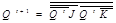

| JK-тригер синхрон. C=var Асинхронний С=1 | J | K | Qt+1 |

|

|

| Qt Qt |

При інших комбінаціях вхідних сигналів асинхронний JK -тригер працює як RS -тригер. Роботу JK -тригера ілюструє табл. 4.4. Комбінаційна частина у послідовнісних автоматах, що побудована на ЛЕ, має негативну властивість утворювати "гонки", які можуть ініціювати короткочасні завади типу "голки". Причиною появи такої завади. Причина цього – різниця затримок поширення сигналів внаслідок різного числа ЛЕ паралельних каналів. Для візуального виявлення цього явища зручно застосовувати двоканальний осцилограф, що дає можливість бачити одночасно зсунуті сигнали і утворену ними заваду.

Усунути явище "гонок" у колах ЛЕ можна за рахунок зовнішнього часового керування (стробування) роботою схеми у такі моменти часу, коли одночасна поява фронтів чи зрізів імпульсів малоймовірна або неможлива. Часове стробування забезпечується синхронізуючими тактовими імпульсами, які подаються на додатковий керуючий вхід тригера. Такий тригер з асинхронного перетворюється у синхронний.

Відсутність заборонених станів у JK-тригера призвело до того, що цей тригер став oсновою для побудови цілого ряду синхронних тригерів в інтегральному виконанні. Найбільше практичне застосування в інтегральній схемотехніці дістали синхронні JK-тригери, які можуть бути одноступеневими, тобто iз статичним керуванням (або синхронізовані фронтом чи зрізом). Одноступеневий синхронний JK-тригер будується за аналогією з синхронним RS-тригером. Він також має додатковий вхід для синхросигнaлiв, який утворений з'єднанням двох окремих входів схем збігу. При С = 1 синхронний JK-тригер перетворюється на асинхронний.

На базі одноступеневих синхронних JK-тригерiв можна простою комутацією зовнішніх виводів будувати різні типи тригерів, наприклад, такі, як D i T -тригери.

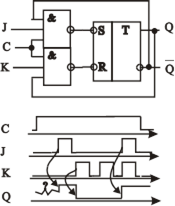

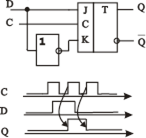

Розглянемо характерні особливості функціонування та призначення D i Т‑тригерів, шо побудовані на базі одноступеневого JK-тригера (табл. 4.5). Призначення D-тригерiв - це затримка нa один період (такт) синхронізуючих імпульсів інформації, що надійшли на вхід D. У цифровій схемотехніці застосовують D-тригери, які синхронізовані рівнем С (такий D -тригер називають тригером-защіпкою (від англ. Latch) тa D-тригери, які синхронізовані фронтом. В обох випадках D-тригер можна побудувати на базі синхронного або асинхронного JK-тригера, якщо прийняти JºD і  . Як видно з табл. 4.5. для побудови D-тригера на базі JK -тригера досить вхід J з'єднати через iнвертор із входом K, що таким чином утворить вхід D. Особливістю D -тригера є зміна стану лише у момент переходу тактового сигналу на вході С з нуля в одиницю, тобто у момент дії переднього фронту синхросигналу D-тригер не сприймає зміну на вході D як при С = 0, так і при С = 1. Така властивість D-тригера зумовлює його високу завадостійкість за інформаційним входом D. Особливість роботи T-тригера, який ще називають лічильним оскільки вiн є основним елементом цифрових лічильників, полягає в тому, що стан його змінюється на протилежний при надходженні сигналу Т=1 і зберігається незмінним при T = 0. Згідно з табл. 4.5 стан T-тригера при J=K=1 змінюється на протилежний Qt+1=Qt, при надходженні кожного синхроімпульса. У цьому випадку JK-тригер при подачі на вхід С імпульсів функціонує як Т-тригер. Функція переходів Т-тригера отримується при J=K=Т (див. табл. 4.5).

. Як видно з табл. 4.5. для побудови D-тригера на базі JK -тригера досить вхід J з'єднати через iнвертор із входом K, що таким чином утворить вхід D. Особливістю D -тригера є зміна стану лише у момент переходу тактового сигналу на вході С з нуля в одиницю, тобто у момент дії переднього фронту синхросигналу D-тригер не сприймає зміну на вході D як при С = 0, так і при С = 1. Така властивість D-тригера зумовлює його високу завадостійкість за інформаційним входом D. Особливість роботи T-тригера, який ще називають лічильним оскільки вiн є основним елементом цифрових лічильників, полягає в тому, що стан його змінюється на протилежний при надходженні сигналу Т=1 і зберігається незмінним при T = 0. Згідно з табл. 4.5 стан T-тригера при J=K=1 змінюється на протилежний Qt+1=Qt, при надходженні кожного синхроімпульса. У цьому випадку JK-тригер при подачі на вхід С імпульсів функціонує як Т-тригер. Функція переходів Т-тригера отримується при J=K=Т (див. табл. 4.5).

Структурний синтез тригерів можна виконати не лише на базі JK-тригера. Широкі функціональні можливості характерні й синхронному D-тригеру. Зокрема, iз синхронного D-тригера легко зробити T-тригер, якшо з’єднати вхід D з виходом  , а вхід С використати як лічильний вхід Т, тобто виконати умову D º

, а вхід С використати як лічильний вхід Т, тобто виконати умову D º  , C=T (див. тaбл. 4.3). Для перетворення синхронного D-тригера на асинхронний RS-тригер потрібно виконання умов CDºS i C

, C=T (див. тaбл. 4.3). Для перетворення синхронного D-тригера на асинхронний RS-тригер потрібно виконання умов CDºS i C  ºR.

ºR.

На відміну від одноступеневих синхронних тригерів, що керовані рівнем або тригерів із статичним керуванням, тригери з динамічним керуванням змінюють свій стан тільки у момент переходу рівня напруги з нуля в одиницю або навпаки. Отже, керуючими сигналами синхронних тригерів з динамічним керуванням є імпульсні сигнали (див.рис.4.4)  або

або  . Тригери цього типу ще називають тригерами з внутрішньою затримкою або двоступеневими синхронними.

. Тригери цього типу ще називають тригерами з внутрішньою затримкою або двоступеневими синхронними.

Основною перевагою двоступеневих синхронних тригерів перед одно-ступеневими є їх внутрішня завадостійкість, яка зумовлена відсутністю порушення стану тригера під час запису інформації, хоча небажана зміна стану тригера можлива також під дією "гонок".

Таблиця 4.19 Синхронні тригери

| Тип тригера | Спрощена таблиця станів | Функція переходів синхронний/асинх. | Схема тригера та часові діаграми | ||

| D-тригер Синхронний C=var Асинхронний С=1 | D | Qt | Qt+1 |

|

|

| JK-тригер Синхронний C=var Асинхронний С=1 | T | Qt+1 |

|

| |

| |||||

|

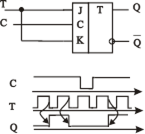

Двоступеневі синхронні тригери (RS-, JK-тригери, тощо) будуються на базі двох послідовно з'єднаних одноступеневих асинхронних або синхронних тригерів, що працюють за принципом "ведучий-ведений", та комбінаційної схеми керування синхронізацією. Такі тригери називають ще MS-тригерами*. Особливість роботи MS-тригерів полягає у тому, що при С=1 здійснюється запис інформації у перший тригер, а при С=0 – передавання інформації з першого тригера в другий та одночасне блокування першого і всіх інших інформаційних входів тригера. Виходами всієї схеми є виходи другого тригера. Отже, дня повного циклу роботи двоступеневого тригера потрібно два перепади синхросигналу. Тому і вважається, що MS-тригер керується імпульсом, а не рівнем напруги.

На рис.4.8.а,б показані схема та часові діаграми двоступеневого синхронного JK-тригерa, який побудовано на базі каскадного з’єднання двох одноступеневих синхронних RS-тригерів та схеми керування на ЛЕ. Причому для першого М-тригера активним сигналом запису є С=1, а для другого S-тригера C=0. Стан першого тригера змінюється у момент переходу фронту синхросигнaлу з нуля в одиницю. Отже, по відношенню до вхідних схем JK‑тригер має прямий динамічний вхід С і при активних сигналах здійснює запис інформації. По відношенню до схеми, що стоїть на його виході, він має інверсний динамічний вхід синхросигнaлу, і його вихідний стан визначається станом другого (веденого) тригера, що керований перепадом (зрізом) С з одиниці в нуль, при якому здійснюється зчитування записаної інформації. Для того щоб новий стан тригера не був логічно залежним від вихідних сигналів та своїх станів і водночас щоб синхроімпульси в часі не перекривалися, тобто щоб їх обидві фази (на запис і зчитування) одночасно не набували значень лог.1, у схемі MS-тригера передбачений пороговий інвертор синхроімпульсів. Останній формує обидві фaзи jM i js синхроімпульсів  і

і  за рахунок спеціально заданих йому логічних порогів спрацювання. В схемі пороґовий iнвертор має нижчий поріг спрацювання Us1 для лог. 1, ніж у M-тригера – отже, він швидше заблокує S-тригер, але вищий Us0 для .лог.0, ніж у M-тригера, – а тому пізніше розблокує S-тригер. Це дозволяє по фронту синхросигналу наперед записати інформацію із входів M -тригера, а разом з тим і MS-тригера при заблокованому М-тригері, а по зрізу - читати записану інформацію з S –тригера, тобто з самого MS-тригера, при заблокованому вході MS-тригера. Таким чином, як ілюструє рис. 4.8.б, завдяки пороговому iнвертору синхроімпульси на лініях обох фаз (

за рахунок спеціально заданих йому логічних порогів спрацювання. В схемі пороґовий iнвертор має нижчий поріг спрацювання Us1 для лог. 1, ніж у M-тригера – отже, він швидше заблокує S-тригер, але вищий Us0 для .лог.0, ніж у M-тригера, – а тому пізніше розблокує S-тригер. Це дозволяє по фронту синхросигналу наперед записати інформацію із входів M -тригера, а разом з тим і MS-тригера при заблокованому М-тригері, а по зрізу - читати записану інформацію з S –тригера, тобто з самого MS-тригера, при заблокованому вході MS-тригера. Таким чином, як ілюструє рис. 4.8.б, завдяки пороговому iнвертору синхроімпульси на лініях обох фаз (  і

і  ) з’являються у різні моменти часу, які взаємно не перекриваються, з проміжками між iмпульсами, що визначаються крутизною фронту і зрізу синхросигналу. Таким чином вдається розділити процеси запису і зчитування інформації, що дуже потрібно для багатьох функціональних пристроїв ЦТ, зокрема для лічильників, у яких одночасно можуть здійснюватись процеси зміни i відліку станів тригерів.

) з’являються у різні моменти часу, які взаємно не перекриваються, з проміжками між iмпульсами, що визначаються крутизною фронту і зрізу синхросигналу. Таким чином вдається розділити процеси запису і зчитування інформації, що дуже потрібно для багатьох функціональних пристроїв ЦТ, зокрема для лічильників, у яких одночасно можуть здійснюватись процеси зміни i відліку станів тригерів.

Рис. 4.51 Структура MS тригера

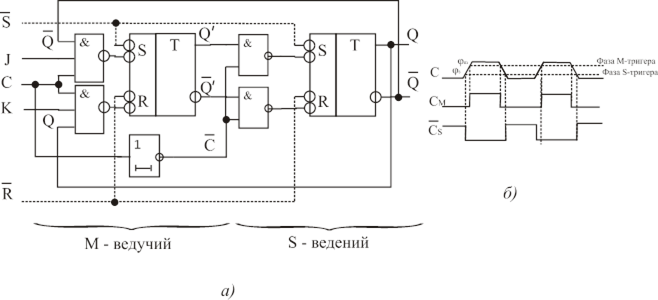

Роботу двоступеневого синхронного; JK-тригера можна пояснити з допомогою часових діаграм, що зображені на рис. 4.9.

Рис. 4.52 Часові діаграми роботи двоступеневого синхронного JK-тригера

При J=K=1 тригер працює у лічильному режимі, тобто як Т-тригер, аналогічно як для випадку одноступеневого JK-тригера (див.табл.4.5). Різниця лише в тому, що у даному випадку зміна стану тригера у лічильному режимі відбувається по зрізу, а не по фронту синхроімпульсів С. Якщо, наприклад, J=0 i K=1 (тобто згідно з табл.4.5 JK -тригер має перейти в стан Qt+1=0), то при надходженні синхроімпульсів стан JK-тригерa перейде в нуль тільки при переході синхросигналу на вході С з одиниці в нуль, бо у цей момент відбувається зміна (або збереження) стану другого S-тригера під дією перепаду C з нуля в одиницю. Отже, запис інформації в JK-тригер здійснюється на першому (при С=1), а зчитування - на другому (при  ) тактах періодa синхроімпульсів. Якщо ситуація на інформаційних входах після другого такту надходження синхроімпульсів не змінилась, то при J¹K¹1 даний тригер знаходиться у режимі зберігання попереднього біту інформації. Тільки при J=K=1 JK-тригер перетворюється на T-тригер (де СºT) i, отже, здатний частоту нaдходження синхроімпульсів поділити на 2 (див. рис. 4.9).

) тактах періодa синхроімпульсів. Якщо ситуація на інформаційних входах після другого такту надходження синхроімпульсів не змінилась, то при J¹K¹1 даний тригер знаходиться у режимі зберігання попереднього біту інформації. Тільки при J=K=1 JK-тригер перетворюється на T-тригер (де СºT) i, отже, здатний частоту нaдходження синхроімпульсів поділити на 2 (див. рис. 4.9).

Таким чином, двоступеневий синхронний JK-тригер змінює свій стан тільки в момент перепадів синхросигналу,a не під дією рівнів, на вході С. Важливою перевагою двоступеневого ,JK-тригера є ще те, що інформаційні входи за період синхроімпульсів, тобто під час завантаження 1 біт інформації, функціонально ізольовані від вхідних кіл. Така своєрідна властивість цього тригера забезпечує стійке перемикання тригера навіть тоді, коли частота синхроімпульсів нестабільна. Завдяки таким властивостям на двоступеневих JK-тригерах можна будувати зaвадостійкі швидкодіючі цифрові пристрої.

У мікросхемотехніці ТТЛ серії 155 (555) щироке застосування має універсальний JK -тригер К155ТВ1. Його відмінність від розглянутого (на. рис. 4.8) лише у наявності потроєних інформаційних входів, що з’еднанi за схемою 1: &J=J1J2J3 i &K=K1K2K3 а також несихронізованих окремих входів  і

і  (на рис.4.8 вони показані пунктирними лініями) для асинхронного встановлення тригера у потрібний стан лог.1 або лог. 0. Під час перемикання тригера з одного стaну в інший під дією сигналів на інформаційних та синхронізуючому входах на входи

(на рис.4.8 вони показані пунктирними лініями) для асинхронного встановлення тригера у потрібний стан лог.1 або лог. 0. Під час перемикання тригера з одного стaну в інший під дією сигналів на інформаційних та синхронізуючому входах на входи  і

і  слід прикладати пасивні рівні лог.1. Наявність потроєних входів &J і &К дозволяє розширити функціональні можливості тригера. Зокрема, кон’юнктивне об’єднання входів, J і K спрощує будову лічильників.

слід прикладати пасивні рівні лог.1. Наявність потроєних входів &J і &К дозволяє розширити функціональні можливості тригера. Зокрема, кон’юнктивне об’єднання входів, J і K спрощує будову лічильників.

Як і у випадку одноступеневого JK-тригера, на базі двоступеневого можна будувати інші схеми тригерів. Шляхом комутації зовнішніх виводів J,K,C,R,S двоступеневий синхронний JK-тригер можна перетворити на тригер, до виконує функції RS-, T-, D-тригерів.

Тригер як двостановий звпам’ятовувач інформації є складовою частиною будь-якого цифрового aвтоматa послідовнісного типу. Тому для синтезу ПП потрібно мати iнформацію про функціонування тригерa для всієї повноти можливих ситуацій на його входах. Крім таблиці станів та функції переходів необхідно знати, що саме зумовило даний стан тригера, тобто які сигнали на входах можуть викликати зміну стану тригера від Qt до Qt+1. Таку інформацію відображає тaк звана таблиця переходів тригера. Кожний тип тригера характеризується своєю таблицею переходів, що наглядно демонструє табл.4.6 для D-,T-,RS-JK-тригерів.

Таблиця 4.20 Таблиці переходів для основних типів тригерів

| Код переходу | D-тригер | Т-тригер | RS-тригер | JK-тригер | ||

| D | T | R | S | J | K | |

| 0 0 0 1 1 0 1 1 | ~ | ~ | ~ ~ | ~ ~ | ||

| Умовні зображення тригерів |

|

|

|

|

У інтегральному виконанні можна зустріти різні типи тригерів у серіях відомих технологій:

· ТТЛ(Ш) - JK-тригери (ТВ1, ТВ9, ТВ10, ТВ11) у серіях К/М/155, К/М/555, КР531, /КР/1533; D-тригери (TM2, ТМ5) у серіях /К/M/555, /КР/1531, 1533;

· ЕЗЛ - JK-тригери (ТВ135) у серіях К500; D-тригери (ТМ130, ТМ131, TM133, TM134) у серіях /K/500, К500М, /К/1500;

· КМОН -JK-тригери (ТВ1) у серіях К561, 564, КР1561; D-тригери (TМ1, TМ2, TМЗ, TМ5) у серіях К561, 564, К176. 1564; RS-тригери (ТР2) у серіях К561,564.

Регістри

Регістром називається послідовнісний пристрій, що призначений для приймання, запам’ятовування, перетворення і передачі двійкової iнформації. Регістри можуть використовуватися також для виконання деяких логічних перетворень. У загальному випадку регістр - це блок тригерів i ЛЕ одного типу, що певним чином з’єднані між собою. Введення /запис/ інформації у регістр i зняття /зчитування/ інформації з нього залежать від способу і характеру цих з’єднань. Тому можливих способів приймання і передачі слів може бути чотири:

· з послідовними входом і виходом - регістр типу SISO (S - від англ. Serial);

· з послідовним входом і паралельним виходом - регістр типу SIРО (Р - від англ. Раrаllel);

· з паралельним входом i послідовним виходом - регістр типу РІSО ;

· з паралельними входом i виходом - регістр типу РІРО;

Регістр типу SISO призначений для послідовного біт за бітом виконання операцій запису і зчитування n-розрядного слова. Такий регістр ще називають регістром зсуву. Регістр типу SІРО завантажується послідовно біт за бітом, а видає записану інформацію одночасно з усіх своїх розрядів за один такт синхросигналу. Приймання інформації у регістрі типу РІSО здійснюється одночасно по всіх розрядах слова за один такт керування, а зчитування - послідовно. Найбільш швидкодіючим очевидно, є регістр РІРО бо і запис, і зчитування слова у нього відбуваються одночасно і незалежно. Такий регістр називають регістром пам’яті.

Розрядність будь-якого регістра визначається числом тригерів, кожний з яких як двостановий запам’ятовувач одного розряду слова відповідає за введення, збереження і виведення-1 біт iнформації. Регістри можуть відрізнятись між собою за кількістю тактів керування, що необхідні для виконання конкретних операцій. Тому за способом тактування розрізняють одно-, дво- або багатотaктні регістри. Для керування однотактним регістром досить однієї послідовності синхросигнaлів, багатотактним - кількох. Операції встановлення регістра у початковий стан, приймання інформації з одного пристрою i передача її в інший пристрій, зсув слова вліво або вправо, реалізуються за допомогою комбінаційної схеми регістра.

Регістри належать до найбільш поширених функціональних вузлів. Крім зберігання інформації, її зсуву тa зчитування, які необхідні для виконання різних арифметичних та логічних операцій над двійковими числами, за допомогою регістрів можна також перетворювати інформацію з одного виду в інший, наприклад, послідовного коду у паралельний або навпаки тощо.

Регістри пам’яті

Цe накопичувальні регістри - пристрої в паралельним записом та зчитуванням слова, типу РІРО. Їх основне призначення – зберігання двійкової інформації невеликого об’єму (не більше 2 байт), що подана у паралельному коді. Регістри пам’яті можуть бути синхронізовані рівнем (дозволом С=1) або фронтом, чи зрізом синхросигналу залежно від типу застосованих тригерiв.

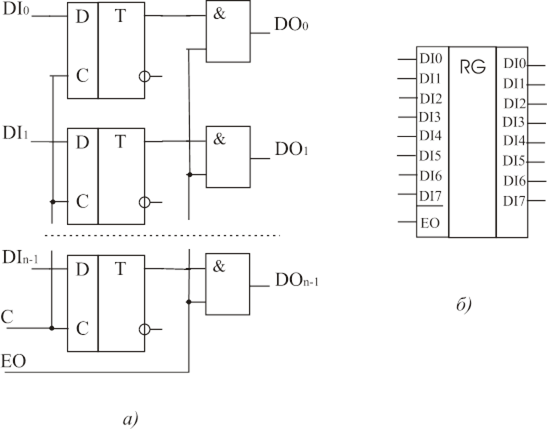

На рис.4.10.а показана схема n-розрядного регістра пам’яті, що побудований на синхронних D-тригерах, та кон’юнкторах на ЛЕ, що виконують функцію збігу. Інформація у вигляді паралельного коду двійкових чисел {DIn-1…DI1,DI0} заноситься по вхідній шині і записується у регістрі тільки при наявності дозволяючого рівня С=1. Зчитування інформації з регістра можливе тільки при наявності на входах схем збігу дозволяючих рівнів, тобто при ЕО=1.

Рис. 4.53 Структура (а) та позначення (б) регістра пам’яті

На рис.4.10.б показане схематичне позначення 8-ми розрядного регістра пам’яті.

У випадку побудови регістра пам’яті на RS -тригерах у схемі потрібно передбачити попереднє "очищення" регістра тобто встановлення всіх тригерів у стан нуль, що здійснюється за допомогою входу скидання R. Попереднє встановлення тригерів в нуль вимагає додаткового часу, то зменшує швидкодію регістра. Для збільшення швидкодії таких регістрів пам'яті застосовують парафазну передачу для перезапису iнформації з регістрa в регістр. Для цього використовують обидва входи RS -тригерів, по яких одночасно подають сигнали  , та

, та  . Розрядність регістрів пвм’ятi нарощується збільшенням потрібного числа тригерів, тактові входи яких приєднують до шини синхронізації С.

. Розрядність регістрів пвм’ятi нарощується збільшенням потрібного числа тригерів, тактові входи яких приєднують до шини синхронізації С.

Регістри зсуву

Роботу регістра зсуву можна спостерігати в деяких мікрокалькуляторах, де при наборі кожної наступної цифри на клавіатурі числа на індикаторі зсуваються вліво. При цьому виявляються характерні властивості регістрів зсуву:

· регістр зсуву, це пристрій, що має часову пам’ять, завдяки чому числа залишаються на індикаторі навіть при відпусканні клавіш на клавіатурі калькулятора;

· ці пристрої зсувають числа на одну позицію кожного разу як тільки набирається нова цифра.

Таким чином регістри зсуву є виключно корисними приладами, які широко використовуються в цифрових системах. [3]

Отже регістри зсуву – це регістри послідовної дії, що призначені для виконання операції зсуву двійкової інформації, яка подається у послідовному коді розряд за розрядом. Зсув або переміщення всіх цифр слова може здійснюватись за допомогою регістрів зсуву в напрямі від старших до молодших розрядів (зсув вправо) або від молодших до старших (зсув вліво).

Рис. 4.54 Структура та функціонування регістр зсуву

В обчислювальній техніці регістри зсуву двійкових чисел застосовують для виконання операцій множення та ділення (для виконання множення код зсувають вліво на один розряд, для ділення – вправо). Операції зсуву на один розряд потрібні лише для позиційної системи числення, при якій вага кожного розряду визначається його позицією в коді.

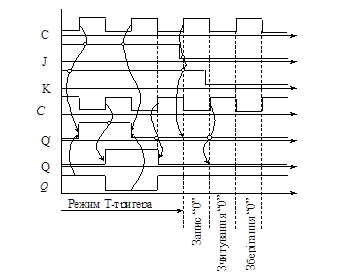

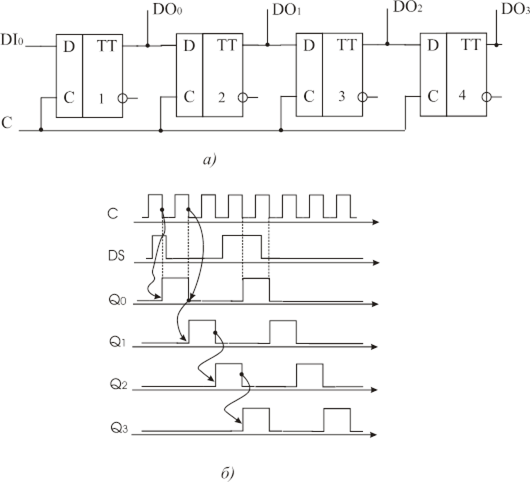

На основі синхронних RS-, D-, JK-тригерів можна будувати різні структури регістрів зсуву. На рис.4.11.а побудований регістр зсуву типу SIРО на базі чотирьох двоступеневих синхронних D-тригерів. Він має один інформаційний вхід DS (від англ. Data Serial ), на який інформація наводить у вигляді послідовного коду, і керуючий вхід С, на який подаються тактові синхронізуючі імпульси.

D -тригер (1) відповідає за молодший розряд (МР), в D-тригер (4) -за старший розряд (СР) чотирирозрядного числа, яке потрібно записати у даний регістр зсуву. Тоді з надходженням тактових імпульсів одночасно на динамічні входи С D-тригерів, для яких активним сигналом є зріз тактових імпульсів, вихід кожного тригера набуватиме стану попереднього. Таким чином, одиниця, що надійшла на інформаційний вхід DS регістра, зсунеться (рис.4.11.б вправо) з молодшого розряду до старшого синхронно з періодом надходження тактових імпульсів. Такий регістр належить до регістрів зсуву вліво.

Слід зазначити, що правильність запису інформації у регістр зсуву залежить і від того, як на його вхід надходять біти послідовного двійкового коду (починаючи з молодшого чи старшого розряду). У розглянутому на рис. 4.11.а регістрі зсуву вліво послідовний код надходить на вхід DS починаючи зі старшого біта. Для запису чотирирозрядного числа (так само, як і дня зчитування) у даний тригер потрібно чотири такти синхроімпульсів.

Зчитування даних з регістра, що після припинення подачi тактових iмпульсів зберігатимуться на його виходах D00, DO1, DO2, DO3, можна виконувати як в послідовному коді, з виходу останнього тригера (4), так і в паралельному коді, відразу з усіх розрядів. За розглянутим принципом роботи та подібною структурною схемою побудовано чотирирозрядний регістр на КМОН-структурі 564ИР2.

Двонапрямлені (або реверсивні) регістри зсуву здатні зсувати записану інформацію і вправо, і вліво, тобто завантажене у регістрі слово можна зсувати по лінійці тригерів як вправо, так і вліво. Напрям зсуву визначається рівнем керуючого сигналу (1 або 0).

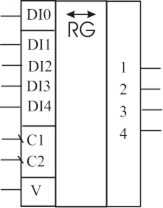

Для прикладу розглянемо мікросхему універсального чотирирозрядного регістра зсуву К555ИРІ яка виконана у схемотехніці ТТЛ середнього ступеня інтеграції. Вона має один послідовний DS (D0) тa чотири паралельних (D1,D2,D3,D4) iнформаційні входи. Умовне позначення регістра зсуву К555ИР1 показано на рис. 4.12. Регістр виконаний на чотирьох RS -тригерах, має два тактових входи С1 і С2, чотири виходи Q0, Q1, Q2 , Q3 i керуючий вхід V, що визначає режим роботи регістра (зсув вправо чи вліво). Mожливі чотири режими роботи універсального регістрa зсуву К555ИР1 введені у табл. 4.7.

Рис. 4.55 Приклад регістру зсуву. Регістр К555ИР1

Таблиця 4.21 Режими роботи регістра зсуву 555ИР1

| Режим роботи | Стан входів | ||||

| DІ0 | DI1…DI4 | V | C1 | C2 | |

| Зсув вправо | DS | ~ | 1  0 0

| ~ | |

| Зсув вліво | DS | ~ | ~ | 1  0 0

| |

|

Дата добавления: 2016-07-22; просмотров: 6986; |