Лічильники з послідовним переносом

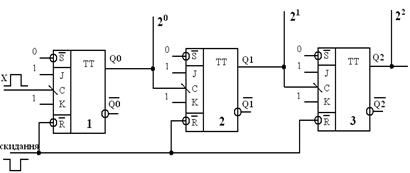

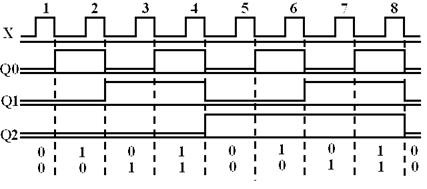

Послідовні лічильники - це асинхронні лічильники, що мають один вхід х і n виходів (Q) відповідно до числа послідовно з’єднаних тригерів. Найпростіші послідовні двійкові або лічильники за модулем 2m (Мл=2m) реалізуються на базі кількох Т -тригерів, кожний з яких працює як лічильник зa модулем 2. На рис.4.13 показано підсумовувальний лічильник за модулем 8 (m=З), який побудований на трьох універсальних двоступеневих JK -тригерах, часові діаграми його роботи зображені на рис. 4.14.

Рис. 4.56 Структура підсумовувального лічильника за модулем 8

Рис. 4.57 Часові діаграми роботи лічильника за модулем 8

Перед початком роботи лічильника всі його тригери переводяться у нульовий стан імпульсом скиду в нуль. Надходження першого iмпульсу своїм зрізом переводить тригер (1), тобто молодший розряд лічильника у стан 1, і на регістрі лічильника фіксується код (001). Другий імпульс, що надходить на вхід X тригера (1), повертає його в стан 0, але при цьому виникає iмпульс переносу, що утворений на першому ступені тригера (2), який змінить тепер стан тригера (2) на 1. Отже, на регістрі лічильника з’являеться число (010). Заповнення розрядів лічильника а кожним імпульсом буде продовжуватися доти, поки лічильник не відрахує максимальне число на його регістрі (111). Восьмий імпульс на вході лічильника переводить своїм зрізом тригер (1) в стан 0, в імпульс переносу - тригери (2) і (3) в стан 0, повертаючи таким чином лічильник у початковий нульовий стан. Зауважимо, що на інших входах тригерів під час роботи лічильника повинні бути такі рівні: J=K=1;  =0:

=0:  =0. За розглянутим принципом працюють чотирирозрядні асинхронні лічильники ТТЛ К155ИЕ2 (двійково-десятковий) і К155ИЕ5 (лічильник-подільник).

=0. За розглянутим принципом працюють чотирирозрядні асинхронні лічильники ТТЛ К155ИЕ2 (двійково-десятковий) і К155ИЕ5 (лічильник-подільник).

Розглянутий підсумовувальний двійковий лічильник легко перетворити віднімальний за модулем 8, якщо замість прямих виходів Q0,Q1,Q2 у тригерів використати їх інверсні виходи які при цьому будуть утворювати його регістр вихідного коду. У цьому неважко переконатись, бо при такій комутації виводів тригерів перенос від розряду до розряду буде утворюватися при переводі відповідного тригера у стан 1, а не у стан 0, як це мало місце у підсумовувальному лічильнику. У віднімальному лічильнику кожний прихід імпульсів на його вхід не збільшує, а зменшує вміст лічильника на одиницю. Тому, коли потрібно підрахувати число відданих імпульсів, даний віднімальний лічильник попередньо треба встановити у стан (111).

Таким чином, з кожним надходженням вхідних імпульсів на регістр віднімальногого лічильника фіксуватиметься обернений код так, як наведено у табл. 4.8 для випадку віднімального/двійкового/ лічильника за модулем 8.

Таблиця 4.22 Робота віднімального лічильника за модулем 8

| Регістр віднімального лічильника за модулем 8 | Число вхідних імпульсів | ||||||||

| Q0 Q1 Q2 |

У розглянутих послідовних двійкових лічильниках зміна стану поширюється послідовно по всій лінійці тригерів. Такі лічильники можна називати по-різному залежно від того, яку характерну властивість підкреслювати. Якщо підкреслити те, що запуск тригерів з лічильника здійснюється не одночасно, тут підходять визначення "з послідовним переносом" і "асинхронний". Назва "лічильник за модулем 2 " відбиває максимальне число станів (тобто модуль лічби Мл =2m), яке фіксується на регістрі лічильника за один повний цикл лічби, a визначення "m-розрядний" показує кількість двійкових розрядів регістра лічильника.

Послідовні лічильники можуть бути й реверсивними, якщо в них передбачити додаткові ЛЕ, які б керували режимом роботи на підсумовування або на віднімання вхідних імпульсів.

Розглянуті асинхронні лічильники з послідовним переносом мають загальний недолік - значний час реєстрації підрахованої кількості вхідних імпульсів, тобто мають малу швидкодію. Цей недолік зумовлений втратою часу на послідовне формування імпульсу переносу в кожному розряді лічильника. У найбільш несприятливому випадку перенос, що виник в молодшому розряді, викличе по черзі переноси у всіх інших розрядах лічильника і час реєстрації при цьому буде дорівнювати /m•tзюп /де tз.п- затримка переносу/ в одному розряді. Зменшення часу реєстрації лічильника досягається при застосуванні паралельного переносу біта з молодшого у старший розряд, що реалізовано в лічильниках з паралельним переносом. [1]

Дата добавления: 2016-07-22; просмотров: 3860;