Краткие сведения из теории

Рис. 4

Рис. 4

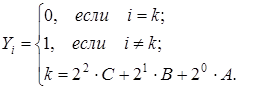

| Дешифратор - логическая комбинационная схема, которая имеет n информационных входов и 2n выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из выходов. Обычно n равно 2,3 или 4. На рис. 4 изображен дешифратор с n=3, активным уровнем является уровень логического нуля (в данной лабораторной работе для удобства вместо схемы дешифратора используется схема демультиплексора, это возможно благодаря сходству алгоритмов работы). На входы С, В, А можно подать следующие комбинации логических уровней: 000, 001, 010, ..., 111, всего 8 комбинаций. |

Схема имеет 8 выходов, на одном из которых формируется низкий потенциал, на остальных - высокий. Номер этого единственного выхода, на котором формируется активный (нулевой) уровень, соответствует числу N, определяемому состоянием входов С, В, А следующим образом: N = С*22 + В*21 + А*20.

Например, если на входы подана комбинация логических уровней 011, то из восьми выходов микросхемы (YO, Y1...Y7) на выходе с номером N=3 установится нулевой уровень сигнала (Y3=0), a все остальные выходы будут иметь уровень логической единицы. Этот принцип формирования выходного сигнала можно описать следующим образом:

(6)

(6)

Видно, что уровень сигнала на выходе Y3 описывается выражением:  .

.

В таком же виде можно записать выражения для каждого выхода дешифратора:

,

,  ,

,

,

,  , (7)

, (7)

,

,  ,

,

,

,  .

.

Рис.5

Рис.5

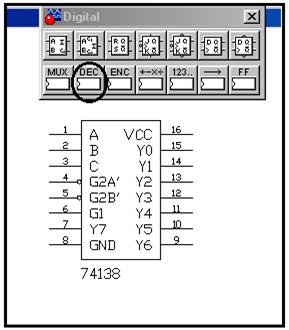

| Помимо информационных входов А, В, С дешифраторы обычно имеют дополнительные входы управления G. Сигналы на этих входах, например, разрешают функционирование дешифратора или переводят его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на всех выходах установится уровень логической единицы. Можно сказать, что существует некоторая функция разрешения, значение которой определяется состояниями управляющих входов. Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является |

уровень логической единицы, у дешифраторов с инверсным входом - уровень логического нуля. На рис. 4 представлен дешифратор с одним инверсным входом управления. Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

(8)

(8)

У дешифратора с несколькими входами управления функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления. Например, для дешифратора 74138 с одним прямым входом управления G1 и двумя инверсными G2A и G2B (рис. 5) функции выхода  и разрешения G имеют вид:

и разрешения G имеют вид:

(9)

(9)

Обычно входы управления используются для каскадирования (увеличения разрядности) дешифраторов или при параллельной работе нескольких схем на общие выходные линии.

Дешифратор может быть использован и как демультиплексор - логический коммутатор, подключающий входной сигнал к одному из выходов. В этом случае функцию информационного входа выполняет один из входов разрешения, а состояние входов С, В и А задает номер выхода, на который передается сигнал со входа разрешения.

2.2. Реализация произвольной функции с использованием дешифратора

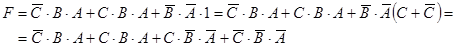

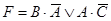

Рассмотрим пример реализации функции трех аргументов с использованием базового дешифратора (рис.4). Функция задана аналитическим выражением  .

.

Раскроем функцию до СДНФ, для этого последнее слагаемое умножим на 1, м запишем ее как

Функция не изменится, если взять от нее двойную инверсию

.

.

Используя теорему де Моргана (см. Приложение 2) раскроем внутреннюю инверсию

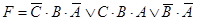

Анализируя выражения для выходов базового дешифратора (7) функцию можно записать

Теперь можно реализовать функцию используя базовый дешифратор, для этого нужно информацию с выходов Y0, Y3, Y4, Y7 подать на вход логического элемента 4-входового И-НЕ (рис.6).

Рис.6

2.3. Задание для выполнения

Соберите и схему на основе базового дешифратора и элементов И-НЕ или И, реализующие заданную функцию F. На входе разрешения установить активный уровень. Варианты задач приведены ниже. Для выбора варианта взять 2 последние цифры в номере зачетной книжки.

| Вариант | |

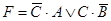

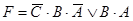

| 1,21,41,61 |

|

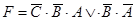

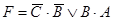

| 2,22,42,62 |

|

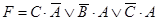

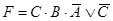

| 3,23,43,63 |

|

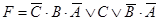

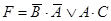

| 4,24,44,64 |

|

| 5,25,45,65 |

|

| 6,26,46,66 |

|

| 7,27,47,67 |

|

| 8,28,48,68 |

|

| 9,29,49,69 |

|

| 10,30,50,70 |

|

| 11,31,51,71 |

|

| 12,32,52,72 |

|

| 13,33,53,73 |

|

| 14,34,54,74 |

|

| 15,35,55,75 |

|

| 16,36,56,76 |

|

| 17,37,57,77 |

|

| 18,38,58,78 |

|

| 19,39,59,79 |

|

| 20,40,60,80 |

|

МУЛЬТИПЛЕКСОРЫ

3.1. Краткие сведения из теории

Мультиплексор - комбинационная логическая схема, представляющая собой управляемый переключатель, который подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу (адресу), определяемому комбинацией логических уровней на входах управления. Кроме информационных и управляющих входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в активное состояние. При подаче на вход разрешения пассивного уровня мультиплексор перейдет в пассивное состояние, для которого сигнал на выходе сохраняет постоянное значение независимо от значений информационных и управляющих сигналов. Число информационных входов у мультиплексоров обычно 2, 4, 8 или 16. На рисунке 7 представлен мультиплексор 8x1 с инверсным входом разрешения G, прямым Y и инверсным W-выходами (  ).

).

Рис. 7 – Мультиплексор 8x1

Уравнение работы мультиплексора

Функционирование мультиплексора, представленного на рисунке 2.1, описывается характеристическим уравнением, связывающим сигнал на выходе (Y) с разрешающим (G), входными информационными (D0 … D7) и управляющими (А, В, С) сигналами:

Как видно из уравнения, на мультиплексоре можно реализовать логические функции, для чего нужно определить, какие сигналы и логические константы следует подавать на входы мультиплексора.

3.2. Реализация заданной функции с помощью мультиплексора

Логическая функция n переменных определена для 2n комбинаций значений переменных. Это позволяет реализовать функцию n - переменных на мультиплексоре, имеющем n - управляющих и 2n информационных входов. В этом случае каждой комбинации значений аргументов соответствует единственный информационный вход мультиплексора, на который подается значение функции.

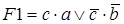

Например, требуется реализовать функцию

Эта функция определена только для 8 комбинаций значений переменных, поэтому для её реализации можно использовать мультиплексор 8x1 с тремя управляющими входами. Составим таблицу истинности функции (табл.18):

| Таблица 18 | ||||

| DN | c | b | a | F1 |

| D0 | ||||

| D1 | ||||

| D2 | ||||

| D3 | ||||

| D4 | ||||

| D5 | ||||

| D6 | ||||

| D7 |

Из таблицы видно, что для реализации функции на мультиплексоре необходимо подать на информационный вход мультиплексора с номером N сигнал, значение которого равно соответствующему значению функции F1, т. е. на входы D0, D1, D5, D7 следует подать уровень логического нуля, а на остальные - уровень логической единицы. Таким образом, при подаче комбинации логических уровней на управляющие входы мультиплексора, к его выходу подключится вход, значение сигнала на котором равно соответствующему значению функции. Схемная реализация приведена на рисунке 8.

Рис. 8 – Схемная реализация

При реализации логических функций на информационные входы можно подавать не только константы, но и изменяющиеся входные сигналы. Так, например, рассмотрим другой способ реализации функции F1, рассмотренной выше. Для этого минимизируем выражение функции:  .

.

Составим таблицу истинности функции в зависимости от значений переменных а и b:

Заданную такой таблицей функцию реализуют, как и в предыдущем случае, подав на вход с номером N сигнал, значение которого соответствует значению функции F1. В данном случае сигналы с и с’, соответствующие переменной с, подаются на информационные входы, как указано в таблице истинности. При этом сокращается число управляющих входов.

| Таблица 19 | |||

| N | b | A | F1 |

| |||

| с |

Схемная реализация такого способа задания функции представлена на рисунке 9. Так как используются только два адресных входа, управляющий вход С можно заземлить. При этом состояние информационных входов D4...D7 безразлично. Уровень сигнала на выходе схемы определяется комбинацией уровней сигналов в точках А, В, С, соответствующих переменным а, b, с. Схема рисунка 9 по существу представляет собой мультиплексор 4x1 с двумя управляющими и четырьмя информационными входами.

Рисунок 9 – Схемная реализация второго способа задания функции

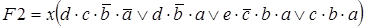

Если функцию можно представить в виде произведения одночлена на многочлен, то её также можно реализовать при помощи мультиплексора. Как следует из уравнения мультиплексора, сигнал, соответствующий одночлену, нужно подать на вход разрешения. Например, требуется реализовать функцию F2, описываемую следующим выражением:

.

.

При реализации данной функции на мультиплексоре сигнал, соответствующий переменной x, следует подать на его разрешающий вход. Рассмотрим, какие сигналы необходимо подать на управляющие входы мультиплексора. Выражение в скобках можно рассматривать как некоторую функцию f пяти переменных: а, b, с, d, е, из которых наиболее часто используются переменные a, b и с. Поэтому сигналы, соответствующие этим переменным, нужно подать на управляющие входы мультиплексора.

Определим, какие сигналы следует подать на информационные входы, чтобы реализовать функциюf. Для этого составим таблицу истинности функции в зависимости от значений переменных a, b и с.

| Таблица 20 | ||||

| N | C | b | a | f |

| d | ||||

| e | ||||

| d | ||||

Из таблицы видно, что на информационные входы с номерами N = 0, 2, 4, 6 нужно подать уровень логического нуля. Сигнал, соответствующий переменной d, нужно подать на входы с номерами N = 1, 5, сигнал, соответствующий переменной е, - на вход с номером 3. Соответствующая схемная реализация представлена на. рисунке 10.

Рис. 10 – Схемная реализация

Дата добавления: 2016-07-18; просмотров: 2120;