Модули интегральных микросхем

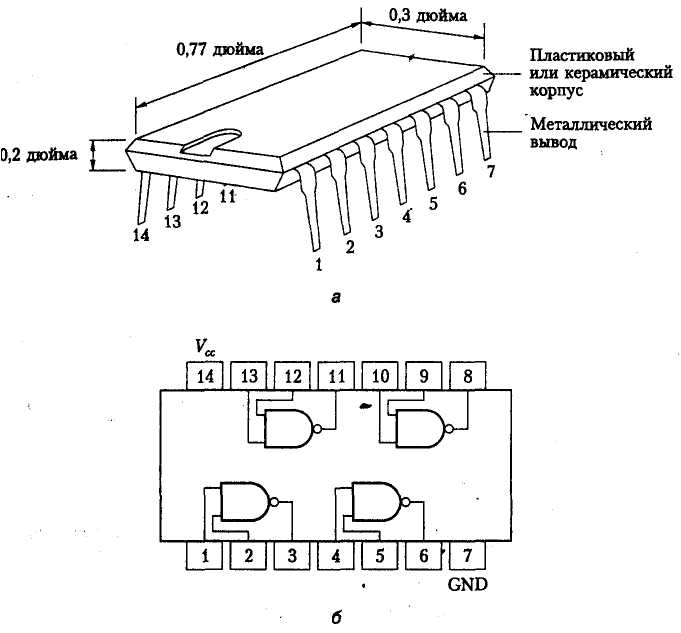

В предыдущих разделах были рассмотрены базовые принципы построения электронных схем для реализации логических функций. Для их практического воплощения используются серийно производимые интегральные схемы (ИС). Когда в 1960-х годах появились первые интегральные схемы, логические вентили стали выпускать в виде стандартизированных чипов. Такой чип монтировался в полностью закрытый защитный корпус со множеством металлических контактов для соединения с внешним устройством. Стандартные модули ИС имели разное количество контактов. На рис. 2.19 показан простейший модуль с четырьмя вентилями И-НЕ. Эти четыре вентиля имеют общие контакты для соединения с «землей» и источником питания. Подобные ИС, содержащие всего несколько логических вентилей, называются схемами с малой степенью интеграции или малыми интегральными схемами (МИС).

Для столь простых функций, которые выполняют малые интегральные схемы, они занимают слишком много физического пространства. Более того, их производительность довольно низка из-за электрических характеристик контактов модуля ИС. Чтобы сгенерировать сигналы достаточной мощности, необходимые для управления устройствами и схемами, подсоединенными к внешним контактам, приходится использовать большие транзисторы. В результате задержка на распространение сигнала и потребляемая схемой мощность заметно увеличиваются.

Время задержки на распространение сигнала для КМОП-вентиля И-НЕ, который входит в состав модуля интегральных может достичь 5 нс. В случае таких же вентилей, используемых в больших интегральных схемах КМОП, задержка обычно составляет не более 0,2 нс, что зависит от технологии производства.

В настоящее время производятся гораздо более крупные ИС, реализующие образные логические элементы. Чип интегральной схемы может содержать полезный функциональный блок, такой как сумматор, умножитель, регистр, шифратор или дешифратор, либо просто набор вентилей и программируемых переключателей внутренних соединений, с помощью которых конструктор может реализовать множество разных функций.

Рис. 2.19. Модуль 14-контактной интегральной схемы: внешний вид (а); логическая структура схемы с четырьмя 2-входовыми вентилями И-НЕ (б)

Рис. 2.19. Модуль 14-контактной интегральной схемы: внешний вид (а); логическая структура схемы с четырьмя 2-входовыми вентилями И-НЕ (б)

Лекция 23

Триггеры и защелки

Логические цепи могут быть разделены на две большие группы. Первая—цепи комбинационной логики, составленные из логических элементов, вторая — последовательные логические цепи, состоящие из элементов, называемых триггерами. Триггеры объединяют в системы с целью образования последовательных логических цепей, предназначенных для размещения данных, обеспечения нужной временной задержки, вычислений и формирования требуемых последовательностей сигналов. Триггеры обладают важной способностью запоминания. Триггер запомнит свои входные сигналы даже тогда, когда эти сигналы будут сняты.

Термином триггер (flip-flop) называют запоминающий элемент, выходное состояние которого меняется на фронте управляющего тактового сигнала (то есть в момент его перехода из одного состояния в другое). Логический элемент, напротив, не сможет запомнить свое состояние на выходе, если будут сняты входные сигналы.

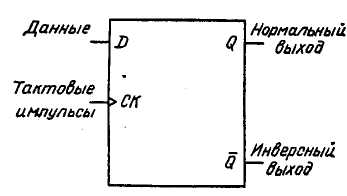

На рис. 2.20 приведена очень широко используемая схема D - триггера (называемого также триггером данных).

|

Рис.2.20. D – триггер.

Отметим здесь два входа, обозначенных D (для данных) и СК (для сигналов синхронизации или тактовый вход).

Триггер имеет обычно два взаимно инверсных выхода, обозначенных Q и  (HE-Q).

(HE-Q).

Выход Q используется более часто и называется нормальным. Выход Q называется дополнительным или инверсным выходом триггера. Графическое обозначение «>» на входе СК логической схемы D-триггера указывает, что этот триггер передает данные со входа на выход при положительном фронте ( ) тактовых импульсов.

Операционные состояния D - триггера приведены в левой колонке таблицы истинности (Таблицы переходов триггера) (табл. 3.8).

Таблица 3.8. Таблица истинности статистических состояний D - триггера

| Операционные состояние | Входы | Выходы |

| D СК | Q

| |

| Активизация Сброс Ожидание | 1 0 * Отсутствие | 1 0 0 1 Предыдущее состояние |

Примечание. 0 —LOW; 1 - HIGH; *—не имеет значения; —переход от LOW к HIGH тактового импульса.

Установить (или активизировать) триггер означает, что на нормальном выходе Q устанавливается 1. Первая строка таблицы истинности показывает, что подачей 1 на вход D-триггера при положительном тактовом импульсе СК на выходе Q устанавливается 1. Вторая строка соответствует сбросу (установке в нуль) триггера. Сбросить триггер означает вернуть выход Q в состояние 0. Установить состояние ожидания - это значит сохранить на выходе данные предыдущего состояния. Когда триггер находится в состоянии ожидания, изменения логических состояний данных на входе не влияют на состояние выходов. Состояние ожидания характеризует способность триггера запоминать сигналы. Отметим, что операции установки и сброса рассматриваются по отношению к выходу Q.

Большинству устройств, в которых задействована цифровая логика, требуются элементы для хранения информации. Например, схема управления кодовым замком должна запоминать последовательность открывающего его набора цифр. Еще один важный пример — электронная память для хранения данных, необходимая цифровым компьютерам. Базовый электронный элемент, используемый для хранения информации, называется защелкой (latch).

равны 1.

|

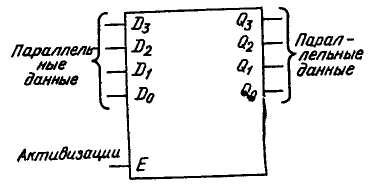

рис. 3.21. Логическая схема прозрачной 4-разрядной защелки.

Рассмотрим логическую схему, приведенную на рис. 3.21, на которой изображена 4-разрядная прозрачная защелка. Каждый триггер-защелка, входящий в это устройство, является устройством либо памяти, либо размещения данных. Для лучшего понимания состава регистра-защелки необходимо рассматривать его состоящим из четырех D-триггеров, тактовые входы которых объединены одним входом разрешения (или активизации). Согласно соответствующей таблице истинности (табл. 3.9) при поступлении 1 на вход Е (Н-сигнал) данные со входов D0—D3 будут переданы на выходы Q0— Q3 соответственно. Четырехразрядное слово поступает на входы в параллельной (но не в последовательной) форме и передается на выходы в той же форме.

таблица 3.9

| Функциональное состояние | Входы | Выход |

| D Е | Q | |

| Признание данных | 0 1 1 1 | |

| Захват данных | * 0 | Предыдущее состояние |

Дата добавления: 2016-07-05; просмотров: 2583;