Программируемая матричная логика

В программируемой логической матрице программируются обе составляющие и матрица И, и матрица ИЛИ. На практике очень популярны похожие схемы, в которых входы матрицы И являются программируемыми, а соединения с матрицей ИЛИ фиксированными. Такие устройства называются микросхемами с ПМЛ или программируемой матричной логикой (Programmable Array Logic, PAL).

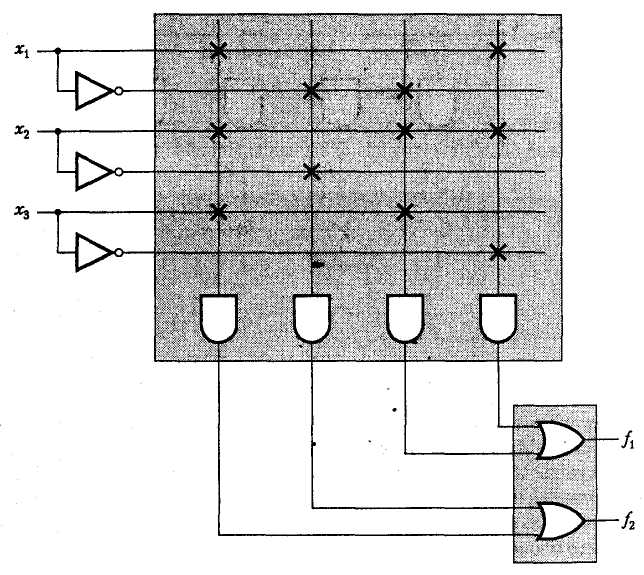

На рис. А.43 показан простой пример схемы с ПМЛ, реализующей две функции. Количество вентилей И, соединенных с каждым вентилем ИЛИ, определяет максимальное число произведений, которое может входить в состав представления данной функции (в виде суммы произведений). Вентили И жестко соединены конкретными вентилями ИЛИ. Это значит, что произведение не может использоваться в нескольких выходных функциях.

f1= x1x2  +

+  x2x3

x2x3

f2=

+ x1x2x3

+ x1x2x3

Рис. А.43. Пример схемы с ПМЛ

Микросхемы ПМЛ выпускаются в разных конфигурациях. В них может быть много входных переменных и выходов, что позволяет на их основе реализовать очень сложные функции. Для большей гибкости на выходе вентилей ИЛИ в них включают триггеры. Таким образом, на одном чипе ПМЛ может быть реализовала достаточно сложная логическая схема.

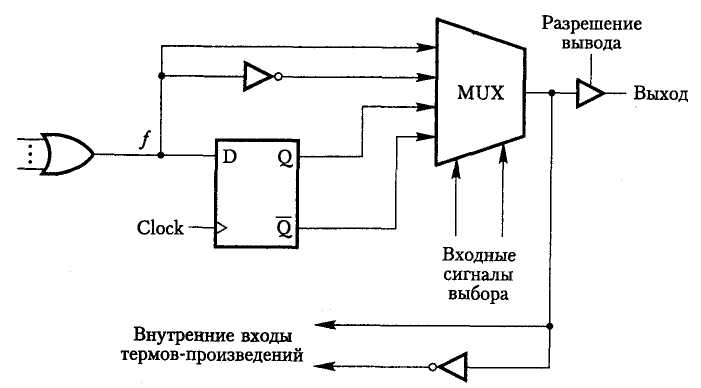

Насколько гибкими могут быть схемы на основе ПМЛ, можно судить по рис. A.44. Здесь вычисляется значение функции f а затем мультиплексор определяет, какое ее значение — истинное, дополненное либо сохраненное (с предыдущего такта) — следует передать на выход. Входные сигналы выбора в мультиплексоре можно реализовать как программируемые соединения. Результирующее значение передается на выход через повторитель с тремя состояниями, управляемый сигналом, который разрешает выдачу значения. Обратите внимание, что выходной сигнал мультиплексора может использоваться как входной сигнал для термов-произведений или других вентилей ИЛИ в этой же ПМЛ- микросхеме. Таким образом могут создаваться схемы с несколькими уровнями логических вентилей

Рис. А.44. Пример обработки выходного сигнала ПМЛ-элемента

Дата добавления: 2016-07-05; просмотров: 4573;