Программируемые вентильные матрицы

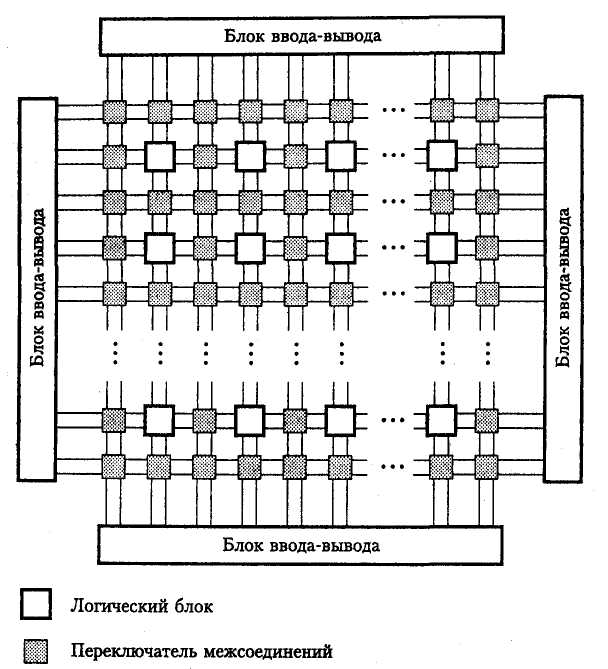

Микросхемы ПМЛ достаточно универсальны, но их размер ограничен по той причине, что для каждой суммы произведений требуется один выходной контакт, ля преодоления этого ограничения разработан класс более мощных программируемых устройств, называемых программируемыми вентильными матрицами, ПВМ (Field Programmable Gate Array, FPGA). Концептуальная схема такой матрицы показана на рис. А.46. Она состоит из набора логических блоков (обозначенных черными квадратами), которые могут соединяться с помощью общих межсоединений. Межсоединения, выделенные на рисунке серым цветом, состоят из отрезков проводящих линий и программируемых переключателей. Переключатели используются для установки соединений между разными сегментами проводящих линий. Построенный таким образом чип обладает исключительной гибкостыо. Для доступа к выходным и входным контактам чипа здесь предназначены буферы ввода-вывода.

Рис. А.46. Концептуальная схема программируемой вентильной матрицы

Существует множество конструкций логических блоков и структур межсоединений. Логическими блоками могут служить простейшие схемы на основе мультиплексоров, реализующие логические функции (см. раздел А. 10). В еще одной популярной конструкции в качестве логического блока используется простейшая таблица для выбора значения. Например, таблица с четырьмя входами может быть реализована в виде 16-разрядной схемы памяти, в которой хранится таблица истинности логической функции. Каждый бит памяти соответствует одной комбинации значений входных переменных. Путем программирования этой таблицы можно реализовать любую функцию четырех переменных. Еще логические блоки могут содержать триггеры, обеспечивающие дополнительную гибкость. В дополнение к логическим блокам многие программируемые вентильные матрицы включают достаточно большое количество ячеек памяти (на рис. А.46 они не показаны), которые могут использоваться для реализации таких структур, как очереди или RAM-И ROM-компоненты в приложениях для встроенных процессоров (см. главу 9). С точки зрения пользователя, между программируемыми вентильными матрицами и сложными программируемыми логическими устройствами имеются существенные различия. Функциональные возможности чипов вентильных матриц шире, и на их основе могут быть реализованы довольно большие и сложные логические схемы. Один такой чип может содержать более миллиона логических вентилей. Различна и скорость работы этих двух типов микросхем. Поскольку во внутренних межсоединениях вентильной матрицы используются программные переключатели, задержка на распространение сигнала в ней неизбежно будет более заметной, нежели у таких менее гибких устройств, как микросхемы ПМЛ или СПЛУ.

Программируемые вентильные матрицы становятся все более популярными у конструкторов цифровых логических устройств, поскольку они позволяют располагать на одном чипе очень сложные схемы и избегать разработки и создания пользовательских СБИС, что, во-первых, дорого, а во вторых, требует очень много времени. Пользуясь средствами автоматизированного проектирования, конструкторы могут создавать интегральные схемы на основе программируемых вентильных матриц не за месяцы, как пользовательские СБИС, а за считанные дни.

Даже самые большие ИС на основе программируемых вентильных матриц стоят несколько сотен долларов, и затраты, связанные с их разработкой, очень малы по сравнению с затратами на разработку пользовательских чипов. Основы программируемых логических устройств освещаются во многих современных книгах по проектированию логических схем. За более подробной информацией об этих устройствах читателя можно отослать и к документации от производителей.

Дата добавления: 2016-07-05; просмотров: 2914;