ТЕХНОЛОГИЯ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

Под интегральной схемой (ИС) понимается электронное устройство, имеющее высокую плотность компоновки элементов электрической схемы, в котором все или часть элементов сформированы и электрически соединены между собой на одном полупроводниковом кристалле или диэлектрической подложке.

ИС представляет собой многокомпонентное тело из слоевых композиций на поверхности или в приповерхностном слое твердого тела (полупроводника). Ее характеристики определяются свойствами тонких слоев различных материалов, которые в свою очередь во многом зависят от условий их формирования, последовательности и вида технологических операций.

Вопросы разработки и производства ИС рассматриваются в новой отрасли науки и техники -микроэлектронике, изучающей технологические, физические конструктивные особенности электро- и радиоэлементов с размерами не более 1 мкм хотя бы по одной координате.

Наиболее важной проблемой при создании микросхем является разработка элементов и совместимых друг с другом материалов со стабильными и воспроизводимыми характеристиками тонких слоев, а также последовательности технологических операций формирования многослойной структуры, при которой последующие операции не оказывают вредного влияния на характеристики ранее сформированных слоев.

В зависимости от способа создания пленочных композиций микросхемы делятся на два класса — гибридные интегральные схемы (ГИС) и полупроводниковые интегральные схемы (ИС).

Гибридная интегральная схема — микроминиатюрное электронное устройство, элементы которого нераздельно связаны конструктивно, технологически и электрически на поверхности диэлектрической (стеклянной, керамической) подложки. В технологии ГИС пассивные элементы (резисторы, проводники, контактные площадки, конденсаторы, диэлектрические и изоляционные слои) изготовляют в одном технологическом цикле в виде металлических и диэлектрических пленок на поверхности подложки. Активные компоненты (диоды, транзисторы), а при необходимости также микроминиатюрные дискретные пассивные компоненты (конденсаторы, катушки индуктивности и т. п.) монтируются на поверхности подложки и соединяются с другими элементами.

В зависимости от технологического процесса формирования пассивных элементов гибридные схемы

юдразделяются на тонкопленочные и толстопленочные.

Гонкопленочная технология — последовательное нанесение на общее основание тонких (менее 1-2 мкм) пленочных проводников, контактов, резисторов, изоляторов армированием микрогеометрии элементов и их соединений (топологический рисунок) или в процессе осаждения с помощью трафаретов (масок), а также с помощью вного локального травления сплошных слоев материалов.

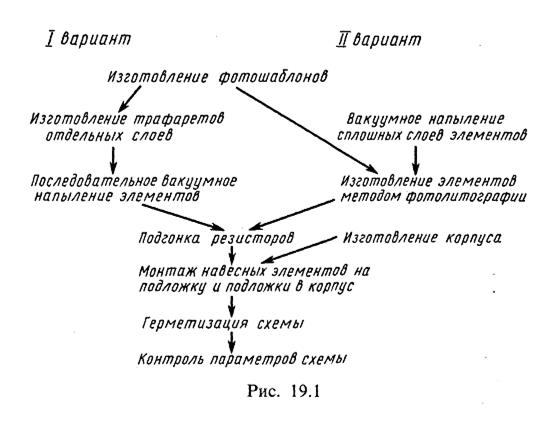

Последовательность технологических операций при изготовлении тонкопленочных ГИС по двум вариантам приведена на рис. 19.1.

Толстопленочная технология — последовательное нанесение через сетчатые трафареты и вжигание в керамические подложки паст резистивного, проводящего и диэлектрического назначения.

Проводящие и резистивные пасты представляют собой смесь мелкодисперсного металлического порошка, стекла, выполняющего роль постоянного связующего, и органических жидкостей, обеспечивающих вязкость смеси. Металл обеспечивает образование проводящих (серебро, золото, платина, палладий и их сплавы) или ре-зистивных (благородные металлы и их композиции с оксидами) дорожек.

Пасты для изоляционных слоев представляют собой смесь стекла и органических жидкостей.

Сетчатые трафареты имеют очень малый размер ячеек (порядка 50 мкм). В соответствии с необходимой топологией схемы на некоторых участках трафарета ячейки заполняются эмульсией, пигментной бумагой или фоторезистом, предохраняющими подложку от попадания пасты на эти участки. Нанесение пасты производится перемещающимся ракилем. Вначале наносится проводящая паста для создания соединительных порошков, обкладок конденсаторов, контактных площадок. Паста высушивается, а затем вжигается при температуре 750- 950 °С. Затем через другой трафарет наносится резистивная паста, которая вжигается при меньшей температуре Аналогично наносится и вжигается диэлектрическая паста для образования диэлектрического слоя в толстопленочных конденсаторах и в местах пересечения проводников.

После формирования топологии последовательность других технологических операций аналогична процессам изготовления тонкопленочных схем.

Полупроводниковые (твердотельные) интегральные схемы получают путем целенаправленного локального изменения свойств материала полупроводниковой подложки, легированной примесью.

Добавлением примесей в строго определенных местах и количествах можно изменять проводящие характеристики в материале подложки из полупроводников кремния и германия в очень широком диапазоне — практически от проводника до изолятора. Это свойство используется для получения в кристаллах как активных, так и пассивных элементов. Изменение свойств происходит лишь в небольшом слое кристалла, равном нескольким микрометрам и называемом р—n-переходом, где смыкаются две зоны с различной проводимостью — дырочной и электронной. Остановимся на этом подробно.

Химические элементы кремний и германий имеют на внешней электронной оболочке четыре электрона, т. е. их валентность равна четырем. Известно, что атом имеет более устойчивое состояние, когда на его внешней оболочке находится восемь электронов. При низких температурах в кристаллах полупроводника все электроны связаны с атомами (подвижных электронов нет), и кристалл представляет собой изолятор.

При повышении температуры полупроводника отдельные электроны отрываются от атомов, становятся подвижными и могут создавать электрический ток в кристалле, когда к нему прикладывается напряжение. При удалении электрона из атома в оболочке атома образуется свободное место-дырка. Свободные электроны дырки беспорядочно перемещаются по кристаллу.

При включении такого кристалла в электрическую цепь наблюдается упорядоченное движение электронов от отрицательного полюса к положительному. При стрече свободного электрона с дыркой они рекомбинируют и их движение прекращается. Такая проводимость назыется собственной проводимостью полупроводника.

Если в кристалл кремния или германия ввести небольшое количество, например, алюминия, то проводимость легированного им кристалла будет, в основном, дырочной. Такой кристалл называется полупроводником р-типа.

При введении в кремний и германий, например, мышьяка, получим полупроводник с электронной проводимостью, называемый полупроводником р-типа.

В кристалле полупроводника можно создать с помощью локального легирования одновременно две зоны: p-типа и n-типа. Границу между ними называют р — п-переходом, который может выполнять функции диода.

Создавая разнообразные комбинации р— n-переходов получают элементы — диоды, транзисторы, резисторы и т. п. Сочетания любого числа элементов образуют желаемую схему, а так как все они являются составными частями одного кристалла полупроводникового материала, то получается полностью монолитная твердотельная структура.

Базовой технологией создания полупроводниковых ИС является эпитаксиалъно-планарная технология, по которой поверхность полупроводниковой монокристаллической пластины вначале окисляют. Затем осуществляют локальное травление оксида слоя и через вскрытые в нем окна производят легирование полупроводника. Легирующие примеси диффундируют в подложку из газовой фазы при высокой температуре. Последующим окислением окна снова закрываются. Повторяя технологические операции окисления, селективного травления и диффузии различных примесей, можно реализовать различные схемные элементы: диоды, транзисторы, сопротивления и емкости. Однако емкостные элементы в связи с их большой площадью и высокой стоимостью технологических операций в ИС практически не применяют. На одной пластине монокристалла полупроводника диаметром около 100 мм формируется одновременно до нескольких тысяч ИС.

Последующими операциями технологического процесса являются: получение вакуумным напылением или фотолитографией металлических проводников, которые соединяют элементы схемы, и контактных площадок, отбраковка пластин по параметрам отдельных ИС, разрезка пластины на отдельные ИС, монтаж ИС в корпусе, соединение контактных площадок с выводами корпуса, герметизация.

Выбор конструкции и технологии изготовления интегральных схем обусловливается технико-экономическими соображениями. Толсто- и тонкопленочная технологии отличаются широкими возможностями реализации схем по точности элементов. Кроме того, они характеризуются сравнительно низкой стоимостью подготовки производства. На их базе можно изготовлять широкую номенклатуру схем малых серий (специальных ГИС).

Преимущественное использование тонкопленочной технологии в производстве прецизионных схем объясняется возможностью достижения более высокой разрешающей способности, точности и стабильности элементов схем.

Толстопленочная технология отличается несколько меньшим циклом подготовки производства и менее сложным технологическим оборудованием. Она используется для получения сравнительно несложных схем в устройствах числового программного управления, ЭВМ и др. Для получения ГИС толстопленочная технология в ряде случаев обладает преимуществами по сравнению с тонкопленочной.

Технологию полупроводниковых ИС применяют для изготовления изделий массового производства — цифровых схем ЭВМ, микропроцессоров, электронных часов, счетных машин и т. п.

Ряд технологических операций трех основных видов технологии изготовления интегральных микросхем по своей физической природе аналогичен, несмотря на различия используемых материалов и оборудования.

Дата добавления: 2016-06-22; просмотров: 22068;