Быстродействие логических элементов

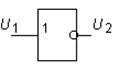

Быстродействие является важнейшим показателем цифровых устройств, определяющим скорость обработки информации. Быстродействие логических элементов характеризуется средним временем задержки сигнала tср, смысл которого поясняется на рис. 3.5 для случая инвертора.

а б

Рис. 3.5. Обозначение сигналов инвертора (а);

принцип определения среднего времени задержки (б)

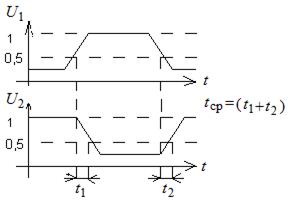

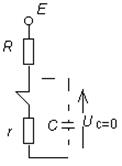

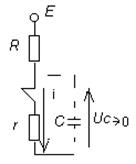

Быстродействие логических элементов зависит как от физических процессов переключения электронных компонентов, входящих в состав элемента, так и от скорости перезарядки паразитных внешних емкостей. На рис. 3.6 показан переход инвертора из состояния низкого уровня, когда напряжение на паразитной емкости нагрузки близко к нулю, в состояние высокого уровня, которое заканчивается не после запирания усилительного элемента (размыкание ключа), а после заряда емкости до напряжения высокого уровня. Очевидно, что имеет место и обратный процесс, когда после замыкания ключа низкий уровень устанавливается лишь после разряда емкости.

Естественно, что процессы переключения электронных элементов из одного состояния в другое сопровождаются потреблением мощности от источника питания Рп.

а б в

Рис. 3.6. Исходное состояние инвертора (а);

процесс установления высокого уровня (б);

процесс установления низкого уровня (в)

Ясно, что чем больше затрачивается мощность, тем быстрее может происходить переход элемента из одного состояния в другое. Технологически же приемы, обеспечивающие снижение времени переноса зарядов в объеме полупроводника и уменьшение паразитных емкостей, позволяют уменьшить время задержки переключения и без потребления значительной мощности. Поэтому показателем технологического совершенства логического элемента может служить энергия переключения Эп, рассчитываемая по формуле

.

.

Рассмотрим логические элементы распространенных серий с точки зрения скорости переключения и потребляемой мощности.

Классическим представителем ТТЛ-технологии является логический элемент И-НЕ, в котором по технологическим соображениям роль диодов, реализующих операцию И, выполняет многоэмиттерный транзистор VT1 (рис. 3.7).

Двухтактный выходной инвертор выполнен на однотипных (n-р-n) транзисторах VT3–VT4, поскольку по технологическим соображениям применение разнотипных (комплементарных) транзисторов в цифровой технике затруднено. Это обстоятельство приводит к необходимости фазорасщепителя (VT2). Транзисторы инвертора работают в режиме насыщения, а многоэмиттерный транзистор – в режиме малых токов. Все это ограничивает предельные значения времени переключения. Варьируя значение номиналов R1–R4, можно увеличить быстродействие за счет повышения потребляемой мощности. В табл. 3.1 приведены сравнительные параметры микросхем ТТЛ, демонстрирующие связь между потребляемой мощностью и быстродействием.

Двухтактный выходной инвертор выполнен на однотипных (n-р-n) транзисторах VT3–VT4, поскольку по технологическим соображениям применение разнотипных (комплементарных) транзисторов в цифровой технике затруднено. Это обстоятельство приводит к необходимости фазорасщепителя (VT2). Транзисторы инвертора работают в режиме насыщения, а многоэмиттерный транзистор – в режиме малых токов. Все это ограничивает предельные значения времени переключения. Варьируя значение номиналов R1–R4, можно увеличить быстродействие за счет повышения потребляемой мощности. В табл. 3.1 приведены сравнительные параметры микросхем ТТЛ, демонстрирующие связь между потребляемой мощностью и быстродействием.

Таблица 3.1

| Серия ТТЛ | Параметр | Допустимая нагрузка | ||||

| Отечественная | Зарубежная | Рп, мВт | tср, нс | Эп, пДж | Сн, пФ | Rн, кОм |

| К131 | 74Н | 0,28 | ||||

| К155 | 0,4 | |||||

| К134 | 74L |

Существенно повысить быстродействие без наращивания мощности удалось введением в схему ТТЛ элементов с переходами Шоттки (диоды Шоттки, транзисторы Шоттки), в которых отсутствует эффект перезаряда диффузионной емкости, приводившей обычно в диодах

и транзисторах к задержке времени выключения. Эта серия получила название ТТЛШ. Эффект перехода на элементы Шоттки демонстрирует табл. 3.2.

Таблица 3.2

| Серия ТТЛШ | Параметр | Допустимая нагрузка | ||||

| Отечественная | Зарубежная | Рп, мВт | tср, нс | Эп, пДж | Сн, пФ | Rн, кОм |

| К531 | 74S | 0,28 | ||||

| К555 | 74Ls | 9/5 | ||||

| К1531 | 74F | 0,28 | ||||

| К1533 | 74als | 1.2 | 4.8 |

Совершенствование технологии и оптимизация решений ТТЛШ элементов привели к дальнейшему улучшению показателей (табл. 3.2, серии К1531, К1533). Другим направлением повышения быстродействия является применение обычных транзисторов, технология которых проще, чем технология элементов Шоттки, но работающих в ненасыщенном режиме и с управлением не током базы, а током эмиттера. Из теории биполярных транзисторов известно, что ток коллектора (в преобразовании Лапласа) можно представить или в функции тока базы

,

,

или тока эмиттера

,

,  .

.

Из известных соотношений для коэффициентов передачи тока эмиттера a и тока базы b

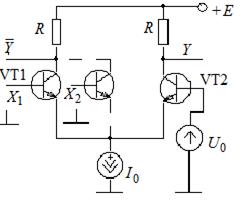

следует, что постоянная времени переходного процесса при управлении током эмиттера ta в (1 + b) раз меньше, чем при управлении током базы. Учитывая, что у современных транзисторов значение b составляет несколько десятков единиц, понятен эффект перехода на управление током эмиттера. Исключение же режима насыщения и связанной с ним задержкой выключения делает такой вариант построения логического элемента достаточно эффективным. Рассмотренные выше идеи реализованы в логических элементах типа ЭСЛ (эмиттерно-связанной логики), основой которых является токовый переключатель (рис. 3.8).

Рис. 3.8. Схема токового переключателя

Если входной сигнал Х имеет низкий уровень (меньше опорного напряжения U0), то VT1 заперт, VT2 – открыт и замыкает на себя весь ток генератора эмиттерного тока I0. На основном выходе при этом формируется сигнал низкого уровня, значение которого  не зависит от параметров транзистора, что позволяет не вводить транзистор в режим насыщения. При высоком уровне входного сигнала Х1(1)>U0 транзистор VT2 запирается и ток I0 замыкается через VT1. На основном выходе формируется высокий уровень Y(1)=E. Независимость Y(0) и Y(1) от параметров транзисторов позволяет сделать логический перепад Y(1) – Y(0) очень малым (порядка 0,8 В), что уменьшает время перезаряда паразитных емкостей. Поскольку значение переключаемого тока I0 не зависит от входного сигнала, транзисторы работают в режиме заданного тока эмиттера. Отсутствие насыщения, управление током эмиттера, низкий стабильный логический перепад обеспечивают чрезвычайно высокое быстродействие элементов ЭЛС, превосходящее даже быстродействие ТТЛШ. Так, элементы ЭЛС серии К1500 имеют следующие параметры: tср = 0,75 нс, Рп = 40 мВт, Эп = 30 пДж. Реальные элементы ЭСЛ имеют несколько входных транзисторов (см. пунктир на схеме рис. 3.8), снабжены выходными повторителями напряжения, обеспечивающими высокую нагрузочную способность. Для повышения помехоустойчивости в ЭСЛ коллекторные цепи заземлены (питание от отрицательного напряжения).

не зависит от параметров транзистора, что позволяет не вводить транзистор в режим насыщения. При высоком уровне входного сигнала Х1(1)>U0 транзистор VT2 запирается и ток I0 замыкается через VT1. На основном выходе формируется высокий уровень Y(1)=E. Независимость Y(0) и Y(1) от параметров транзисторов позволяет сделать логический перепад Y(1) – Y(0) очень малым (порядка 0,8 В), что уменьшает время перезаряда паразитных емкостей. Поскольку значение переключаемого тока I0 не зависит от входного сигнала, транзисторы работают в режиме заданного тока эмиттера. Отсутствие насыщения, управление током эмиттера, низкий стабильный логический перепад обеспечивают чрезвычайно высокое быстродействие элементов ЭЛС, превосходящее даже быстродействие ТТЛШ. Так, элементы ЭЛС серии К1500 имеют следующие параметры: tср = 0,75 нс, Рп = 40 мВт, Эп = 30 пДж. Реальные элементы ЭСЛ имеют несколько входных транзисторов (см. пунктир на схеме рис. 3.8), снабжены выходными повторителями напряжения, обеспечивающими высокую нагрузочную способность. Для повышения помехоустойчивости в ЭСЛ коллекторные цепи заземлены (питание от отрицательного напряжения).

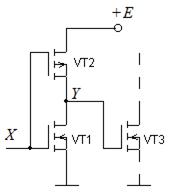

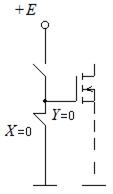

Особую ветвь в схемотехнике цифровых устройств занимают логические элементы, построенные на технологии МДП (МОП) структур, которые обладают целым рядом достоинств: oтсутствием эффекта насыщения в открытом состоянии, что, во-первых, исключает процессы задержки выключения, а во-вторых, позволяет обеспечить режим переключения в широком диапазоне питающих напряжений; oтсутствием входного тока; удобством управления потенциалом затвора; технологическая возможность выполнения на одном кристалле транзисторов с разным типом канала (комплементарные транзисторы) позволила создать логические элементы, не потребляющие энергию от источника питания в статическом состоянии. И хотя время задержки переключения, определяемое перезарядом паразитных емкостей через достаточно большие сопротивления открытых слаботочных транзисторов, может быть существенно выше, чем у ТТЛШ и ЭСЛ элементов, КМОП-логика широко используется как наиболее экономичная, а совершенствование технологии позволяет приблизить быстродействие КМОП к ТТЛШ. На рис. 3.9 приведена схема инвертора КМОП-типа.

Транзистор VT1 – n-канальный, VT2 – р-канальный. Напомним, что n-канальный транзистор открывается и принимает минимальное сопротивление при положительном напряжении, а р-канальный – при отрицательном напряжении затвор-исток.

а б в

Рис. 3.9. Схема КМОП-инвертора (а);

состояние высокого уровня (б);

состояние низкого уровня (в)

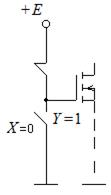

Запираются оба транзистора, при напряжении затвор-исток, близко к нулю. Транзистор VT3 является входным другого КМОП-элемента, являющегося нагрузкой для данного. При низком уровне входного сигнала [Х(0)<<Е] транзистор VT1 заперт, VT2 открыт, т. к. на его затворе положительное напряжение меньше, чем на истоке. На выходе формируется высокий уровень Y(1)=E (рис. 3.9, б). При высоком уровне входного сигнала [Х(1)=Е] транзистор VT2 заперт, т. к. его напряжение затвор–исток практически равно нулю, а VT1 – открыт и на выходе формируется низкий потенциал (рис. 3.9, в). При отсутствии тока нагрузки (входного тока VT3) потребление энергии от источника в любом случае из двух статических состояний отсутствует.

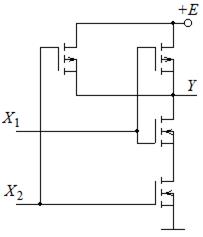

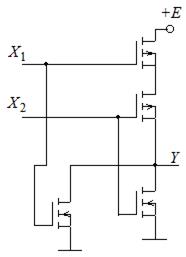

С использованием комплементарных пар можно строить как элементы И-НЕ, так и ИЛИ-НЕ (рис. 3.10).

а б

Рис. 3.10. Варианты КМОП элементов И-НЕ (а), ИЛИ-НЕ (б)

Дата добавления: 2016-06-22; просмотров: 7859;