Логические уровни, нагрузочная способность

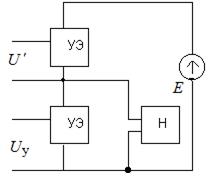

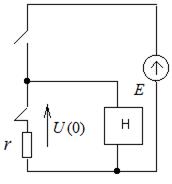

Как уже отмечалось ранее, наибольшее практическое применение находят логические элементы, содержащие выходные инверторы, которые наряду с выполнением логической операции НЕ являются формирователями логических уровней. Схема инвертора на обобщенном усилительном элементе УЭ приведена на рис. 3.1.

а б в

Рис. 3.1. Схема инвертора на обобщенном усилительном элементе:

а – схема простого инвертора; б – формирование высокого логического уровня;

в – формирование низкого логического уровня

В случае когда нагрузкой Н инвертора служат входные цепи однотипных логических элементов (направления токов нагрузки в режимах высокого и низкого уровней изображены на рис. 3.1 б, в), значение логических уровней, формируемых инвертором, определяется очевидными соотношениями

,

,  ,

,

где r – сопротивление усилительного элемента в открытом состоянии.

Поскольку U(1) и U(0) зависят от тока нагрузки, то при больших значениях последнего может произойти деформация логических уровней, когда

U(1)®U(0), U(0) ®U(1),

что недопустимо. Поэтому нагрузочная способность – допустимое число подсоединяемых входов однотипных логических элементов – является параметром, приводимым в сведениях о логическом элементе.

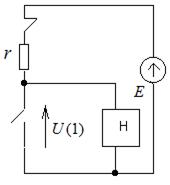

Сопротивление r открытого усилительного элемента минимизируется путем обеспечения достаточно высокого уровня управляющего сигнала (Uy, iy) УЭ. Снижение же сопротивления балансного резистора R с целью уменьшения влияния тока нагрузки на высокий уровень приведет к большим потерям мощности за счет увеличения тока iR. Поэтому инверторы с высокой нагрузочной способностью строятся по двухтактной схеме (рис. 3.2).

а б в

Рис. 3.2. Мощный инвертор:

а – схема; б – формирование высокого уровня; в – формирование низкого уровня

Дата добавления: 2016-06-22; просмотров: 2309;