Ограничители электрических сигналов

Четырехполюсник, на выходе которого напряжение uвых(t) остается практически неизменным и равным U0, в то время как входное напряжение uвх(t) может превышать или быть ниже какого-то наперед заданного напряжения Е, называется ограничителем.

|

Если uвх(t) > Е, то ограничение происходит сверху (рис. 19.19). Если uвх(t) < E', то ограничение происходит снизу (рис. 19.20). Если E < uвх(t) < E', то ограничение двустороннее (рис. 19.21). Если входной сигнал не превосходит по амплитуде пороговых уровней, то он должен воспроизводиться без искажений. Таким образом, ограничитель является нелинейным четырехполюсником, который в идеальном случае имеет идеально ломаные амплитудные характеристики ивых(t) = f[uвx(t)]. В качестве нелинейных элементов в ограничителях в основном применяют полупроводниковые диоды.

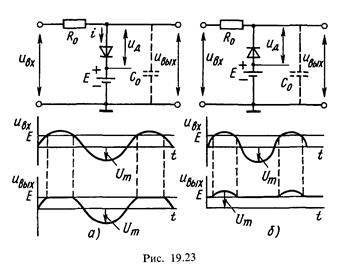

Рассмотрим ограничители на полупроводниковых диодах. В зависимости от способа включения диода различают последовательные (рис. 19.22, а, б) и параллельные (рис. 19.23, а, б) схемы ограничения электрических сигналов. На рис. 19.22 приведены также их временные диаграммы напряжений. Когда напряжение на аноде диода отрицательно, диод заперт и выходное напряжение uвых(t) ≈ Е, так как обратное сопротивление диода Rобр значительно больше сопротивления нагрузки R.

|

Если Uд > 0, то диод открыт и при условии, что прямое сопротивление диода Rд << R, напряжение на выходе почти равно входному. Следовательно, порог ограничения сигнала определен равенством нулю напряжения на диоде.

|

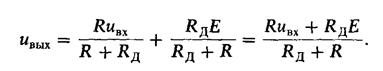

Если изменять значение и полярность напряжения источника постоянного напряжения Е, то можно в довольно широких пределах изменять уровень ограничения. Положим, что прямое сопротивление диода Rд мало зависит от температуры окружающей среды и постоянно, тогда для последовательного ограничителя справедливо следующее равенство:

(19.13)

(19.13)

Чем больше неравенство R >> Rд, тем точнее напряжение на выходе повторяет входное напряжение. Ограничением в выборе R является появление при высоких частотах паразитной емкости на выходе схемы (точки 2-2') емкости диода Сд и, как следствие, искажение формы импульса. Паразитные емкости (возможность их существования) показаны пунктиром на схемах рис. 19.22, а, б.

Диод выбирают, исходя из требований к обратному напряжению, значениям прямого тока и емкости Сд.

Схемы параллельных ограничителей и их временные диаграммы приведены на рис. 19.23, а, б. При открытом диоде выходное напряжение uвых(t) мало отличается от Е, если попрежнему выполняется условие Rд << R0, где R0 — сопротивление, ограничивающее ток в цепи при открытом диоде. Для схемы рис. 19.23, а справедливо следующее выражение:

(19.14)

(19.14)

При Rд/R0 << 1 можно считать, что напряжение на выходе uвых = E.

При запертом диоде выходное напряжение почти повторяет входное, так как Ro6p >> R0. Как и в последовательной схеме, уровень ограничения в параллельном диодном ограничителе определяется напряжением Е.

В параллельных ограничителях, схемы которых подобны представленным на рис. 19.23, а, б, также проявляются паразитные емкости С0 (пунктир на рисунке), особенно на высоких частотах. Поэтому для сокращения длительности фронта импульса следует значение ограничивающего сопротивления R0 выбирать не слишком большим.

Отметим, что параллельный ограничитель на диоде обеспечивает худшую по сравнению с последовательным ограничителем четкость ограничителя, так как в параллельной схеме четкость ограничения опре

деляется отношением Rд/R0, а в последовательной — отношением Roбp/R. Однако Rобр > R и неравенство Rобр >> R реализуется на практике легче, чем Rд << R0. К недостаткам параллельных ограничителей относится и то, что в этом случае источник Е должен иметь малое собственное внутреннее сопротивление.

Схема рис. 19.23,б тоже имеет недостаток: на высоких частотах и при крутых перепадах напряжения дифференциальная емкость р-n-пере-хода создает в режиме ограничения (диод заперт) паразитную связь между входом и выходом.

Двустороннее ограничение напряжения рассмотрим на примере применения операционного усилителя в качестве активного ограничивающего прибора. Схемное решение приведено на рис. 19.24, а, а временные диаграммы — на рис. 19.24, б. Ограничение напряжения происходит следующим образом: до тех пор, пока выходное напряжение uвыx(t) по абсолютному значению не превысит сумму напряжения стабилизации uст одного из стабилитронов, например Д2 (на временной диаграмме Uст2) и прямого падения напряжения на другом стабилитроне Д1 (uпр1), устройство работает как обычный инвертирующий усилитель с коэффициентом усиления по входу, равным отношению R2/R1. Если же наступает неравенство uвых(t) > uст2 + uпр1, стабилитрон Д2 пробьется и напряжение будет ограничено на уровнях uпрl и uст2.

Дата добавления: 2018-11-26; просмотров: 741;