ИЗМЕРИТЕЛЬНЫЕ ОРГАНЫ (РЕЛЕ) С ДВУМЯ, ВХОДНЫМИ ВЕЛИЧИНАМИ НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМА.

К этой группе ИО относятся реле направления мощности (РНМ) и реле сопротивления (РС), входными величинами которых являются напряжение и ток защищаемого объекта (UP и IP).

Для построения РНМ на ИМС используется в основном принцип сравнения фаз двух входных величин (UI и UII), позволяющий получить большее быстродействие, чем у реле, построенных на сравнении абсолютных значений. Ниже рассмотрены реле серии РМ-11 и РМ-12, выпускаемые ЧЭАЗ вместо индукционных реле типов РБМ-171 и РБМ-177. Новые РНМ типа РМ-10 изготовляются из отдельных транзисторов и ИМС (ОУ). В основу работы реле положена схема сравнения фаз двух синусоидальных напряжений u1t = k1Upmsin(ωt + φ) и u2t = k2Upmsin(ωt + φ), построенная на сопоставлении времени совпадения tСП однополярных мгновенных значений этих напряже- ний с заданным временем совпадения (уставкой) tУ, при котором реле должно срабатывать. В § 2.18 показано, что значение tHC, определяется сдвигом фаз ψ между сравниваемыми напряжениями.

Параметры элементов схемы подобраны так, чтобы реле начинало действовать, если время совпадения превышает четверть периода промышленной частоты, т. е. если tСП > tУ. В данном реле это соответствует сдвигу фаз между UI и UII, равному 90o.

Особенностью фазосравнивающей схемы реле РМ-10 является разделение ее на две параллельные части – два канала прохождения сигналов сравниваемых напряжений. В одном измеряется время совпадения положительных значений UI и UII, а в другом отрицательных мгновенных значений этих же напряжений. Такое разделение с последующим суммированием выходных сигналов обоих каналов устраняет влияние апериодической составляющей.

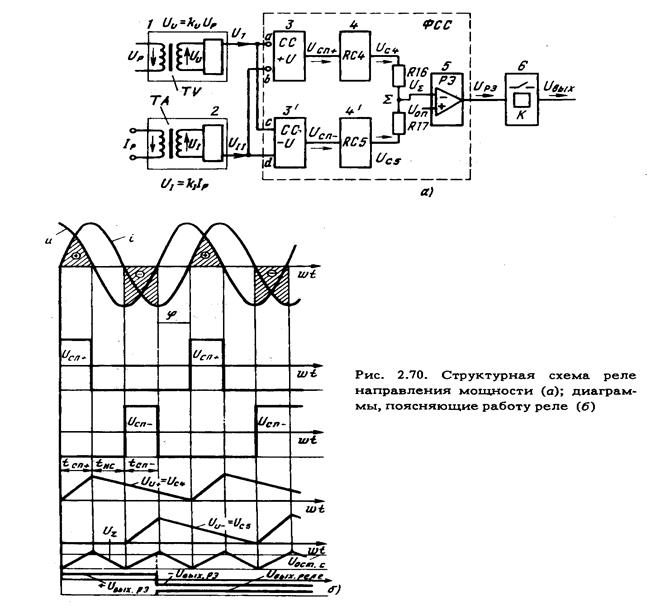

Рассмотрим структурную схему реле, показанную на рис. 2.70,а. Напряжение UP и ток IP от ТТ и ТН поступают на вход блоков 1 и 2, являющихся промежуточными преобразователями напряжения и тока. В блоках 1 и 2 входные сигналы преобразуются в пропорциональные им напряжения UU = kUUP и UI = kIIP, а затем напряжение UU, сдвигается по фазе относительно вектора UP с помощью фазоповоротной схемы на некоторый постоянный угол α, а UI проходит через фильтр, снижающий уровень высших гармоник. Сдвиг по фазе напряжения UU относительно UP обеспечивает получение требуемого угла максимальной чувствительности ψМ.Ч и угловой характеристики срабатывания реле. В результате указанных преобразований на выходе блока 1 появляется напряжение UI, а блока 2 – UII.

Выходные напряжения UI = UU – ejα = k1UP и UII = k2IP блоков 1 и 2 поступают на блоки 3 и 3' фазосравнивающей схемы (ФСС). Блок 3 выявляет и фиксирует совпадение мгновенных значений UI и UII положительного знака, а блок 3 – тех же напряжений отрицательного знака. В интервале времени совпадения мгновенных значений UI и UII положительной полярности на выходе блока 3 появляется напряжение UСП+ прямоугольной формы, а при совпадении отрицательных значений такое же по форме и амплитуде напряжение UСП– появляется на выходе блока 3 (рис. 2.70, б).

Каждый из сигналов (UСП+ и UСП–) поступает на блоки 4 и 4', которые являются интеграторами. Они выполняются в виде цепей RС4 и RС5 с одинаковыми значениями R и С. По мере заряда конденсаторов С4 и С5 на выходе соответствующего интегратора появляются напряжения UU+ = UC4 на 4 и UU– = UC5 на 4'. Значения UU+ и UU– пропорциональны длительности положительных и отрицательных сигналов совпадения UU+ ≡ tСП+, а UU– ≡ tСП–. Каждое из этих напряжений нарастает на обкладках конденсаторов С интеграторов 4 и 4' по экспоненте, имеющей в начальной части линейный характер. После исчезновения напряжения, фиксирующего совпадение входных величин (UU+ и UU–), конденсатор интегратора разряжается.

С интеграторов оба напряжения приходят на вход аналогового сумматора (R16, R17), где происходит их сложение. Напряжения UU+ и UU–, как и результирующее напряжение UΣ, равное их сумме, имеют пилообразный характер (рис. 2.70, б).

С выхода сумматора результирующее напряжение UΣ подводится к блоку 5 – реагирующему элементу РЭ фазосравнивающей схемы ФСС, который выполняется в виде порогового компаратора релейного действия триггера Шмитта. Триггер срабатывает при появлении на его входе напряжения UΣ = UОП, значение которого соответствует продолжительности времени совпадения tСП ≥ 0,005 с (что имеет место, когда сдвиг фаз между UI и UII равен 90о). При этом условии UΣ ≥ UОП порога триггера, и на выходе РЭ появляется сигнал отрицательного знака UВЫХРЭ = – UMAX. Этот сигнал поступает на транзисторный усилитель 6, под действием которого промежуточное реле усилителя К срабатывает и замыкает контакт.

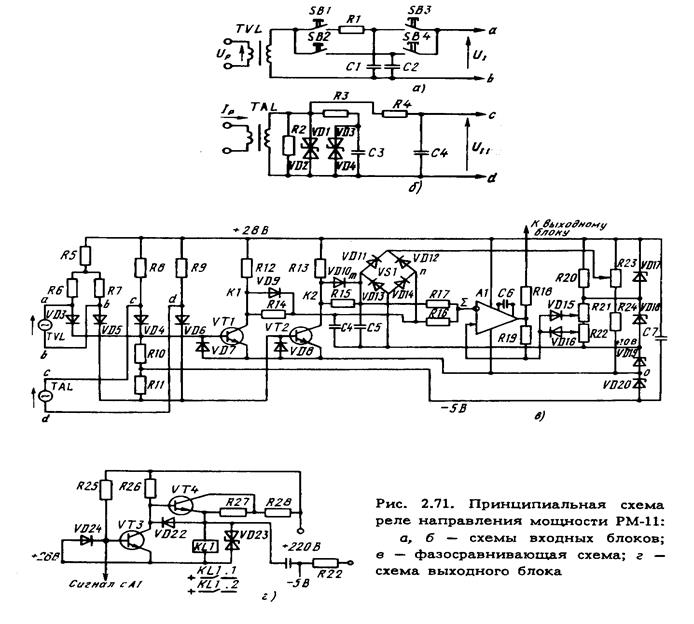

Принципиальная фазосравнивающая схема реле РМ-11 приведена на рис. 2.71, в. Реле типа РМ-12 отличается от приведенной схемы только в части схемы блоков 1 и 2, поскольку оно имеет регулировку чувствительности и другой φМ.Ч. Схема блока 1 (рис. 2.71, а) состоит из промежуточного трансформатора напряжений (ТVL) и двух фазосдвигающих контуров R1, С1 и С2, подключаемых ко вторичной обмотке ТVL переключателями SВ1, SВ3 или SВ2, SВ4. Трансформатор ТVL преобразует UP (блок 1) в пропорциональное ему напряжение kUP требуемого уровня, а фазосдвигающие контуры обеспечивают получение одного из двух заданных значений угла максимальной чувствительности φМ.Ч = – 35o (при замыкании SВ1, SВ3) и φМ.Ч = – 45o (при замыкании SВ2 и SВ4). Преобразователь тока IP (блок 2) состоит из промежуточного трансформатора тока (ТАL), замкнутого на R2 (рис. 2.71, б). Напряжение UP на зажимах R2 пропорционально току IP и совпадает с ним по фазе. К ТАL. подключены: стабилитроны VD1 и VD2, ограничивающие напряжение на R2 при больших токах IP; контур R3, С3, VD3, VD4, осуществляющий коррекцию φМ.Ч при искажении формы вторичного напряжения ТАL; контур R4, С4, отфильтровывающий высшие гармоники в токе IP.

В результате преобразования входных величин IP и UP на выходе блока 1 появляется напряжение UI, а блока 2 – UII. Эти напряжения поступают на ФСС (рис. 2.71, в), который осуществляет фиксацию совпадения знаков сравниваемых напряжений UI и UII, измерение времени их совпадения tСП и сравнение его с заданным значением.

Схему можно разделить на три части. Первой частью ФСС является схема, фиксирующая совпадение знаков мгновенных значений UI и UII. Она выполнена на транзисторах VT1 и VТ2, диодах VDЗ-VD6, резисторах R6-R9. Диоды VD3-VD6 исполняют функции ключа, пропускающего на базы VТ1 и VТ2 управляющие их работой сигналы положительного знака, уровень которых зависит от сопротивлений R6-R9. Выходные сигналы схемы совпадения знаков сравниваемых напряжений UI и UII снимаются с коллекторов транзисторов VТ1 и VТ2 в точках К1 и К2 и поступают на вторую часть ФСС – интеграторы (блоки 4 и 4' на рис. 2.70, а), фиксирующие длительность совпадения знаков сравниваемых величин tСП. Интегратор, получающий сигнал с коллектора VТ1, состоит из С4, R12, R14, VD9. Интегратор, связанный с коллектором VТ2, состоит из С5, R13, R15, VD10.

К выходу интеграторов (в точках m и n) подключен диодный мост VS1, ограничивающий уровни напряжений, снимаемых с конденсаторов С4 и С5. Выходные сигналы интеграторов UC4 и UC5 поступают на суммирующие сопротивления R16 и R17 аналогового сумматора. Суммарное напряжение UΣ, снимаемое со средней точки сумматора, поступает на третью часть ФСС – инвертирующий вход порогового компаратора А1 с положительной ОС (ПОС) (триггер Шмитта на ОУ). Обратная связь триггера А1 выполнена на делителе напряжения из R19, R21, R22 и диодах VD15 и VD16. В качестве порогового напряжения срабатывания UОП.С, и возврата UОП.В триггера на Н-вход ОУ подается напряжение, снимаемое с R21 и R22. Диоды VD15 и VD16 разделяют цепи срабатывания и возврата.

Выход триггера ОУ связан с выходным блоком (усилителем), состоящим из транзисторов VТЗ, VТ4 и промежуточного реле типа РП-13 или геркона РПГ-5 (КL1) (рис. 2.71,г). Реле KL1 срабатывает при появлении на выходе триггера А1 сигнала отрицательного знака, означающего, что РНМ сработало.

Фазосравнивающая схема и схема выходного блока питаются от стабилитронного делителя, включенного между плюсом и минусом напряжения постоянного тока 220 или 110 В: на делителе имеются ответвления ± 28, + 10, -5 и 0 В. Предусмотрена возможность использования в качестве источника питания выпрямленного напряжения, получаемого с помощью комбинированного блока питания, включаемого на напряжение и ток сети.

Работа элементов ФСС.При появлении входных сигналов UP и IP на входе схемы совпадения ФСС появляются сравниваемые напряжения UI и UII. Поведение транзисторов VT1 и VT2 будет определяться состоянием диодов VD3-VD6, через которые на базы транзисторов поступает управляющий сигнал с полярностью входных сигналов UI и UII, приходящих на анодный вход диодов в точках а и b, с и d

При положительной полуволне входного сигнала, например U1, один вход источника сигнала (связанный с точкой b) в течение этого полупериода будет иметь положительный потенциал (+), потенциал второго входа а (относительно первого) будет отрицательным (-) (рис. 2.71,в). При указанной полярности во время положительной полуволны диод VD5 будет открыт и через него на базу VТ2 пройдет сумма двух положительных сигналов: от источника входного сигнала + U1 и от источника питания +ЕП. диод VD3 будет заперт, так как точка а имеет отрицательный потенциал, под действием которого VТ1 закрыт.

Аналогично при положительной полярности UII (с учетом стрелки на рис. 2.71, б), показывающей направление положительного напряжения UII, точка d связана с входом, имеющим положительный потенциал, поэтому диод VD6 будет открыт и пропустит суммарный положительный сигнал на базу транзистора VТ2, под действием которого он будет открыт. Точка с связана с входом, имеющим отрицательный потенциал, следовательно, диод VD4 закрыт.

Под действием отрицательного напряжения смещения (-SB) транзистор VТ1 будет закрыт. Следовательно, при совпадении положительных знаков мгновенных значений UI и UII один транзистор VТ2 будет полностью открыт положительным напряжениям, поступающим на его базу через диоды VD5 и VD6, а второй транзистор VТ1 будет заперт.

При совпадении сравниваемых сигналов отрииательного знака стрелки, обозначающие полярность напряжений UI и UII, будут направлены противоположно показанным на рис. 2.71, в, соответственно изменится полярность точек а, b, с, d. В результате этого транзистор VT1 откроется, а VТ2 закроется. Таким образом, при совпадении знаков сравниваемых напряжений (UI и UII) во время положительных полуволн закрыт транзистор VТ1 и открыт VТ2, а во время отрицательных полуволн VТ2 закрыт, VТ1 открыт.

При различной полярности сравниваемых входных сигналов оба транзистора будут открыты одновременно, при этом их выходные сигналы (напряжения на коллекторах) равны нулю.

Во время одновременного открытия обоих транзисторов реле не должно работать, а при поочередном открытии VТ1 и VТ2 (одного – при совпадении положительных знаков UI и UII, а второго – отрицательных) реле должно сработать, если продолжительность совпадения соответствует заданной (tСП = t3), значение t3, определяется порогом срабатывания U0 триггера А1.

Выходной сигнал схемы совпадения в виде напряжения UK1 и UK2, снимаемого с коллекторов VТ1 и VТ2, приходит на интеграторы, измеряющие продолжительность сигналов: UK1 – совпадения сигналов положительного знака, UK2 – отрицательного.

Работа интеграторов. Когда знаки сравниваемых напряжений совпадают, один из транзисторов будет закрыт и его выходное коллекторное напряжение в точке K1 (или К2) близко к напряжению ЕП источника питания. В этом режиме выходное напряжение закрытого транзистора, поступившее на соответствующий интегратор, начинает заряжать его конденсатор. Допустим, что совпадают положительные значения UI и UII и закрыт транзистор VТ1. Тогда под действием UK1 заряжается С4 током, проходящим по контуру, образованному R12, через точку К1 и открытый диод VD9. В это же время через второй открытый транзистор VТ2 начинается разряд С5, поскольку напряжение коллектора открытого транзистора UK2 ≈ 0. Ток разряда противоположен току заряда (разряд происходит по контуру R15, VТ2, нулевая шинка, шинка + 10 В, нижняя обкладка конденсатора С5). Напряжение UC4 на заряжающемся конденсаторе С4 нарастает, его конечное значение зависит от времени совпадения tСП знаков UI и UII в течение каждого полупериода промышленной частоты: UC4 ≡ tСП.

Напряжение на разряжающемся С5 снижается, его конечное значение в пределах полупериода также зависит от tСП : UC5 ≡ – 0,5Т – tСП (рис. 2.70, б).

После прекращения совпадения положительных полуволн VТ1 снова открывается, С4 начинает разряжаться через R14 и открытый VТ1, диод VD9 в этом режиме закрыт.

При совпадении по времени отрицательных полуволн UI и UII транзистор VT2 закрывается, С5 заряжается через R15 и диод VD9 (рис. 2.71, в). Заряд и разряд С4, С5 происходит по экспоненциальному закону, но в начальной части экспонента имеет линейный характер, поэтому на диаграмме рис. 2.70, б характер изменения UC4 и UC5 показан в виде прямых линий.

Выходное напряжение интеграторов UC4, UC5 приходит на сумматор из R16 и R17 и с их общей точки Σ поступает на интегрирующий вход А1 триггера Шмитта. Сопротивление R16 = R17, поэтому суммарное напряжение точки Σ равно полусумме напряжений конденсаторов UΣ = 0,5(UC4 + UC5).

Пока напряжение UΣ, поступающее на И-вход А1, меньше опорного напряжения, установившегося на Н-входе (UОП.С = UR21), на выходе А1 остается неизменным напряжение положительной полярности UвыхА1 = + Umax. Опорное напряжение выбирается так, чтобы реле начинало работать при сдвиге фаз ψ между UI и UII, равном 90o, чему соответствует время совпадения, равное четверти периода промышленной частоты, т. е. tСП = 0,005 с. При сдвиге фаз ψ = 90o, но меньше 270o, напряжение на И-входе становится равным или больше опорного: UΣ ≥ UОП. При достижении этого уровня триггер А1 переключается, и на его выходе вместо положительного сигнала появляется UвыхА1 = – Umax, имеющее отрицательный знак. Это напряжение поступает на базу транзистора VТ3 выходного блока (рис. 2.71, г), транзистор закрывается и дешунтирует обмотку (реле) KL1, оно срабатывает и подает командный выходной сигнал о действии РНМ.

После срабатывания А1 и появления на его выходе напряжения отрицательной полярности UMAX диод VD15 закрывается (рис. 2.71, в), а VD16 открывается. В результате этого на Н-входе появляется новое пороговое напряжение UR22. Это напряжение определяет уровень напряжения на И-входе, необходимого для возврата триггера А1 в исходное состояние. Пороговое напряжение возврата UОП.В выбирается ниже UОП.С чтобы обеспечить непрерывность выходного сигнала А1, когда входной сигнал UΣ пилообразной формы близок к напряжению срабатывания UОП.С.

Ограничитель напряжения. При заряде С4 и С5 (рис. 2.71, в) уровень напряжения между их обкладками (UC4, UC5) зависит от значения tСП и будет наибольшим при ψ = 0, т. е. когда фазы UI и UII совпадают, а сдвиг фаз между UP и IP равен φМ.Ч (в этом случае tСП = 0,5 периода). Для ограничения роста напряжения UC используется мост VS1. Напряжения UC4 и UC5 подаются на точки m и n моста (рис. 2.71, в). Два других зажима моста подключаются: один – к шинке +10 В, второй – к резистору 223. Попустим, что идет заряд С4. Пока UC4 мало, диоды VD11 и VD12 моста VS1 заперты положительным напряжением U23, поступающим с R23, – это напряжение является предельным UОГР ограничивающим верхнее значение UC4. Как только нарастающее напряжение UC4 достигает уровня UОГР = UR23, диод VD12 моста открывается и рост напряжения на С4 останавливается на уровне UC4 = UОГР + UД, где UД – падение напряжения в открытом диоде. Аналогично происходит ограничение UC5 на конденсаторе С5 с помощью диода VD11. Ограничитель VS1 используется в схеме реле и при разряде конденсаторов для ограничения минимального уровня. Как видно из схемы (рис. 2.71, в), нижняя обкладка конденсаторов С4 и С5 жестко соединена с шинкой +10 В, а верхняя связана с точками m и n диодного моста. При полном открытии одного из транзисторов схемы совпадения, например VТ1, на конденсаторе С4 появится напряжение UK1 = 0, и он начнет разряжаться. Тогда диод VD14 моста VS1 откроется и зашунтирует С4, так как анодный вход диода VD114 соединен с шинкой +10 В, а точка и моста получила нулевой потенциал. Следовательно, предельным уровнем напряжения при разряде С4 будет падение напряжения в открытом диоде VD14, взятое с обратным знаком.

При разряде С5 предельным значением UC5 будет падение напряжения в открытом диоде VD13, взятое с обратным знаком.

Основными параметрами реле РМ-11 являются: время срабатывания при φ = φМ.Ч = 30 мс; чувствительность UP.CP = 0,25 В; ток срабатывания ICP = 0,25IHOM, потребление цепи переменного тока SЦ.Т = 0,15 В • А, переменного напряжения SЦ.H = 01 В • А, цепей оперативного тока SO.T = 10 Вт.

Дата добавления: 2020-10-25; просмотров: 709;