Построение управляющего автомата

На первом этапе курсовой работы необходимо построить операционное устройство. Но чтобы проверить правильность его работы, необходимо иметь последовательность управляющих сигналов, подаваемых на входы элементов ОУ в каждом такте. Для этого создадим модель управляющего автомата.

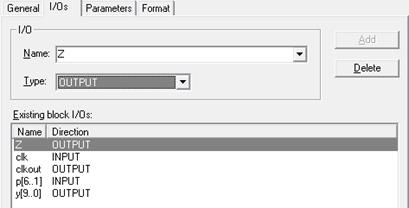

Выберите на панели инструментов элемент Block.  . Далее правой кнопкой мыши вызовите контекстное меню и выберите пункт Block Properties>Вкладка I/Os. Укажите наименования входов и выходов, а также их тип. Затем присоедините следующие линии связи к блоку (рисунок 47).

. Далее правой кнопкой мыши вызовите контекстное меню и выберите пункт Block Properties>Вкладка I/Os. Укажите наименования входов и выходов, а также их тип. Затем присоедините следующие линии связи к блоку (рисунок 47).

Рис. 47. Формирование сигналов блока УА

Рис. 48. Вид блока УА в Quartus (б)

Наведите курсор на “зеленые стрелочки” и кликните правой кнопкой мыши (рисунок 48). Выберите свойство Mapper Properties. На вкладке General укажите Type = INPUT или OUTPUT (в зависимости от типа сигнала). На вкладке Mappings поставьте соответствие между сигналом шины и входом блока. Нажмите Add, затем ОК. Повторите операцию для всех остальных линий связи, соединенных с данным блоком (рисунок 49).

|

Рис. 49. Окно Mapper Properties

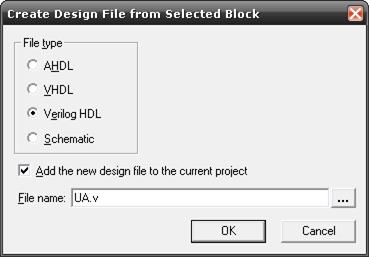

Выделите блок. Правой кнопкой мыши в контекстном меню выберите Create Design File from Selected Block…Укажите имя файла и его тип (рисунок 50). Нажмите ОК.

Рис. 50. Создание файла микропрограммы УА

Далее правой кнопкой мыши вызовите контекстное меню, выберите пункт Open Design File. В этом файле с помощью языка описания аппаратуры Verilog Вам предстоит написать микропрограмму работы вашего управляющего автомата.

Идея заключается в следующем. Управляющий автомат срабатывает по положительному фронту синхросигнала. Операционный автомат срабатывает по положительному фронту сигнала clkout, который выдается управляющим автоматом и является инверсией внешнего синхросигнала. Граф-схема алгоритма делится на такты. В каждом такте проверяются определенный набор условий, значения которых задают осведомительные сигналы, поступающие из ОУ. В соответствии с условиями, на выходе управляющего автомата выдаются определенная последовательность управляющих сигналов. Затем осуществляется переход к следующему такту.

Когда Вы откроете файл, то вся микропрограмма должна располагаться после строчек

// {{ALTERA_IO_BEGIN}} DO NOT REMOVE THIS LINE!

input clk;

input [6:1] p;

output clkout;

output Z;

output [9:0] y;

// {{ALTERA_IO_END}} DO NOT REMOVE THIS LINE!

//Ваша микропрограмма

endmodule

Пример микропрограммы.

integer pc=1; //Объявление счетчика тактов, переменная типа integer

reg [9:0] y; //Объявление регистра для хранения массива управляющих сигналов

wire clkout; //Объявление проводника clkout

reg Z=0; //Объявление регистра для хранения признакак окончания операции

assign clkout=!clk; //clkout является инвертированным сигналом clk, указываем, как система должна вычислять значение clkout

always @(posedge clk) //Данная функция срабатывает при положительном (pos) перепаде (edge) сигнала clk (по фронту)

begin

case (pc)

1:begin //что выполняется на первом такте

y=10'b0000000011;; //число «10» указывает на количество управляющих сигналов, «b» указывает на то, что данные бинарные, «1» указывает на то, что на этом такте УА вырабатывает данный управляющий сигнал

pc= pc + 1; //переход на след такт

end

2:begin //что выполняется на втором такте

if (p[1]==0) begin //проверка значения осведомительных сигналов «!» - символ отрицания; «&» – логическое И

y=10'b0000000100;

pc = pc + 1; end

else begin //иначе…

y=10'b1000000010;

pc=9; end //переход к такту 9

end

…

end

default y=10'b000000000; //что выполнять, если тактов больше 9

endcase;

end

endmodule

После этого, проект необходимо скомпилировать (Ctrl+L). Если ошибок не возникло, то операционный автомат готов к работе.

Прежде чем открывать схему в программе для проверки работоспособности ОА, необходимо все выводы схемы (элементы input и output) назвать соответствующим образом (это улучшит производительность и процесс исследования схемы):

x[15..0] – входные данные (размерность шины постоянна и составляет 16 разрядов);

clk или c – сигнал синхронизации;

result[15..0] – выходные данные (размерность шины постоянна и составляет 16 разрядов);

y[n..0]– управляющие сигналы (разрядность шины согласно разработанной схеме);

p[m..0]– осведомительные сигналы (разрядность шины согласно разработанной схеме);

Z – признак окончания операции;

PRS– признак ПРС;

PMR – признак ПМР;

DEL – признак деления на ноль;

RESET – сброс УА (при построении объединенной схемы).

Для того, чтобы процесс назначения выводов в программе был проще и быстрее, рекомендуется для дополнительных выводов (значения выходов сумматоров, регистров, счетчиков) задавать имена (для элементов output), оканчивающиеся словом «out» (рисунок 51).

Рис. 51. Дополнительные выводы

Дата добавления: 2022-02-05; просмотров: 460;