Разработка функциональной схемы операционной части АЛУ

Разработка функциональной схемы заключается в выборе конкретных функциональных элементов и соединений.

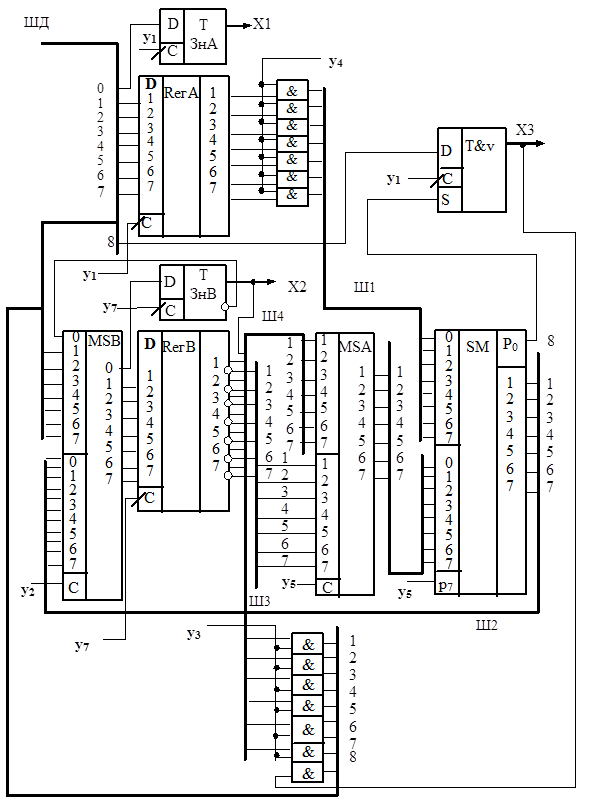

Функциональная схема представлена на рис. 7.3.

Входами схемы являются линии шины управляющих сигналов: y1 – y7 (семь линий) и линия кода операции (на вход триггера кода операции/переполнения) из схемы УЧ АЛУ.

Кроме этого, схема использует магистральную двунаправленную шину данных (семь разрядов числа и знак).

Функции триггера кода операции и триггера признака переполнения объединяются в одном триггере кода операции/переполнения (Тa/v). Это допустимо, так как код операции используется только в первых тактах, а признак переполнения только на последних тактах выполнения операции.

Анализ структурной схемы и графа микропрограммы показывает, что для построения схемы требуется:

· Два семиразрядных регистра на D-триггерах. Один из них должен иметь как прямые, так и инверсные выходы. Этот регистр (РегВ) предназначен для приема семи разрядов (с первого по седьмой) второго операнда. Второй регистр (РегА) может не иметь инверсных выходов. Он предназначен для хранения разрядов первого операнда. Для хранения результата можно использовать один из этих регистров.

· Два D-триггера для приема и хранения знаков операндов. Один из них должен иметь инверсный выход для реализации инвертирования знака результата при коррекции.

· Комбинационный семиразрядный сумматор (SM) с выходом переноса из старшего разряда SM(p1) и входом переноса на младший разряд SM(р7).

· Семиразрядный мультиплексор MSA на два входа для коммутации входов сумматора SM(В) на прием разрядов второго операнда (или результата) в прямом или дополнительном кодах.

Рис. 7.3. Функциональная схема операционной части устройства алгебраического сложения/вычитания восьмиразрядных целых чисел со знаком в прямом коде.

· Семиразрядный мультиплексор MSB на два входа для коммутации входов регистра второго операнда/результата (РегВ) на прием второго операнда с шины данных (ШД) или с выхода сумматора.

· Семиразрядную схему И для разъединения выходов регистра первого операнда с входами сумматора на время коррекции результата.

· Восьмиразрядную схему И (на схеме рис.1 обозначена как точка управления с входящей стрелкой) для разъединения выходов регистра результата (со знаком) с магистральной шиной данных.

· Синхронный D-триггер с входом сброса для фиксации кода операции в начале операции и хранения переноса с сумматора в такте суммирования.

Вопросы для самопроверки

1. Определите этапы проектирования операционной части АЛУ.

2. Определите понятие структурной схемы.

3. Определите понятие функциональной схемы.

4. Определите понятие принципиальной схемы.

5. Определите понятие графа микропрограммы.

Дата добавления: 2022-02-05; просмотров: 477;