Схемы умножения целых чисел в прямом коде

Умножение в прямом коде – это умножение абсолютных значений сомножителей и вычисление знака произведения. Произведению присваивается знак плюс, если знаки сомножителей совпадают, и минус, если знаки не совпадают.

Произведение чисел без знака А и Вможно записать в виде:

А´В=А´(bn 2n + bn–1 2n-1 + …+ b1 2 + b0), где b – двоичная цифра числа В.

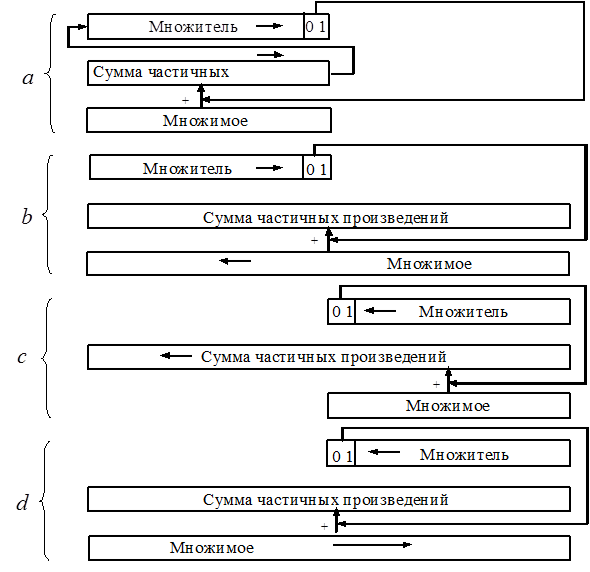

Умножение числа А на 2n равносильно сдвигу числа А вправо на n разрядов. Таким образом, умножение в двоичной системе сводится к последовательности сдвигов множителя и сложению его с частичным произведением, при единичном значении соответствующей разрядной цифры множителя. Начальное значение частичного произведения устанавливается нулевым, после выполнения всех сложений оно равно произведению А на В. Сдвиг множителя производится относительно частичного произведения. Здесь возможны четыре варианта схем умножения:

· умножение с младших разрядов множителя и сдвиг частичных произведений вправо (вариант схема а на рис. 5.2.),

· умножение с младших разрядов множителя и сдвиг множимого влево (вариант схема b на рис. 5.2.),

· умножение со старших разрядов множителя и сдвиг частичных произведений влево (вариант схема c на рис. 5.2.),

· умножение со старших разрядов множителя и сдвиг множимого вправо (вариант схема d на рис. 5.2.).

При умножении n-разрядных чисел результат формируется 2n-разрядный.

Умножение по схеме a использует три n-разрядных регистра. При этом сдвигаемые вправо разряды суммы частичных произведений принимаются в освобождаемые разряды множителя. Эта схема требует минимального оборудования и часто используется в ЭВМ.

Схема b не имеет никаких преимуществ по сравнению с а и практически не используется.

Рис. 5.2. Схемы выполнения умножения

Схема с использует сумматор и регистр суммы частичных произведений двойной разрядности и по оборудованию уступает схеме а. Но она позволяет выполнять и операцию деления без использования дополнительных цепей сдвига. Поэтому она имеет свою практическую ценность.

Схема d использует сумматор и два регистра удвоенной разрядности, но она, как и схема d, позволяет выполнять и операцию деления без использования дополнительных цепей сдвига. Кроме этого, при умножении дробных чисел обычно производится округление результата. В этом случае, младшие разряды сумматора, регистра частичных произведений и множимого можно сократить до n +1 разряда. Поэтому эта схема также имеет свою практическую ценность.

Если ориентироваться на использование только специализированных устройств умножения, то схема по варианту "а" а является наиболее предпочтительной.

Пример. Умножение целых чисел в прямом коде по схеме а (умножение с младших разрядов множителя со сдвигом частных произведений вправо).

А = 7(10) =SignA ½111(2)½ – множимое.

В = 5(10) =SignВ ½101(2)½ – множитель.

С – произведение.

При умножении числа А и В рассматриваются как числа без знаков. Знак произведения определяется отдельно. Знак произведения будет положительным, если знаки сомножителей совпадают. Положительное значение произведения определяется по совпадению знаков сомножителей. При умножении n-разрядных чисел разрядность результата не превышает 2n, но возможен перенос из старшего разряда сумматора при вычислении сумм частичных произведений. Для его сохранения регистр суммы сумм частичных произведений должен иметь дополнительный разряд.

В примере разряды суммы частичных произведений отделены от дополнительного разряда пробелом, а от разрядов множителя – вертикальной чертой.

| Множимое А (3 бита) | Произведение С (4 бита) | Множитель В (3 бита) | Комментарии |

| 0 000 | ½101 | Исходное состояние. | |

| 0 000 0 111 0 111 | ½101 | Анализ младшего бита множителя (1) и прибавление множимого к сумме частичных произведений | |

| 0 011 | 1½10 | Сквозной сдвиг суммы частичных произведений и множителя вправо на один разряд. | |

| 0 011 0 000 0 011 | 1½10 | Анализ младшего бита множителя (0) и блокировка прибавления множимого к сумме частичных произведений. | |

| 0 001 | 11½1 | Сквозной сдвиг суммы частичных произведений и множителя вправо на один разряд. | |

| 0 001 0 111 1 000 | 11½1 | Анализ младшего бита множителя (1) и прибавление множимого к сумме частичных произведений | |

| 0 100 | 011½ | Сквозной сдвиг суммы частичных произведений и множителя вправо на один разряд. |

Результат С =0,100011(2) = 35(10).

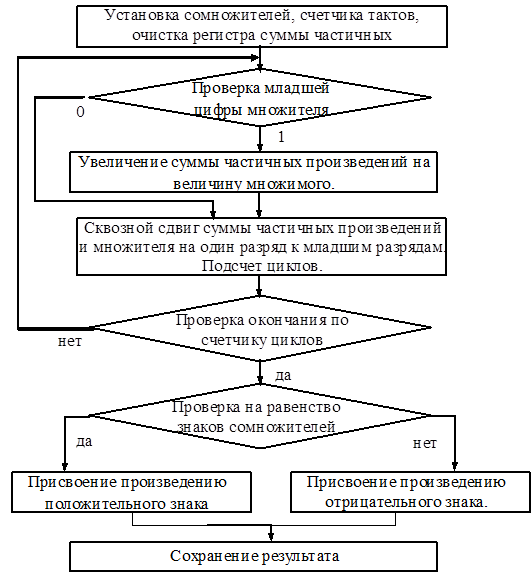

Блок схема алгоритма выполнения умножения целых чисел в прямом коде по схеме а (умножение с младших разрядов множителя со сдвигом частных произведений вправо) представлена на рис. 5.3.

Рис. 5.3. Блок схема алгоритма выполнения умножения целых чисел в прямом коде по схеме а (умножение с младших разрядов множителя со сдвигом частных произведений вправо).

Дата добавления: 2022-02-05; просмотров: 859;