Типовые структуры и функциональные узлы

Микросхем памяти

Для характеристики микросхемы памяти как функционального узла электронной аппаратуры необходимо знать, прежде всего, режимы работы, сигналы управления, способы сопряжения с другими функциональными узлами в аппаратуре, систему электрических параметров и их значения.

Обобщенная структурная схема запоминающего устройства, характерная для ОЗУ и ПЗУ, представлена на рис. 12.4. Она включает следующие функциональные узлы: накопитель, дешифратор кода адреса (ДШ), устройство ввода-вывода (УВВ), устройство управления (УУ).

Накопитель представляет собой совокупность элементов памяти, объединенных в матрицу. В матрице ЭП размещены на пересечениях горизонтальных и вертикальных проводников, называемых соответственно строками и столбцами. Каждый ЭП может хранить один бит (0 или 1) информации. Для хранения n-разрядного слова требуются n элементов памяти. Совокупность элементов памяти, предназначенная для хранения одного слова, называется ячейкой памяти (ЯП).

Накопитель может иметь одноразрядную и многоразрядную (словарную) организацию.. Накопитель со словарной организацией позволяет за одно обращение к нему записать или считать n разрядов, составляющих слово. На рис. 1.2.1. представлена структура микросхемы памяти со словарной организацией. Микросхема с одноразрядной организацией имеет один информационный вход и один выход.

Организация ЗУ предусматривает возможность обращения к любой ЯП для записи или считывания информации. Для этой цели служит дешифратор (ДШ). Он преобразует код адреса Am-1...A0 в активный сигнал выборки ЯП. Число ЯП в накопителе равно 2m, где m — число разрядов в адресном коде. Если ЗУ допускает выборку любой ЯП в произвольном порядке, то его называют ЗУ с произвольной выборкой (ЗУПВ).

Рис. 12.4 Обобщенная структурная схема запоминающего устройства

Устройство ввода-вывода (УВВ) предназначено для усиления и нормализации информационных сигналов Dn-1...D0, подаваемых на входы ЗУ DI при записи и снимаемых с выходов DO при считывании.

Многие микросхемы имеют совмещенные входы-выходы. В таких микросхемах УВВ дополнительно выполняет и функцию разделения внутренних цепей приема и выдачи информации. К УВВ предъявляется также требование сопряжения входов и выходов с внешними линиями передачи.

Устройство управления формирует внутренние сигналы для воздействия на функциональные узлы ЗУ, соответствующего внешним сигналам управления: «Запись/Считывание» (WR/RD), «Выбор кристалла (микросхемы)» (CS). Сиг-нал WR/RD определяет режим записи при WR/RD=1 и считывания при-WR/RD=0. Сигнал CS разрешает при CS = 1 или запрещает доступ к накопителю по информационным входам и выходам при CS=0. У большинства микросхем памяти сигнал CS является основным для установления микросхемы в режим хранения независимо от состояний сигналов на других входах.

Принцип действия изображенной на рис. 12.4. схемы применительно к ОЗУ заключается в следующем. Для записи слова DIn_1... Do в заданную ЯП его необходимо подать на информационные входы DIn-1... DI0. Одновременно на адресные входы Аm-1... Ао должен быть подан код адреса выбираемой ЯП, а на входы управления — сигналы WR/RD=1 и CS-1. После выполнения этих операций входная информация через УВВ пройдет в накопитель и запишется в выбранную ячейку памяти. Для обеспечения режима хранения достаточно подать сигнал CS=0. Режим считывания реализуется аналогично режиму записи, но при значении сигнала WR/RD = 0.

Типовая схема ПЗУ отличается от ОЗУ отсутствием входов для информационных сигналов.

Следует заметить, что сигналы на входах и выходах микросхем ОЗУ и ПЗУ могут быть представлены своими прямыми значениями, как, например, в вышеприведенном рассмотрении, так и инверсными.

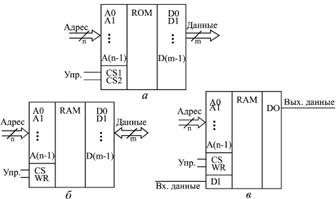

В общем случае любая микросхема памяти имеет следующие информационные выводы (Рис. 12.5).

Рис. 12.5. Микросхемы памяти: ПЗУ (а), ОЗУ с двунаправленной шиной данных (б), ОЗУ с раздельными шинами входных и выходных данных (в)

· Адресные выводы (входные), образующие шину адреса памяти. Код на адресных линиях представляет собой двоичный номер ячейки памяти, к которой происходит обращение в данный момент. Количество адресных разрядов определяет количество ячеек памяти: при количестве адресных разрядов n количество ячеек памяти равно 2n.

· Адресные выводы (входные), образующие шину адреса памяти. Код на адресных линиях представляет собой двоичный номер ячейки памяти, к которой происходит обращение в данный момент. Количество адресных разрядов определяет количество ячеек памяти: при количестве адресных разрядов n количество ячеек памяти равно 2n.

· Выводы данных (выходные), образующие шину данных памяти. Код на линиях данных представляет собой содержимое той ячейки памяти, к которой производится обращение в данный момент. Количество разрядов данных определяет количество разрядов всех ячеек памяти (обычно оно бывает равным 1, 4, 8, 16). Как правило, выходы данных имеют тип выходного каскада ОК или 3С.

· В случае оперативной памяти, помимо выходной шины данных, может быть еще и отдельная входная шина данных, на которую подается код, записываемый в выбранную ячейку памяти. Другой возможный вариант — совмещение входной и выходной шин данных, то есть двунаправленная шина, направление передачи информации по которой определяется управляющими сигналами. Двунаправленная шина применяется обычно при количестве разрядов шины данных 4 или более.

· Управляющие выводы (входные), которые определяют режим работы микросхемы. В большинстве случаев у памяти имеется вход выбора микросхемы CS (их может быть несколько, объединенных по функции И). У оперативной памяти также обязательно есть вход записи WR, активный уровень сигнала на котором переводит микросхему в режим записи.

Дата добавления: 2021-12-14; просмотров: 679;