Выход с открытым коллектором

Элементы с открытым коллектором имеют выходную цепь, заканчивающуюся одиночным транзистором, коллектор которого не соединен с какими-либо цепями внутри микросхемы (Рис. 2.18,а). Транзистор управляется от предыдущей части схемы элемента так, что может находиться в насыщенном или запертом состоянии. Насыщенное состояние транзистора трактуется как отображение логического нуля, запертое, как логической единицы.

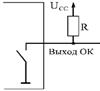

Поэтому для формирования высокого уровня напряжения на выходе элементов с открытым коллектором (типа ОК) требуется подключение внешних резисторов величиной порядка сотен Ом (или другие нагрузки), соединенные с источником питания.

Выход с открытым коллектором ОК можно считать состоящим из одного выключателя, замкнутому состоянию которого соответствует сигнал логического нуля, а разомкнутому - отключенное, пассивное состояние (Рис.2.18.б.).

Несколько выходов типа ОК можно соединять параллельно, подключая их к общей для всех выходов цепочке Ucc – R (Рис.2.18.в). При этом можно получит режим поочередной работы на общую линию, как и для элементов с тремя состояниями, если активным будет лишь один элемент, а выводы всех остальных окажутся запертыми. Если же разрешить активную работу элементов, выходы которых соединены, то можно получить дополнительную логическую операцию, называемую операцией монтажной логики.

При реализации монтажной логики высокое напряжение на общем выходе возникает только при запирании всех транзисторов, т.к. насыщение хоты бы одного из них снижает выходное напряжение до уровня U0 = Uкэн. То есть для получения логической единицы на выходе требуется единичное состояние всех выходов: выполняется монтажная операция И. Поскольку каждый элемент выполняет операцию Шеффера над своими входными переменными, общий результат окажется следующим:

F = X1X2 X3X4 … Xm-1 Xm = X1X2+X3X4+ …+Xm-1 Xm

|

|

|

| а) | б) | в) |

| Рис.2.18. Выход с открытым коллектором |

При использовании элементов с ОК в магистрально-модульных структурах требуется разрешать или запрещать работу того или иного элемента. Для элементов типа ОК кВ качестве входа ОЕ может быть использован один из обычных входов элемента. Если речь идет об элемента И-НЕ, то, подавая ) на любой из входов, можно запретить работу элемента, поставив его выход в разомкнутое состояние независимо от состояния других входов. Уровень 1 на этом входе разрешит работу элемента.

Положительной чертой элементов с ОК при работе в магистально-модульных системах является их защищенность от повреждений из-за ошибок управления, приводящих к одновременной выдаче на шину нескольких слов, а также возможность реализации дополнительных операций монтажной логики.

Недостатком таких элементов является большая задержка переключения из 0 в 1. При этом переключении происходит заряд выходной емкости сравнительно малым током резистора R. Сопротивление резистора нельзя сделать слишком малым, т.к. это привлекло бы к большим токам выходной цепи в статике при насыщенном состоянии выходного транзистора. Поэтому положительный фронт выходного напряжения формируется относительно медленно с постоянной времени RC.

До порогового напряжения (до середины полного перепада напряжения) экспоненциально изменяющийся сигал изменится за время 0,7RC, что и составляет задержку tз01.

При работе с элементами типа ОК проектировщик должен задать сопротивление резистора R, которое не является стандартным, а определяется для конкретных условий. Анализ статических режимов задает ограничения величины сопротивленияR снизу и сверху. Значение сопротивления резистора R выбирается в этом диапазоне с учетом быстродействия схемы и потребляемой ею мощности.

Ограничение снизу величины сопротивления резистора R связано с тем, что ее уменьшение может вызвать перегрузку насыщенного транзистора по току. На Рис.2.19.а показан режим, в котором нулевое состояние выхода схемы обеспечивается элементом 1 с ОК. Из этого рисунка видно, что через элемент 1 протекает суммарный ток, складывающийся из токов резистора, входных токов логических элементов (ЛЭ1…ЛЭn) и токов заперых транзисторов элементов с ОК 2 …m, т.е.

Iвых.0 = IR + nIвх.0+ (m-1)IZ≈ IR + nIвх.0, где

· Iвх.0 – входные токи элементов приемников сигнала при низком уровне выходных напряжений;

· IZ - токи запертых выходов ОК (обычно пренебрежимо малые);

· IR = (Ucc – U0)/R.

Чтобы ток выхода элемента 1 не превысил допустимого значения следует соблюдать условие

R >= (Ucc – U0)/(IВых.0.max - nIВх.0.max).

Ограничение сверху величины сопротивления резистора R связано с необходимостью гарантировать достаточно низкий уровень напряжения U1 формируемого в схеме при запертом состоянии всех выходов элементов с ОК.

Из схемы Рис.2.19.б видно, что U1 = Ucc – IRR.

В то же время IR = mIZ + nIВх.1.max.

Из полученных выражений следует R <= (Ucc – UВых.1.min)/(mIZ + nIВх.1.max) , где UВых.1.min - паспортный параметр элемента.

Имея границы диапазона значений сопротивления R, полученные как показано выше, проектировщик должен выбрать некоторое конкретное его значение. Выбор вблизи нижней границы

|

|

| а) | б) |

| Рис.2.19. Схемы для расчета минимального (б) и максимального (а) значений сопротивлений внешней цепи с открытым коллектором. |

Улучшает быстродействие схемы, а выбор вблизи верхней потребляемую мощность.

Дата добавления: 2021-12-14; просмотров: 1217;