Логические элементы на МДП-транзисторах

В настоящее время в логических схемах используются МДП-транзисторы с диэлектриком SiO2 (МОП-транзисторы).

Анализ МОП-транзисторных логических элементов достаточно прост, т.к. из-за отсутствия входных токов их можно рассматривать отдельно от других элементов даже при работе в цепочке.

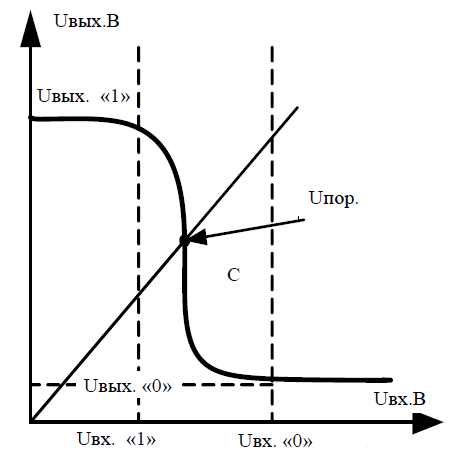

Рис.13.15.

Схема и передаточная характеристика логического элемента «НЕ» (комплементарного ключа)приведена на рис. 13.15.

Чтобы высокий и низкий уровни  и

и  инвертора максимально приближались к напряжениям

инвертора максимально приближались к напряжениям  и 0 В, необходимо выполнить следующее условие как для n-канального, так и p-канального транзистора: сопротивление канала

и 0 В, необходимо выполнить следующее условие как для n-канального, так и p-канального транзистора: сопротивление канала  <<

<<  . Это условие выполняют для специально конструируемых мощных инверторов КМОП, работающих на выходах микросхем. Напомним, что малое сопротивление канала

. Это условие выполняют для специально конструируемых мощных инверторов КМОП, работающих на выходах микросхем. Напомним, что малое сопротивление канала  равноценно повышенной крутизне усиления S полевого транзистора. Пределы

равноценно повышенной крутизне усиления S полевого транзистора. Пределы  и

и  для оконечных буферных инверторов обычно оговариваются. Если их превысить, структура может разрушиться. Оконечные транзисторы с большой крутизной занимают значительную часть площади кристалла микросхемы.

для оконечных буферных инверторов обычно оговариваются. Если их превысить, структура может разрушиться. Оконечные транзисторы с большой крутизной занимают значительную часть площади кристалла микросхемы.

Достоинства КМОП логики, как и у комплементарных ключей, является то, что она практически не потребляет мощности как в закрытом, так и в открытом состоянии.

Время переключения можно свести к минимальному, применив транзисторы в комплементарной паре с одинаковым пороговым напряжением. Технологическими способами для этого является равенство сопротивлений каналов обоих транзисторов  и

и  , что позволит уменьшить выходные фронты ЛЭ t0,1 и t1,0 и приблизить к идеальной форму передаточной характеристики.

, что позволит уменьшить выходные фронты ЛЭ t0,1 и t1,0 и приблизить к идеальной форму передаточной характеристики.

На рис. 13.16 показаны два варианта построения логических элементов на МОП-транзисторах с n-каналами.

Рис. 13.16. Логические элементы на МОП-транзисторах: а) – элемент ИЛИ-НЕ, б) – элемент И-НЕ

Транзисторы Т3 выполняют роль нагрузки. Логические уровни в обеих схемах не зависят от нагрузки и соответствуют выходным напряжениям открытого и закрытого ключа:  Соответственно, логический перепад составляет:

Соответственно, логический перепад составляет:

.

.

Напряжение питания Ec МОП-логики выбирают в 3…4 раза больше порогового напряжения Uo открывания транзисторов.

Более высоким быстродействием и низким энергопотреблением характеризуется логика на комплементарных транзисторах- КМОП-логика.

На базе МОП-транзисторов с индуцированным n-каналом строятся ячейки динамических запоминающих устройств. Электрическая схема такого элемента памяти и его структура приведены на рис. 13.17, а, б соответственно.

Адресной шиной является область “3”затвора, разрядная шина “РШ” – это область истока, к которой подведен слой металлизации“1”, область стока со слоем “4” из поликристаллического кремния образует емкость относительно подложки “  ” запоминающего элемента. Область “2”– изоляционный слой окисла кремния.

” запоминающего элемента. Область “2”– изоляционный слой окисла кремния.

Функции элементов памяти могут также выполнять транзисторы со структурой МНОП (Металл Al — Нитрид кремния SiN4 — Окисел кремния Si02—Полупроводник Si) или транзисторы со структурой ЛИЗМОП (Металл – Окисел кремния – Полупроводник с Лавинной Инжекцией Заряда).

На их основе строятся микросхемы РПЗУ (Репрограммируемых Запоминающих Устройств). Их подразделяют на две группы: стираемые электрическим сигналом (ЭСППЗУ) и стираемые УФ-излучением (СППЗУ). Микросхемы ЭСППЗУ содержат элементы памяти типа МНОП или ЛИЗМОП с двойным затвором.

Рис. 13.17

В микросхемах СППЗУ применяется также ЛИЗМОП-элемент памяти (ЭП) с двойным затвором, отличающийся от аналогичных ЭП в микросхемах ЭСППЗУ тем, что требует для стирания УФ-излучение. Элемент памяти со структурой МНОП представляет собой МОП-транзистор с индуцированным каналом n – или р-типа, имеющий двуслойный диэлектрик под затвором. Верхний слой сформирован из нитрида кремния, нижний – из окисла кремния, причем нижний слой значительно тоньше верхнего.

Если к затвору относительно подложки приложить импульс напряжения положительной полярности с амплитудой 30...40 В, то под действием сильного электрического поля между затвором и подложкой электроны получат достаточную энергию, чтобы преодолеть тонкий диэлектрический слой и попасть на границу раздела двух диэлектриков.

Поскольку верхний слой имеет значительную толщину, то электроны не могут его пройти и накапливаются внутри подзатворного слоя. Накопленный под затвором заряд электронов снижает пороговое напряжение МНОП-транзистора и тем самым смещает передаточную характеристику влево (рис. 2.20, а, б).

Состояние ЭП с зарядом под затвором соответствует лог. 1. Состояние ЭП без заряда под затвором соответствует лог. 0. В этом состоянии передаточная характеристика МНОП-транзистора занимает положение с более высоким порогом отпирания. Процесс программирования микросхем ЭСППЗУ происходит в два этапа. На первом этапе стирают информацию во всех МНОП-элементах памяти.

Для этого импульсом напряжения отрицательной полярности, прикладываемым на затвор относительно подложки амплитудой 30…40 В, электроны вытесняются из подзатворного диэлектрика в подложку. Следовательно, при стирании информации элемент памяти получает состояние лог. 0. На втором этапе производят выборочную запись в нужные ЭП лог. 1 импульсом напряжения положительной полярности, подаваемым на затвор относительно подложки.

Рис. 13.18

Рис. 13.18

|

Эта возможность основана на использовании явления лавинной инжекции электронов под затвор, которая происходит при соединении затвора с подложкой и подаче на сток и исток импульса напряжения относительно подложки и затвора такой полярности, чтобы переходы между подложкой и стоком (истоком) оказались под обратным смещением. Амплитуда импульса должна быть достаточной для возникновения в переходах электрического пробоя.

Типичные значения напряжения программирования лежат в пределах 20…30 В. В результате электрического пробоя переходов в них происходит лавинное размножение носителей заряда и инжекция части этих носителей, обладающих достаточной кинетической энергией, на границу между слоями подзатворного диэлектрика.

При считывании на затвор подают напряжение  , значение которого лежит между двумя пороговыми уровнями. Если в МНОП-транзистор записана единица, то он откроется, а при нуле останется в закрытом состоянии. Микросхемы на n-МНОП-транзисторах обладают втрое большим быстродействием, чем на р-МНОП, сниженным до 21…25 В напряжением программирования и работают от одного источника питания.

, значение которого лежит между двумя пороговыми уровнями. Если в МНОП-транзистор записана единица, то он откроется, а при нуле останется в закрытом состоянии. Микросхемы на n-МНОП-транзисторах обладают втрое большим быстродействием, чем на р-МНОП, сниженным до 21…25 В напряжением программирования и работают от одного источника питания.

Дата добавления: 2019-09-30; просмотров: 1065;