Двухступенчатые триггеры

Простейшие схемы триггеров имеют тот недостаток, что они являются одновременно источниками приёма новой информации и элементарным устройством хранения прежней. При идеальном быстродействии логических элементов, входящих в его состав, может нарушиться правильное функционирование триггера.

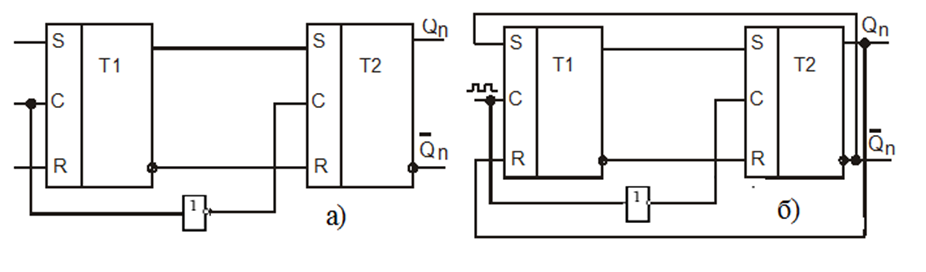

С целью устранения данного противоречия были разработаны двухступенчатые триггеры, состоящие из двух последовательно соединённых триггеров – ведущего и ведомого. Схемы этих триггеров, работающих в обычном и счётном режимах, показаны на рис.1 3.26, а, б соответственно.

Рис. 13.26

Первый триггер Т1 называется ведущим, второй Т2 – ведомым. При подаче синхроимпульса на вход «С» информация записывается в первый триггер, второй триггер при этом закрыт синхроимпульсом, прошедшим через инвертор. После окончания синхроимпульса информация перезаписывается с первого триггера во второй, так как на его входе «С» будет иметь место разрешающий сигнал.

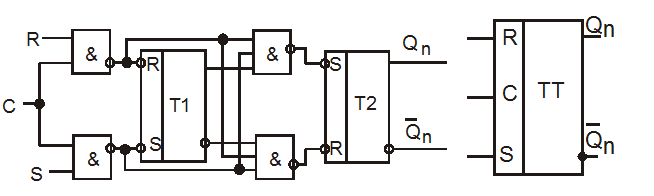

Такие триггеры часто называют MS-триггерами (в переводе с английского Master–Slave–мастер-помощник). Ещё одной разновидностью двухступенчатого триггера является RS-триггер с запрещающими связями

(рис. 13.27, а, б)

Рис. 13.27, а, б

При С = 1 информация может быть записана только в первый триггер Т1, так как на входе триггера Т2 установленные трёхвходовые логические элементы не пропустят сигнал записи. Затем при С = 0 разрешающие сигналы будут присутствовать на входах этих элементов и записанная информация может быть передана в триггер Т2.

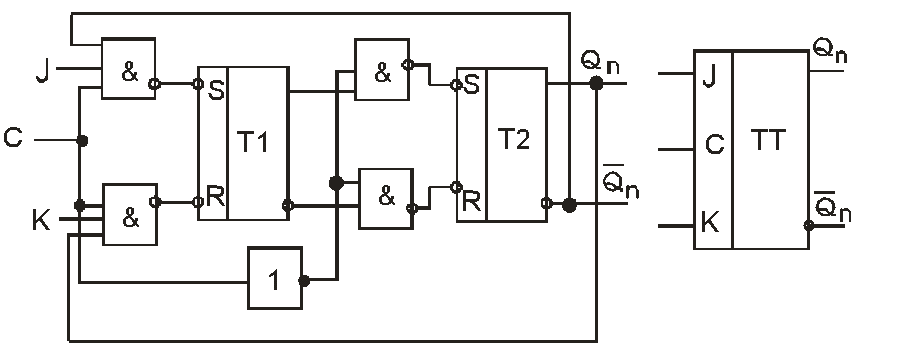

Схема двухступенчатого универсального JK-триггера, построенная на базе логических элементов «И – НЕ», приведена на рис.13.28, а, а его условное обозначение на рис.13.28. б.

а б

Рис. 13.28

Временные диаграммы его работы представлены на рис.13.29:

Триггер срабатывает по заднему фронту синхроимпульса. Видно, что триггер устанавливается в единичное состояние при J = 1 и в нулевое – при K = =1. Если J = K = 1, то он работает в счётном режиме.

Рис. 13.29

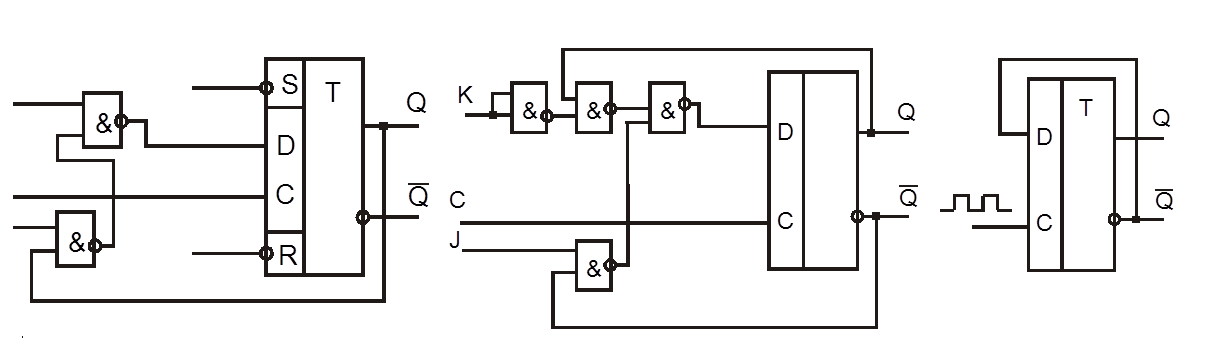

D-триггер можно использовать как RS, JK или Т-триггер. Преобразование достигается применением дополнительных элементов или связей. Для получения схемы RS-триггера можно использовать D-триггер, если в нем имеются дополнительные установочные входы R и S, причем импульсы на эти входы поступают в различные моменты времени (рис. 13. 30, а на рис. 13.31 показан триггер на основе КМОП-логики с запуском положительными импульсами.

Рис. 3.30 Рис. 13.31

На рис.13.32 - 13.34 показано преобразование D-триггера в синхронный RS, JK- и счетный триггер соответственно.

Рис. 13.32 Рис. 13.33 Рис. 13.34

Триггеры служат основой для создания более сложных устройств – счетчиков, регистров, применяются в схемах управления и формирования сигналов, в других случаях.

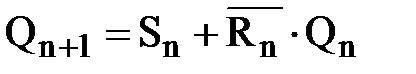

Триггеры S-типа. Это такие триггеры, которые имеют информационные входы R и S, вход синхронизации “C”, a функционирование происходит следующим образом: при комбинации сигналов  = 1 принимают единичное состояние, а при всех остальных комбинациях информационных сигналов функционируют, как обычный «R-S»- триггер. Уравнение триггера S-типа имеет вид

= 1 принимают единичное состояние, а при всех остальных комбинациях информационных сигналов функционируют, как обычный «R-S»- триггер. Уравнение триггера S-типа имеет вид

. (13.41)

. (13.41)

Схема (рис. 3.23) и таблица истинности (табл. 3.8) приведены ниже.

Схема триггера S- типа отличается от R-S-триггера наличием дополнительного инвертора, который блокирует прохождение сигнала через элемент Э3 при S = 1.

При комбинации входных сигналов S·R·C = 1 элемент Э3 будет закрыт и триггер будет принимать единичное состояние, независимого от предыдущего.

Таблица 3.8

Рис. 13.35

Синхронный триггер Е-типа. К триггерам Е-типа относят триггеры, которые при комбинации сигналов на входе S·R = 1, не изменяют своего состояния, а при всех остальных сочетаниях информационных сигналов работают в соответствии с таблицей обычного R-S-триггера.

Схема (рис. 13. 36) и таблица истинности имеют (табл. 3.9) следующий вид.

| Таблица 3.9 | |

| |

| Рис. 13.36 |

В схеме имеется два дополнительных инвертора, что приводит к тому, что запись информации происходит только при несоответствии сигналов на входах R и S. При комбинации сигналов S R =1 элементы Э3 и Э4 будут закрыты и триггеры не изменят своего состояния. Такого типа триггеры находят применение в управляемых устройствах цифровых схем.

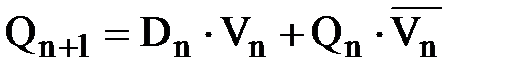

Триггеры D-V-типа. Такого типа триггер состоит из синхронного D- триггера с дополнительным входом V. Если V=1, то он функционирует как D-триггер, а при V = 0 – сохраняет исходное состояние, независимо от изменения информации на входе D. Уравнение триггера «D-V» типа имеет вид

. (13.42)

. (13.42)

Схема триггера (рис. 3.25) и таблица истинности (табл. 3.10) выглядят следующим образом.

| Таблица 3.10 | |

| |

| Рис. 13.37 |

В этом триггере входы D и V– информационные, вход «С» – вход синхронизации. При V = 1 триггер DV- типа превращается в синхронный D-триггер. Условием устойчивой работы данного триггера является совпадение сигнала на входе V и C (V = C = 1) и превышение по длительности сигнала на входе V. Такие схемы используются при построении счетчиков, регистров сдвига, в устройствах управления. К универсальным DV-триггерам относят, например, К561ТН3, JKD-триггер К501ТК1П.

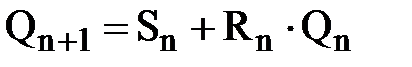

Триггеры R-типа. Это такие триггеры которые имеют информационные входы R и S, вход синхронизации «C» , a функционирование происходит следующим образом: при комбинации сигналов R∙S = 1 триггер принимает нулевое состояние, а при всех остальных комбинациях информационных сигналов функционирует, как обычный R-S- триггер. Уравнение триггера R-типа имеет вид

. (13.43)

. (13.43)

Схема (рис.1 3.37) и таблица истинности (табл. 3.11) приведены ниже:

При комбинации входных сигналов R·S·С = 1 элемент Э2 будет закрыт и триггер установится по входу R в нулевое состояние.

| Таблица 3.11 | |

| |

| Рис. 13.37 | ` |

Дата добавления: 2019-09-30; просмотров: 1675;