Метод наращивания перераспределительных слоев

В последнее время в мире возросли технические требования к качеству ПП и экологической безопасности их производства, что связано с применением ПМК и технологии поверхностного монтажа. Конструкция и технология изготовления ПП практически полностью определяется элементной базой и способами ее монтажа. В технологии сборки электронных модулей на ПП в настоящее время применяют следующую элементную базу [44]:

• традиционные выводные компоненты или компоненты «в отверстия» (IMC или ТНТ), включающие:

1) пассивные компоненты с осевыми (аксиальными) выводами;

2) пассивные неактивные компоненты с радикальными выводами;

3) ИМС в корпусах 1-, 2- (DIP-корпусах), 3-й 4-го типа;

• ПМК (SMC или SMD), к которым относятся:

1) пассивные чип-компоненты в корпусах, различающихся по размеру, например, 0805, 0605, MELF;

2) ИМС в базовых технологических корпусах SO, PLCC, OFP, BGA и т. д.;

• бескорпусные ИМС, для монтажа которых применяют специализированные технологии, которые еще не являются стандартом (tape automated bonding — TAB, flip chip-FC, COB, DCA и др.).

• нестандартные компоненты (odd form components — OFC), такие как соединители, разъемы, трансформаторы, колодки, держатели, экраны и пр.

Рост функциональности на единицу площади требует от конструкторов-технологов ЭА увеличения количества соединений на единицу площади ПП. Для реализации высокого уровня плотности соединений разработано много новых упаковочных технологий (корпусов) ЭРИ и ПМК в микрокорпусах с большим числом выводов (1000 и более) и малым шагом расположения выводов 0,25...0,5 мм [45]. К таким упаковочным технологиям относятся следующие технологии:

• СОВ (chip on board) — чип на плате или технология «открытой матрицы»;

• FP (flip chip) — перевернутый кристалл;

• CSP (chip scale packaging или chip size packages) — кристалло-соразмерный корпус или микрокорпус в размер кристалла;

• BGA (ball grid arrays) — матрица шариковых выводов;

• МСМ (multichip modults) — многочиповый модуль;

• DCA (direct chip attach) — прямое присоединение чипа;

• СОС (chip on chip) — чип на чипе и др.

Основной тенденцией производства ЭА является переход от технологии сквозных отверстий (through — hole technology — ТНТ) к технологии поверхностного монтажа (surface mounted technology — SMT) и внутри нее — к fine pitch technology (FPT), BGA, CSP, МСМ и др. Использование технологии поверхностного монтажа (SMT-технологии) существенно увеличивает плотность монтажа, что наглядно демонстрирует приведенное в табл. 4.34 сравнение некоторых конструктивных параметров ПП и ЭРИ для технологии монтажа в отверстия, поверхностного монтажа и FPT-технологии.

Сравнительная характеристика некоторых корпусов представлена в табл. 4.35 [46].

Поскольку конструкция корпуса ЭРИ и ПМК непосредственно влияет на конструкцию и технологию изготовления ПП, рассмотрим особенности наиболее широко применяемых в настоящее время в ЭА корпусов микросхем подробнее.

В настоящее время широко используются микросхемы в пластиковых корпусах QFP с малым и сверхмалым шагом выводов от 0,4 до 0,25 мм (мелкошаговые); общемировое их потребление постоянно растет. Число дефектов корпусов QFP с шагом 0,5 мм составляет порядка 150—200 дефектов на 1 млн (Defeсt per Million — DPM) или 0,005 % брака. Однако установочная площадь корпуса QFP в несколько раз больше, чем у корпуса FC (см. табл. 4.35).

Сегодня основной технологией производства корпусов за рубежом является технология BGA, что связано с большим количеством каналов ввода/вывода микросхемы. Различают четыре основных типа корпусов BGA: пластиковые, керамические ленточные и металлические. В них устранены недостатки корпусов QFP (уменьшены размеры, увеличено число контактов и производительность блока). Отмечается значительное увеличение плотности ПП (примерно на 59 %) по сравнению с QFP. Кроме того, эти корпуса более прочные, проще в изготовлении, чем мелкошаговые QFP. Однако использование корпуса BGA оправдано, если количество каналов ввода/вывода микросхемы превышает 256. Для таких компаний, как Intel, LSI Logic, Texas instruments и VLSI Technology, производящих изделия с мини- или микро-BGA, с шагом 0,75 мм, происходит сближение понятий между BGA, мини-BGA и микро-BGA. Поэтому важно отметить, что возможности ТП изготовления и аппаратной части для BGA позволяют уменьшить шаг до 0,5 мм и менее. Число дефектов, корпусов BGA составляет около 3—10 DPM (на 1 млн). Для монтажа кррпусов BGA плотность межслойных переходов должна быть не менее 310 переходов/см2.

Корпуса CSP, известные так же как микро-BGA или мини-BGA, представляют собой промежуточную ступень между BGA и перевернутым кристаллом (флип-чип). Сборка CSP представляет собой установку бескорпусного кристалла обратной стороной непосредственно на ПП, используя адгезив на основе эпоксидной смолы. После сборки выполняется присоединение золотой (термозвук), либо алюминиевой (ультразвук) проволокой контактной площадки каждого вывода к ПП. Затем проводится контроль, после которого компоненты и проводящие соединения полностью заливаются эпоксидной смолой.

К техническим проблемам установки бескорпусного компоновочного узла кристалла на ПП относится большое различие в ТКЛР (coefficient of thermal expansion — CTE) кристалла и ПП. ТКЛР кремниевого кристалла составляет (2,5...3) • 10-6 оС-1, а стандартной ПП - (16...20) • 10-6 оС-1. Следовательно, место сопряжения чипа и ПП является потенциальным источником отказов, которое подвергается относительно высоким температурам не только при креплении кристалла, но и при включении и выключении устройства, при которых он также может подвергаться множественным температурным циклам. В результате чего в месте сопряжения могут создаваться остаточные напряжения.

Основные компании по сборке полупроводников, включая Amkor/Anam, STATS, ASE, Intel, LSI logic, Texas Instruments и Matsushita, в настоящее время осуществляют массовый выпуск CSP и в некоторых случаях цены на эти корпуса соизмеримы с ценами на PBGA.

Размер корпуса CSP обычно превышает размер самого кристалла не более чем на 20 %. Наибольшее применение корпуса CSP нашли в микросхемах памяти (особенно флэш), управления (аналого-цифровые преобразователи, микроконтроллеры, логические схемы с малым количеством каналов ввода/вывода), цифровой обработки, а также в микросхемах специального назначения (ASIC) и микропроцессорах. Однако широкое применение CSP ожидается через несколько лет, вследствие недостаточной их надежности и конкурентоспособной цены в настоящее время.

Перед креплением кристалла в корпус СОВ моделируют остаточные напряжения, которые могут возникнуть в месте сопряжения кристалла с ПП, для определения адгезива с соответствующими свойствами и толщины, необходимой для поглощения напряжений. Причинами снижения надежности СОВ являются проволочное соединение кристалла с ПП, термообработка и охлаждение герметика, в результате которых могут возникнуть температурные напряжения между герметикой и кристаллом и герметикой и ПП.

В перевернутом кристалле (флип-чип — flip chip — FC) достигнута наивысшая плотность монтажа корпуса. Кристалл крепится лицевой стороной вниз, используя капли припоя или проводящих полимеров, непосредственно на ПП. Эта технология является наиболее компактной из всех новых технологий (корпус занимает всего 13 % площади эквивалентного корпуса QFP).

Преимущества флип-чипа:

• экономия места на ПП (малая установочная площадь);

• незначительная высота и масса;

• сокращение длины соединений, что улучшает электрические параметры;

• уменьшение числа соединений, что сокращает количество мест потенциальных отказов.

Недостатки флип-чипа:

• необходимость высокой плотности рисунка схемы ПП под посадочное место для флип-чипа, что повышает стоимость ПП;

• большие затраты на технологию прикрепления полусферических выводов к кристаллу;

• сложность подбора флюса и адгезивов в зависимости от вида флип-чипа и подложки;

• сложность ремонта ПП с их применением;

• низкий уровень выхода годных флип-чипов;

• сложность распределения тепловой энергии для обеспечения надежности ФУ.

Флип-чипы применяют в устройствах:

• с низким числом каналов ввода/вывода — электронные часы и автомобильная электроника (до 60 %);

• со средним числом каналов ввода/вывода — драйверы дисплеев, модули формата PCMCIA и в компьютерной технике большого формата;

• с числом каналов ввода/вывода от 2000 и выше применяют значительно реже, так как в них используют кристаллы только высокой степени надежности, монтируемые, как правило, на керамические подложки.

Кроме того, возможно применение корпусированных флип-чипов, монтируемых на ПП (FCOB). Компания Flextronics запатентовала многокристальный блок, в котором до четырех чипов памяти, расположенных друг на друге, можно размещать на многокристальном модуле.

В технологии TAB кремниевые кристаллы крепятся к полимерному ленточному носителю, на котором сформированы внутренние соединения выводов чипа. Присоединение выводов чипа к ПП осуществляется при помощи внешних выводов пайкой горячим газом или лазерной микросваркой. Для монтажа кристаллов на ленточном носителе (TAB) плотность межслойных переходов ПП должна составлять порядка ПО переходов/см2.

Чаще всего из 'рассмотренных корпусов используются BGA и CSP, коммутация вводов/выводов которых является трудной задачей. Если необходимая плотность связей для корпусированных микросхем в 1-, 2-, 3- и 4-м типах корпусов должна быть порядка 60... 100 см/см2, то для микросхем в микрокорпусах она составляет 300...500 см/см2 [2].

Тенденции развития корпусов ЭРИ: большое число выводов (более 1000) и малый шаг их расположения (0,3, 0,4, 0,5 и более) мм, которые приводят к увеличению числа межсоединений в ЭА, новые способы упаковки кристаллов и новые способы формирования контактных соединений корпуса ЭРИ с ПП — все это требует соответствующих технических характеристик ПП, как средства коммутации, постоянного увеличения плотности печатного монтажа, разработки новых конструкций ПП, ТП их изготовления, базовых и расходных материалов.

Переход от технологии сквозных отверстий на ПП к поверхностному монтажу не случаен, он связан с тем что переходные металлизированные отверстия в том числе и сквозные могут занимать до 20...30 % площади ПП и препятствовать увеличению числа проводников в слое. Если же идти по пути уменьшения диаметра отверстий и отказаться от контактных площадок, что связано с большими техническими и экономическими трудностями, то минимальное значение диаметра отверстия, полученного механическим сверлением составит порядка 0,15 мм. Поэтому разработаны конструкции и технологии изготовления ПП с глухими межслойными переходами, в которых формирование микросоединений производят лазерным сверлением, фотолитографией или плазменным «сухим» травлением.

Для монтажа ПМК, крепление и самоцентрирование которых осуществляется за счет расплавления припойной пасты на контактных площадках определенной формы и размеров, необходимо изготовить ПП не хуже 4-го класса с паяльной маской и повышенными требованиями к неровности поверхности, а для монтажа ПМК в микрокорпусах с малым шагом выводов необходимы высокоплотные (high density printed circuit) МПП с проводниками менее 50 мкм, шириной контактных площадок менее 100 мкм и микропереходами диаметром 0,1...0,2 мм. В конструкциях МПП для высокоинтегрированной элементной базы глухие микропереходы (микроотверстия) выполняют между наружным и ближайшими внутренними слоями (в перераспределительных слоях), а сквозные скрытые межслойные отверстия размещают между внутренними слоями МПП (рис. 4.43). В перераспределительных слоях расположены проводники, которые соединяют выводы микросхем, припаянные к контактным площадкам наружного слоя, с проводниками внутренних слоев.

Эти технологии называются технологиями наращивания (Built-up technology). Пример структуры 8-слойной МПП со сквозными и глухими отверстиями приведен на рис. 1.5.

Многослойные ПП, изготовленные по технологии наращивания имеют:

• глухие (слепые) микропереходы;

• скрытые (внутренние) микропереходы;

• скрытые сквозные металлизированные межслойные отверстия;

• сквозные металлизированные отверстия.

В зависимости от применяемой технологии наращивания в центре МПП в качестве стержневого слоя используются или тонкие фольгированные материалы, или диэлектрические слои. Такие МПП имеют ряд преимуществ:

• высокая плотность печатных проводников и межслойных переходов, что позволяет уменьшить площадь монтажа и длину электрических соединений, задержку сигналов, увеличить помехоустойчивость;

• уменьшенные размеры, массу и количество слоев МПП;

• высокая надежность глухих межслойных переходов;

• улучшенные электромагнитные характеристики;

• низкая стоимость и пр.

Малые размеры контактных площадок глухих (слепых) и скрытых (внутренних) межслойных переходов увеличивают область (площадь) прокладки проводников. Технология наращивания обеспечивает большую экономию площади для трассировки, чему способствует малая ширина проводников внутренних слоев 0,08...0,05 мм, малые диаметры микроотверстий, зигзагообразное, веерообразное или в шахматном порядке расположение глухих (слепых) и скрытых отверстий, размещение глухих (слепых) отверстий в контактных площадках, на которые монтируются ПМК (рис. 4.44) (BGA, CSP и СОВ). В этом случае коммутация ПМК осуществляется на лежащих ниже сигнальных слоях (рис. 4.45).

К достоинствам можно также отнести возможность использования сэкономленной площади на слоях для размещения внутренних резисторов, конденсаторов и индуктивностей с целью уменьшения их числа и площади, занимаемой ими на наружных слоях (см. рис. 4.43, а).

Размещение отверстий в контактных площадках и под корпусом ПМК позволяет создавать наружные слои практически без трассировки, а также использовать их как экраны для улучшения электромагнитных и электрических характеристик ПП (см. рис. 4.44, б).

Существует большое количество способов изготовления МПП с высокой плотностью монтажа с микропереходами. Основными этапами одного из способов технологии наращивания являются [47]:

• изготовление двусторонней заготовки стержневого слоя с сигнальными проводниками и межслойными отверстиями;

• заделка — заполнение внутренних межслойных (скрытых) сквозных металлизированных отверстий смолой для получения плоского, без раковин заполнения, без образования впадин над отверстиями;

• нанесение диэлектрика в виде жидкого эпоксидного покрытия, покрытой фольгой, арамида, полиимидного пленочного ламината или фольгированного медью материала. При нанесении жидкого диэлектрика для получения требуемой толщины необходимо произвести покрытие несколько раз, так как, во-первых, он наносится поочередно на каждую сторону стержневого слоя; во-вторых, толщина каждого слоя составляет 20...30 мкм. Пленочный диэлектрик достаточной толщины (25...65 мкм) и равномерности наносят одновременно на обе стороны стержневого слоя за один раз;

• лазерное сверление микроотверстий с коническим профилем боковой стенки для равномерного распределения меди при металлизации микроотверстий (в международной практике считается основной технологией создания микроотверстий при существующих также фотолитографии и плазменном сухом травлении). При лазерном сверлении применяется большое разнообразие диэлектриков; отверстия получают с самым высоким отношением толщину слоя диэлектрика к диаметру микроотверстия, высокую точность совмещения сквозных микроотверстий. О материалах для лазерной технологии см. гл. 2;

• металлизация;

• получение рисунка наружных слоев с применением фоторезиста с высокой разрешающей способностью;

• электрические испытания с использованием контактирующих устройств с высокой плотностью контрольных точек.

Технологию послойного наращивания перераспределительных слоев с глухими межслойными микропереходами применяют при изготовлении высокоплотных 4-, 6- и 8-слойных МПП. При этом в качестве основного структурного элемента используют двусторонние заготовки с сигнальными проводниками и межслойными микропереходами, но даже применяя заготовки с одним слоем микроотверстий, получают экономию от 10 до 20 % по сравнению с обычными МПП с механическим сверлением отверстий.

Многослойные ПП (МПП)

Состоят из чередующихся слоев диэлектрического материала с односторонним или двухсторонним расположением проводящих слоев и изоляционных слоев.

Желательно, чтобы для обеспечения хорошего сцепления между слоями диэлектрик и межслойные прокладки изготавливались на основе одного и того же материала.

При необходимости возможно наличие экранирующих слоев и слоев электропитания.

Число проводящих слоев определяется допустимой толщиной МПП, толщиной диэлектрика, меди, межслойных прокладок, диэлектрических свойств их, которые определяются содержанием смолы (до 30%) в межслойных прокладках.

. При

. При  мм возможно 10-12 проводящих слоев.

мм возможно 10-12 проводящих слоев.

Где  - число слоев диэлектрика и его толщина,

- число слоев диэлектрика и его толщина,  - толщина прокладки,

- толщина прокладки,  - толщина слоя меди,

- толщина слоя меди,  - число слоев с площадью Cu не менее 40%.

- число слоев с площадью Cu не менее 40%.

Достоинства МПП:

1. снижение количества внешних контактов;

2. высокая устойчивость к внешним воздействиям;

3. при использовании внутренних слоев со стандартным рисунком проводников сокращается время проектирования;

4. многослойный печатный монтаж позволяет уменьшать габаритные размеры, повышается плотность монтажа, уменьшается трудоемкость монтажных соединений. Высокая плотность монтажа, меньше габариты, масса, уменьшенная длина электрических связей, т.е. быстродействие повышается;

5. упрощается решение задач пересечения и распределения проводников;

6. наличие экранных слоев, можно увеличить теплоотвод.

Недостатки МПП:

1. высокая стоимость;

2. процесс изготовления трудоемкий. Включает до 100 технологических операций, требуется большое количество единиц оборудования (до 40.. .50), больше % брака;

3. предъявляются высокие требования к точности изготовления печатных проводников и переходных отверстий,

4. предъявляются высокие требования к исходным материалам;

5. разные ТКЛР меди, диэлектриков, смолы и т.д.

При изготовлении МПП применяют методы:

1. соединения слоев объемными деталями;

2. открытых контактных площадок;

3. с выступающими выводами;

4. планарное прессование;

5. послойное наращивание рисунка;

6. металлических сквозных отверстий - базовый техпроцесс изготовления МПП.

Сравнение характеристик конструктивно-технологических вариантов МПП.

| Тип МПП | Максимальное число слоев | Механическая надежность | Относительная плотность мон-тажа | Трудоемкость изготовления | Ремонтопри-годность | Возможность механизации и автоматизации | Стоимость изделия | Длительность цикла произ-водства |

| Соединение объем-ными деталями | 4-6 | низкая | 0,5 | низкая | да | среднее | среднее | |

| Открытые контакт-ные площадки | 8-12 | высокая | 0,6 | 0,7 | высокая | нет | низкое | малое |

| Выступающие вы-воды | 10-15 | высокая | 0,5 | высокая | да | высокое | среднее | |

| Попарное прессование | хорошая | 0,8 | Затрудни-тельная | да | низкое | большое | ||

| Последовательное наращивание | высокая | низкая | нет | высокое | большое | |||

| Металлизация сквозных отверстий | 15-20 | хорошая | 0,8 | хорошая | да | низкое | среднее |

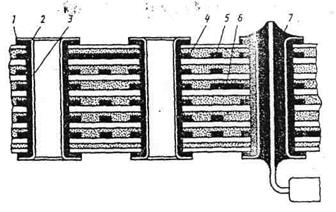

Рис. 8.13. МПП, изготовленная методом Рис. 8.14. МПП с открытыми контактными

попарного прессования площадками

Рис. 8.15.МПП с выступающими выводами Рис. 8.16. МПП, изготовленная методом послойного

наращивания

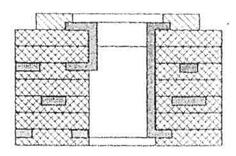

Рис.6.3.13. Структура МПП, изготовленной

методом металлизации сквозных отверстий:

1 – контактная площадка наружного слоя; 2 – защитное покрытие;

3 – металлизация сквозного отверстия; 4 – контактная площадка

внутреннего слоя; 5, 6 – проводники; 7 - припой

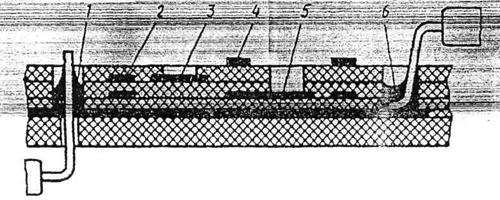

Рис. 6.3.10. Структура МПП, изготовленной методом открытых контактных площадок:

1 - пайка в «колодец» штыревого вывода; 2 - печатный проводник

внутреннего слоя; 3 - монтажная площадка; 4 - печатный проводник

внешнего слоя; 5 — соединение монтажных площадок в одном слое;

6- пайка в «колодец» планарного вывода

Дата добавления: 2016-11-26; просмотров: 1960;