Прямой цифровой синтезатор частоты

Решим задачу, поставленную в предыдущем пункте, используя прямой цифровой синтезатор частоты (DDS). В этом случае нет необходимости разбивать диапазон 4…8 МГц на поддиапазоны, а шаг пересторйки частоты пользователь может программировать произвольно, так как если мы будем использовать синтезатор семейства AD983x, минимально возможное значение этого параметра составит сотые доли Герца (см. параграф 7.5). В случае использования DDS нужно дополнительно оговорить еще один параметр – уровень паразитных составляющих в спектре выходного колебания. Пусть в нашем случае эта величина не превышает –60 дБн (относительно несущей).

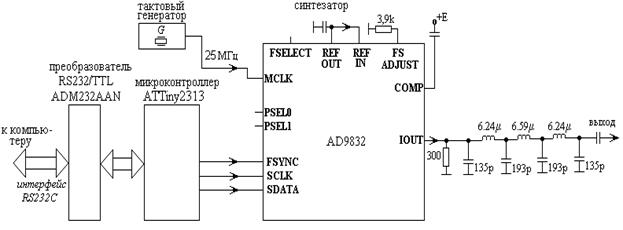

Синтезатор частоты (структурная схема – рис.8.3.5) выполним на основе ИМС прямого цифрового синтеза AD9832 фирмы Analog Devices. От рассматривавшейся выше ИМС AD9830 (рис. 7.5.6) она отличается последовательным вводом данных, в 5 раз меньшей потребляемой мощностью и возможностью синхронизации момента смены частоты или фазы с тактовым колебанием синтезатора.

ИМС синтезатора частоты вырабатывает ток квазисинусоидальной формы, частота и начальная фаза которого зависят от управляющих битов, записываемых пользователем в память ИМС синтезатора при помощи специальной управляющей программы для персонального компьютера. Выходной токовый сигнал ИМС синтезатора через реконструирующий фильтр подключается к соответствующему входу схемы радиостанции.

Рис. 8.3.5

Тактовый сигнал с частотой f MCLK = 25 МГц для ИМС синтезатора вырабатывается интегральным кварцевым генератором и подается на вход MCLK микросхемы. Поскольку микросхема AD9832 обладает 32-разрядным аккумулятором фазы (структуру микросхемы см. на рис. 8.3.6), то частота выходного колебания синтезатора f OUT будет определяться следующим образом:

f OUT = (f MCLK / 232)*FREQ,

где FREQ – 32-х разрядный (в двоичном представлении) код частоты, записанный в один из регистров частоты FREQ0 REG, FREQ1 REG. Из этой формулы видно, что данный синтезатор способен формировать синусоидальный сигнал в диапазоне частот от сотых долей герца до единиц мегагерц без каких-либо переключений. Все необходимые данные синтезатор получает от компьютера через микроконтроллер ATTiny2313 фирмы ATMEL, в памяти которого находится программа преобразования данных из формата интерфейса RS-232C в специальный формат последовательной передачи данных, встроенный в ИМС AD9832.

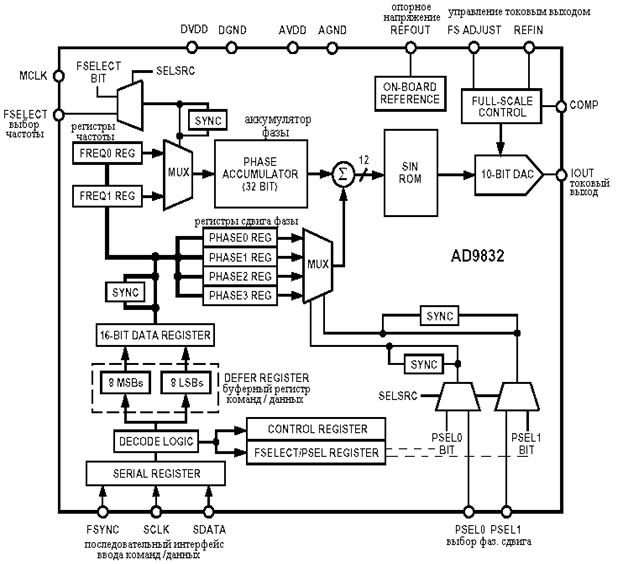

Рис. 8.3.6

Кроме двух 32-разрядных регистров FREQ0 REG и FREQ1 REG, в которых могут храниться коды частоты выходного сигнала, в ИМС синтезатора предусмотрены еще четыре 12-разрядных регистра, в которых могут быть записаны четыре возможных значения начальной фазы выходного сигнала: PHASE0 REG…PHASE3 REG. Регистры выбора частоты и регистры выбора сдвига фазы подключены к фазовому аккумулятору через мультиплексоры (MUX), управляемые одним из двух способов: аппаратно или программно. Способ выбора регистра частоты или начальной фазы задается битом SELSRC прошивки синтезатора:

- SELSRC = 1 - программный выбор, когда за подключение конкретного регистра к фазовому аккумулятору отвечают определенные биты прошивки синтезатора: FSELECT (для частоты) и PSEL0, PSEL1 (для фазового сдвига); нужно помнить, что в режиме программного выбора частоты (фазы) на входе FSELECT (на входах PSEL0, PSEL1) должен быть установлен низкий логический уровень;

- SELSRC = 0 - аппаратный выбор, когда указанные выше биты игнорируются, а выбор регистра зависит от логических уровней на входах ИМС FSELECT (для частоты) и PSEL0, PSEL1 (для фазового сдвига).

Пример:

- установлено FSELECT = 0, следовательно, используется регистр FREQ0 REG;

- установлено PSEL0 = 0, PSEL1 = 0, следовательно, используется регистр PHASE0 REG.

Нужно отметить, что смену регистров частоты или фазового сдвига нежелательно производить в моменты положительного фронта тактового сигнала синтезатора, в противном случае возможны искажения выходного сигнала. Для устранения нежелательных последствий таких переключений в ИМС AD9832 предусмотрены подключаемые по желанию пользователя логические блоки синхронизации загрузки «SYNC» (см. рис. 8.3.6). При установке бита SYNC = 1 включается задержка смены регистров частоты и фазы, необходимая для устранения искажений синусоиды; если же SYNC = 0, смена частоты или фазы происходит асинхронно.

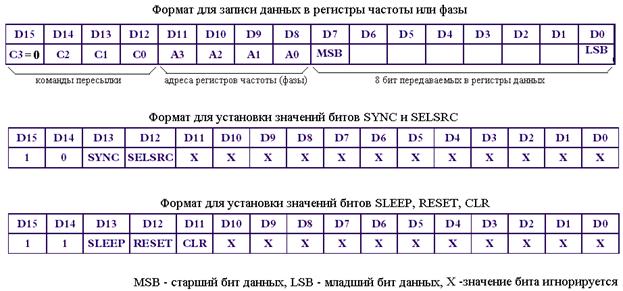

Опишем теперь порядок загрузки регистров и записи команд синтезатора AD9832. Протокол обмена данными, принятый в синтезаторе, предусматривает передачу данных и команд 16-битными словами D15…D0 (рис. 8.3.7), в которых предусмотрены:

- биты для передачи команд С3…С0 (это команды пересылки данных в регистры синтезатора);

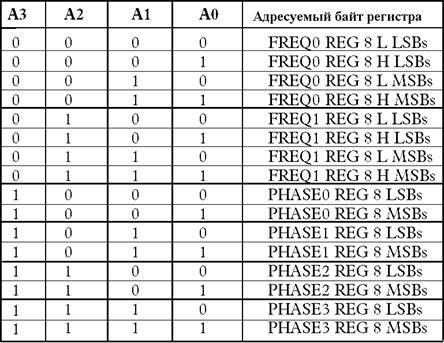

- биты А3…А0 адреса регистра фазы или частоты, в который отправляют данные (табл. 4.1);

- биты данных о частоте или фазе MSB…LSB (8 бит);

- команды для установки значений битов SYNC, SELSRC (их значение см. выше);

- команды для установки значений битов SLEEP, RESET, CLR.

SLEEP = 1 - режим пониженного энергопотребления микросхемы, выходной сигнал отсутствует («спящий» режим); SLEEP = 0 – обычный рабочий режим.

RESET = 1 – сброс аккумулятора фазы, на выходе синтезатора присутствует ток, равный половине полного значения токовой шкалы; RESET = 0 – обычный рабочий режим.

CLR = 1 – сброс битов SYNC, SELSRC в ноль. Бит CLR после установки пользователем в 1 автоматически возвращается в 0 (в отличие от битов SLEEP и RESET).

Рис. 8.3.7

Рис. 8.3.8

Таблица 8.3.1

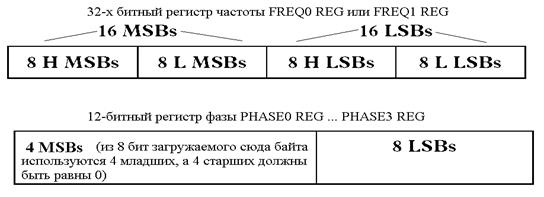

Из рис. 8.3.7, в частности, видно, что передать в какой-либо регистр частоты или фазы можно за один цикл обращения к ИМС синтезатора только 8 бит данных. Поэтому 32-х битные регистры частоты FREQ0 REG и FREQ1 REG разделены на 4 байта, а 12-битные регистры фазы PHASE0 REG…PHASE3 REG –на 2 байта, как это показано на рис. 8.3.8. Адреса каждого из этих байтов приведены в табл. 8.3.1.

Список команд, управляющих загрузкой данных в регистры частоты и фазы, приведен в табл. 8.3.2. Из этой таблицы ясно, что данные через последовательный порт синтезатора поступают порциями в один байт, а в регистры частоты или фазы загружаются двухбайтными словами, поскольку байт, переданный первым, дожидается следующего байта в промежуточном 16-битном регистре DEFER REGISTER, который можно увидеть на рис. 8.3.6.

Таким образом, чтобы загрузить 12-разрядный регистр фазового сдвига PHASEi REG, достаточно одной пересылки из промежуточного регистра DEFER REGISTER, а для загрузки регистра частоты необходимо две таких пересылки.

Приведем пример последовательности команд для установления частоты синтезатора. Пусть необходимо в качестве рабочего регистра выбрать FREQ1 регистр и установить частоту f OUT = 5577 кГц (как в примере предыдущего пункта) при тактовой частоте f MCLK = 25 МГц. Выбор рабочего регистра частоты пусть производится программным способом (SELSRC = 1).

1) Выводим синтезатор из спящего режима, устанавливаем бит SELSRC = 1 (как это сделать – см. рис. 8.3.7). На входе FSELECT нужно установить логический 0.

2) Указываем в качестве рабочего регистра FREQ1 REG, для чего отправляем в синтезатор команду D15…D0 = 0101 1 00000000000, см. табл. 8.3.2 и рис. 8.3.7.

3) Находим содержание байтов 8H MSBs…8L LSBs (рис.8.3.8), используя встроенный калькулятор Windows:

FREQ = (f OUT / f MCLK )* 232 » 95812130410 = = 111001 00011011 11000101 010110002;

8H MSBs = 00111001; 8L MSBs = 00011011;

8H LSBs = 11000101; 8L LSBs =01011000.

4) Записываем 8 бит частоты в DEFER REGISTER, начиная с самого старшего байта 8H MSBs (что не обязательно). Для этого записываем команду D15…D0 = 0011 0111 00111001, см. табл. 8.3.1, 8.3.2 и рис. 8.3.7.

5) Записываем еще 8 бит частоты (это 8L MSBs) и отправляем вместе 8H MSBs и 8L MSBs в регистр FREQ1 REG с помощью команды D15…D0 = 0010 0110 00011011.

6) Аналогично загружаем 8 бит частоты (теперь это 8H LSBs) в DEFER REGISTER: D15…D0 = 0011 0100 11000101.

7) Дописываем последние 8 бит частоты (это 8L LSBs) и отправляем вместе 8H LSBs и 8L LSBs в регистр FREQ1 REG с помощью команды D15…D0 = 0010 0110 01011000.

После этой записи на выходе ИМС появляется колебание с требуемой частотой.

Таблица 8.3.2

| С3 | С2 | С1 | С0 | Команда |

| Записывает 16 «фазовых» бит (из которых 8 содержатся в данном информационном пакете, а другие 8 уже находятся в DEFER REGISTER) в указанный битами адреса регистр PHASE0 REG…PHASE3 REG | ||||

| Записывает 8 «фазовых» бит в DEFER REGISTER | ||||

| Записывает 16 бит частоты (из которых 8 содержатся в данном информационном пакете, а другие 8 уже находятся в DEFER REGISTER) в указанную битами адреса часть регистра FREQ0 REG или FREQ1 REG | ||||

| Записывает 8 бит частоты в DEFER REGISTER | ||||

| При SELSRC=1 выбирает рабочий регистр фазы, используя биты D9 как PSEL0 и D10 как PSEL1. (Если установлено SELSRC=0, эти биты игнорируются, а для выбора используются одноименные входы ИМС.) | ||||

| При SELSRC=1 выбирает рабочий регистр частоты, используя бит D11 как FSELECT. (Если установлено SELSRC=0, этот бит игнорируется, а для выбора используется одноименный вход ИМС.) | ||||

| При SELSRC=1 одновременно выбирает рабочий регистр фазы, используя биты D9 как PSEL0 и D10 как PSEL1, и частоты, используя бит D11 как FSELECT. (Если установлено SELSRC=0, эти биты игнорируются, а для выбора используются одноименные входы ИМС.) | ||||

| Зарезервировано (применяется для тестирования). |

Кратко о проектировании реконструирующего или «антиалайсингового» фильтра (см. параграф 7.2). Как было условлено выше, уровень нежелательных спектральных составляющих не должен превышать –60 дБн. Реконструирующий фильтр устанавливается для подавления «образов» основного сигнала; рассмотрим наихудший в этом смысле случай – максимальную частоту выходного сигнала 8 МГц, при которой ближайший «образ» будет расположен на частоте

f IMAGE1 = f MCLK - f OUT = 25 МГц - 8 МГц = 17 МГц.

Учитывая «sinc(x)» форму огибающей спектра колебания на выходе ЦАП DDS

рассчитаем, что несущая с частотой 8 МГц будет ослаблена на 1,5 дБ, а первый образ с частотой 17 МГц – на 8 дБ. Значит, требование к реконструирующему фильтру по подавлению первого образа снижаются на 8 - 1,5 = 6,5 дБ и составляет 60 – 6,5 = 53,5 дБ.

Рис.8.3.9

Рис.8.3.10

Рис.8.3.10

Для проектирования фильтра можно воспользоваться любой известной методикой расчета или САПР. Выберем ФНЧ Чебышева и зададим следующие его параметры (с учетом некоторого запаса):

- ослабление сигнала в полосе пропускания 3 дБ;

- неравномерность АЧХ в полосе пропускания 1 дБ;

- граничная частота полосы пропускания 8,5 МГц;

- ослабление (на частоте 16,5 МГц) в полосе задержания не хуже 58 дБ;

- сопротивление нагрузки и источника сигнала 300 Ом.

Фильтр с такими параметрами, спроектированный с помощью системы схемотехнического моделирования Micro-Cap 7.0.0 показан на рис. 8.3.9, а его АЧХ с отметками на точках 8 МГц и 17 МГц – на рис. 8.3.10. Полученный фильтр с запасом удовлетворяет предъявляемым требованиям и может быть использован в синтезаторе по схеме рис.8.3.5.

Дата добавления: 2021-01-11; просмотров: 780;