Система команд процессора

В общем случае система команд процессора включает в себя следующие четыре основные группы команд:

* команды пересылки данных;

* арифметические команды;

* логические команды;

* команды переходов.

Команды пересылки данных не требуют выполнения никаких операций над операндами. Операнды просто пересылаются (точнее, копируются) из источника (Source) в приемник (Destination). Источником и приемником могут быть внутренние регистры процессора, ячейки памяти или устройства ввода/вывода. АЛУ в данном случае не используется.

Арифметические команды выполняют операции сложения, вычитания, умножения, деления, увеличения на единицу (инкрементирования), уменьшения на единицу (декрементирования) и т.д. Этим командам требуется один или два входных операнда. Формируют команды один выходной операнд.

Логические команды производят над операндами логические операции, например, логическое И, логическое ИЛИ, исключающее ИЛИ, очистку, инверсию, разнообразные сдвиги (вправо, влево, арифметический сдвиг, циклический сдвиг). Этим командам, как и арифметическим, требуется один или два входных операнда, и формируют они один выходной операнд.

Наконец, команды переходов предназначены для изменения обычного порядка последовательного выполнения команд. С их помощью организуются переходы на подпрограммы и возвраты из них, всевозможные циклы, ветвления программ, пропуски фрагментов программ и т.д. Команды переходов всегда меняют содержимое счетчика команд. Переходы могут быть условными и безусловными. Именно эти команды позволяют строить сложные алгоритмы обработки информации.

В соответствии с результатом каждой выполненной команды устанавливаются или очищаются биты регистра состояния процессора (PSW). Но надо помнить, что не все команды изменяют все имеющиеся в PSW флаги. Это определяется особенностями каждого конкретного процессора.

У разных процессоров системы команд существенно различаются, но в основе своей они очень похожи. Количество команд у процессоров также различно. Например, у упоминавшегося уже процессора МС68000 всего 61 команда, а у процессора 8086 — 133 команды. У современных мощных процессоров количество команд достигает нескольких сотен. В то же время существуют процессоры с сокращенным набором команд (так называемые RISC-процессоры), в которых за счет максимального сокращения количества команд достигается увеличение эффективности и скорости их выполнения.

Рассмотрим теперь особенности четырех выделенных групп команд процессора более подробно.

10.3.1. Команды пересылки данных

Команды пересылки данных занимают очень важное место в системе команд любого процессора. Они выполняют следующие важнейшие функции:

* загрузка (запись) содержимого во внутренние регистры процессора;

* сохранение в памяти содержимого внутренних регистров процессора;

* копирование содержимого из одной области памяти в другую;

* запись в устройства ввода/вывода и чтение из устройств ввода/вывода.

В некоторых процессорах (например, Т-11) все эти функции выполняются одной единственной командой MOV (для байтовых пересылок — MOVB) но с различными методами адресации операндов.

В других процессорах помимо команды MOV имеется еще несколько команд для выполнения перечисленных функций. Например, для загрузки регистров могут использоваться команды загрузки, причем для разных регистров — разные команды (их обозначения обычно строятся с использованием слова LOAD — загрузка). Часто выделяются специальные команды для сохранения в стеке и для извлечения из стека (PUSH — сохранить в стеке, POP — извлечь из стека). Эти команды выполняют пересылку с автоинкрементной и с автодекрементной адресацией (даже если эти режимы адресации не предусмотрены в процессоре в явном виде).

Иногда в систему команд вводится специальная команда MOVS для строчной (или цепочечной) пересылки данных (например, в процессоре 8086). Эта команда пересылает не одно слово или байт, а заданное количество слов или байтов (MOVSB), то есть инициирует не один цикл обмена по магистрали, а несколько. При этом адрес памяти, с которым происходит взаимодействие, увеличивается на 1 или на 2 после каждого обращения или же уменьшается на 1 или на 2 после каждого обращения. То есть в неявном виде применяется автоинкрементная или автодекрементная адресация.

В некоторых процессорах (например, в процессоре 8086) специально выделяются функции обмена с устройствами ввода/вывода. Команда IN используется для ввода (чтения) информации из устройства ввода/вывода, а команда OUT используется для вывода (записи) в устройство ввода/вывода. Обмен информацией в этом случае производится между регистром-аккумулятором и устройством ввода/вывода. В более продвинутых процессорах этого же семейства (начиная с процессора 80286) добавлены команды строчного (цепочечного) ввода (команда INS) и строчного вывода (команда OUTS). Эти команды позволяют пересылать целый массив (строку) данных из памяти в устройство ввода/вывода (OUTS) или из устройства ввода/вывода в память (INS). Адрес памяти после каждого обращения увеличивается или уменьшается (как и в случае с командой MOVS).

Также к командам пересылки данных относятся команды обмена информацией (их обозначение строится на основе слова Exchange). Может быть предусмотрен обмен информацией между внутренними регистрами, между двумя половинами одного регистра (SWAP) или между регистром и ячейкой памяти.

10.3.2. Арифметические команды

Арифметические команды рассматривают коды операндов как числовые двоичные или двоично-десятичные коды. Эти команды могут быть разделены на пять основных групп:

* команды операций с фиксированной запятой (сложение, вычитание, умножение, деление);

* команды операций с плавающей запятой (сложение, вычитание, умножение, деление);

* команды очистки;

* команды инкремента и декремента;

* команда сравнения.

Команды операций с фиксированной запятой работают с кодами в регистрах процессора или в памяти как с обычными двоичными кодами. Команда сложения (ADD) вычисляет сумму двух кодов. Команда вычитания (SUB) вычисляет разность двух кодов. Команда умножения (MUL) вычисляет произведение двух кодов (разрядность результата вдвое больше разрядности сомножителей). Команда деления (DIV) вычисляет частное от деления одного кода на другой. Причем все эти команды могут работать как с числами со знаком, так и с числами без знака.

Команды операций с плавающей запятой (точкой) используют формат представления чисел с порядком и мантиссой (обычно эти числа занимают две последовательные ячейки памяти). В современных мощных процессорах набор команд с плавающей запятой не ограничивается только четырьмя арифметическими действиями, а содержит и множество других более сложных команд, например, вычисление тригонометрических функций, логарифмических функций, а также сложных функций, необходимых при обработке звука и изображения.

Команды очистки (CLR) предназначены для записи нулевого кода в регистр или ячейку памяти. Эти команды могут быть заменены командами пересылки нулевого кода, но специальные команды очистки обычно выполняются быстрее, чем команды пересылки. Команды очистки иногда относят к группе логических команд, но суть их от этого не меняется.

Команды инкремента (увеличения на единицу, INC) и декремента (уменьшения на единицу, DEC) также бывают очень удобны. Их можно в принципе заменить командами суммирования с единицей или вычитания единицы, но инкремент и декремент выполняются быстрее, чем суммирование и вычитание. Эти команды требуют одного входного операнда, который одновременно является и выходным операндом.

Наконец, команда сравнения (обозначается CMP) предназначена для сравнения двух входных операндов. По сути, она вычисляет разность этих двух операндов, но выходного операнда не формирует, а всего лишь изменяет биты в регистре состояния процессора (PSW) по результату этого вычитания. Следующая за командой сравнения команда (обычно это команда перехода) будет анализировать биты в регистре состояния процессора и выполнять действия в зависимости от их значений. В некоторых процессорах предусмотрены команды цепочечного сравнения двух последовательностей операндов, находящихся в памяти (например, в процессоре 8086 и совместимых с ним).

Лекция 35

10.3.3. Логические команды

Логические команды выполняют над операндами логические (побитовые) операции, то есть они рассматривают коды операндов не как единое число, а как набор отдельных битов. Этим они отличаются от арифметических команд. Логические команды выполняют следующие основные операции:

* логическое И, логическое ИЛИ, сложение по модулю 2 (Исключающее ИЛИ);

* логические, арифметические и циклические сдвиги;

* проверка битов и операндов;

* установка и очистка битов (флагов) регистра состояния процессора (PSW).

Команды логических операций позволяют побитно вычислять основные логические функции от двух входных операндов. Кроме того, операция И (AND) используется для принудительной очистки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие очистки, установлены в нуль). Операция ИЛИ (OR) применяется для принудительной установки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие установки в единицу, равны единице). Операция «Исключающее ИЛИ» (XOR) используется для инверсии заданных битов (в качестве одного из операндов при этом применяется код маски, в котором биты, подлежащие инверсии, установлены в единицу). Команды требуют двух входных операндов и формируют один выходной операнд.

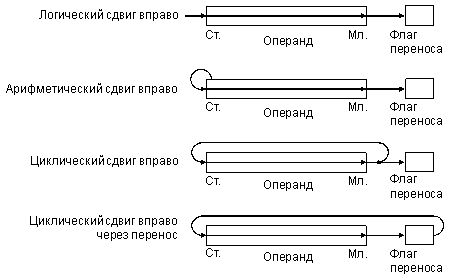

Команды сдвигов позволяют побитно сдвигать код операнда вправо (в сторону младших разрядов) или влево (в сторону старших разрядов). Тип сдвига (логический, арифметический или циклический) определяет, каково будет новое значение старшего бита (при сдвиге вправо) или младшего бита (при сдвиге влево), а также определяет, будет ли где-то сохранено прежнее значение старшего бита (при сдвиге влево) или младшего бита (при сдвиге вправо). Например, при логическом сдвиге вправо в старшем разряде кода операнда устанавливается нуль, а младший разряд записывается в качестве флага переноса в регистр состояния процессора. А при арифметическом сдвиге вправо значение старшего разряда сохраняется прежним (нулем или единицей), младший разряд также записывается в качестве флага переноса.

Циклические сдвиги позволяют сдвигать биты кода операнда по кругу (по часовой стрелке при сдвиге вправо или против часовой стрелки при сдвиге влево). При этом в кольцо сдвига может входить или не входить флаг переноса. В бит флага переноса (если он используется) записывается значение старшего бита при циклическом сдвиге влево и младшего бита при циклическом сдвиге вправо. Соответственно, значение бита флага переноса будет переписываться в младший разряд при циклическом сдвиге влево и в старший разряд при циклическом сдвиге вправо.

Для примера на рис. 3.12 показаны действия, выполняемые командами сдвигов вправо.

Команды проверки битов и операндов предназначены для установки или очистки битов регистра состояния процессора в зависимости от значения выбранных битов или всего операнда в целом. Выходного операнда команды не формируют. Команда проверки операнда (TST) проверяет весь код операнда в целом на равенство нулю и на знак (на значение старшего бита), она требует только одного входного операнда. Команда проверки бита (BIT) проверяет только отдельные биты, для выбора которых в качестве второго операнда используется код маски. В коде маски проверяемым битам основного операнда должны соответствовать единичные разряды.

Рис. 3.12. Команды сдвигов вправо.

Наконец, команды установки и очистки битов регистра состояния процессора (то есть флагов) позволяют установить или очистить любой флаг, что бывает очень удобно. Каждому флагу обычно соответствуют две команды, одна из которых устанавливает его в единицу, а другая сбрасывает в нуль. Например, флагу переноса С (от Carry) будут соответствовать команды CLC (очистка) и SEC или STC (установка).

10.3.4. Команды переходов

Команды переходов предназначены для организации всевозможных циклов, ветвлений, вызовов подпрограмм и т.д., то есть они нарушают последовательный ход выполнения программы. Эти команды записывают в регистр-счетчик команд новое значение и тем самым вызывают переход процессора не к следующей по порядку команде, а к любой другой команде в памяти программ. Некоторые команды переходов предусматривают в дальнейшем возврат назад, в точку, из которой был сделан переход, другие не предусматривают этого. Если возврат предусмотрен, то текущие параметры процессора сохраняются в стеке. Если возврат не предусмотрен, то текущие параметры процессора не сохраняются.

Команды переходов без возврата делятся на две группы:

* команды безусловных переходов;

* команды условных переходов.

В обозначениях этих команд используются слова Branch (ветвление) и Jump (прыжок).

Команды безусловных переходов вызывают переход в новый адрес независимо ни от чего. Они могут вызывать переход на указанную величину смещения (вперед или назад) или же на указанный адрес памяти. Величина смещения или новое значение адреса указываются в качестве входного операнда.

Команды условных переходов вызывают переход не всегда, а только при выполнении заданных условий. В качестве таких условий обычно выступают значения флагов в регистре состояния процессора (PSW). То есть условием перехода является результат предыдущей операции, меняющей значения флагов. Всего таких условий перехода может быть от 4 до 16. Несколько примеров команд условных переходов:

* переход, если равно нулю;

* переход, если не равно нулю;

* переход, если есть переполнение;

* переход, если нет переполнения;

* переход, если больше нуля;

* переход, если меньше или равно нулю.

Если условие перехода выполняется, то производится загрузка в регистр-счетчик команд нового значения. Если же условие перехода не выполняется, счетчик команд просто наращивается, и процессор выбирает и выполняет следующую по порядку команду.

Специально для проверки условий перехода применяется команда сравнения (CMP), предшествующая команде условного перехода (или даже нескольким командам условных переходов). Но флаги могут устанавливаться и любой другой командой, например командой пересылки данных, любой арифметической или логической командой. Отметим, что сами команды переходов флаги не меняют, что как раз и позволяет ставить несколько команд переходов одну за другой.

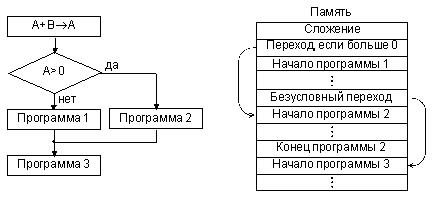

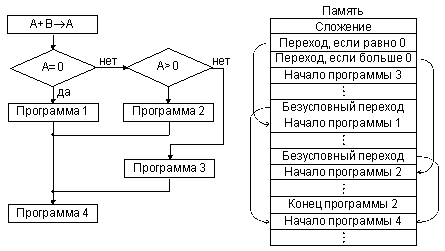

Совместное использование нескольких команд условных и безусловных переходов позволяет процессору выполнять разветвленные алгоритмы любой сложности. Для примера на рис. 3.13 показано разветвление программы на две ветки с последующим соединением, а на рис. 3.14 — разветвление на три ветки с последующим соединением.

Команды переходов с дальнейшим возвратом в точку, из которой был произведен переход, применяются для выполнения подпрограмм, то есть вспомогательных программ. Эти команды называются также командами вызова подпрограмм (распространенное название — CALL). Использование подпрограмм позволяет упростить структуру основной программы, сделать ее более логичной, гибкой, легкой для написания и отладки. В то же время надо учитывать, что широкое использование подпрограмм, как правило, увеличивает время выполнения программы.

Рис. 7.13. Реализация разветвления на две ветки.

Рис. 7.14. Реализация разветвления на три ветки.

Все команды переходов с возвратом предполагают безусловный переход (они не проверяют никаких флагов). При этом они требуют одного входного операнда, который может указывать как абсолютное значение нового адреса, так и смещение, складываемое с текущим значением адреса. Текущее значение счетчика команд (текущий адрес) сохраняется перед выполнением перехода в стеке.

Для обратного возврата в точку вызова подпрограммы (точку перехода) используется специальная команда возврата (RET или RTS). Эта команда извлекает из стека значение адреса команды перехода и записывает его в регистр-счетчик команд.

Особое место среди команд перехода с возвратом занимают команды прерываний (распространенное название — INT). Эти команды в качестве входного операнда требуют номер прерывания (адрес вектора). Обслуживание таких переходов осуществляется точно так же, как и аппаратных прерываний. То есть для выполнения данного перехода процессор обращается к таблице векторов прерываний и получает из нее по номеру прерывания адрес памяти, в который ему необходимо перейти. Адрес вызова прерывания и содержимое регистра состояния процессора (PSW) сохраняются в стеке. Сохранение PSW — важное отличие команд прерывания от команд переходов с возвратом.

Команды прерываний во многих случаях оказываются удобнее, чем обычные команды переходов с возвратом. Сформировать таблицу векторов прерываний можно один раз, а потом уже обращаться к ней по мере необходимости. Номер прерывания соответствует номеру подпрограммы, то есть номеру функции, выполняемой подпрограммой. Поэтому команды прерывания гораздо чаще включаются в системы команд процессоров, чем обычные команды переходов с возвратом.

Для возврата из подпрограммы, вызванной командой прерывания, используется команда возврата из прерывания (IRET или RTI). Эта команда извлекает из стека сохраненное там значение счетчика команд и регистра состояния процессора (PSW).

Отметим, что у некоторых процессоров предусмотрены также команды условных прерываний, например, команда прерывания при переполнении.

Конечно, в данном разделе мы рассмотрели только основные команды, наиболее часто встречающиеся в процессорах. У конкретных процессоров могут быть и многие другие команды, не относящиеся к перечисленным группам команд. Но изучать их надо уже после того, как выбран тип процессора, подходящий для задачи, решаемой данной микропроцессорной системой.

Лекция 36

10.4. Система команд микропроцессора i8086/8088

| Мнемоника | Функция команды |

| AAA | ASCII- коррекция результата сложения |

| AAD | ASCII- коррекция перед делением |

| AAM | ASCII- коррекция результата умножения |

| AAS | ASCII- коррекция результата вычитания |

| ADC | Сложение с переносом |

| ADD | Сложение |

| AND | Конъюнкция (функция И) |

| CALL | Вызов подпрограммы |

| CBW | Преобразование байта в слово |

| CLC | Сброс флага переноса |

| CLD | Сброс флага направления |

| CLI | Сброс флага прерывания |

| CMC | Инвертирование флага переноса |

| CMP | Сравнение операндов |

| CMPS | Сравнение символов строки |

| CWD | Преобразование слова в двойное слово |

| DAA | Десятичная коррекция результата сложения |

| DAS | Десятичная коррекция результата вычитания |

| DEC | Декремент операнда |

| DIV | Беззнаковое деление |

| ESC | Переключиться на сопроцессор |

| HLT | Останов |

| IDIV | Знаковое деление |

| IMUL | Знаковое умножение |

| IN | Ввод операнда из порта |

| INC | Инкремент операнда |

| INT | Прерывание |

| INTO | Прерывание при переполнении |

| IRET | Возврат из прерывания |

| JB (JBNAF) | Переход, если ниже |

| JBE (JNA) | Переход, если ниже или равно |

| JE (JZ) | Переход, если равно |

| JL (JNGE) | Переход, если меньше |

| JLE (JNG) | Переход, если меньше или равно |

| JLNE (JG) | Переход, если больше |

| JMP | Безусловный переход |

| JNB (JAE) | Переход, если не ниже |

| JNBE (JA) | Переход, если выше |

| JNE (JNZ) | Переход, если не равно |

| JNL (JGE) | Переход, если не меньше |

| JNO | Переход, если нет переполнения |

| JNP (JPO) | Переход, если нечетность |

| JNS | Переход, если положительный знак |

| JO | Переход, если переполнение |

| JP (JPE) | Переход, если четность |

| JS | Переход, если отрицательный знак |

| LAHF | Загрузка признаков в регистр AH |

| LDS | Загрузка селектора в регистр DS |

| LEA | Загрузка эффективного адреса в регистр |

| LES | Загрузка селектора в регистр ES |

| LOCK | Префикс захвата шины |

| LODS | Загрузка символа строки |

| LOOP | Реализация цикла |

| LOOPE (LOOPZ) | Зациклить, если равно (если нуль) |

| LOOPNE (LOOPNZ) | Зациклить, если не равно (если не нуль) |

| MOV | Пересылка данных |

| MOVS | Пересылка символа строки |

| MUL | Беззнаковое умножение |

| NEG | Перемена знака |

| NOP | Отсутствие операции |

| NOT | Логическая инверсия (операция НЕ) |

| OR | Дизъюнкция (операция ИЛИ) |

| OUT | Вывод операнда в порт |

| POP | Чтение операнда из стека |

| POPF | Чтение из стека содержимого регистра флагов |

| PUSH | Запись операнда в стек |

| PUSHF | Запись в стек содержимого регистра флагов |

| RCL | Циклический сдвиг влево |

| RCR | Циклический сдвиг вправо |

| REP | Префикс повторения операции со строками символов |

| REPE (REPZ) | Повторение при совпадении (при равенстве нулю) |

| REPNE (REPNZ) | Повторение для несовпадения (при неравенстве нулю) |

| RET | Возврат из подпрограммы |

| ROL | Циклический сдвиг влево через перенос |

| ROR | Циклический сдвиг вправо через перенос |

| SAHF | Запись содержимого AH в регистр флагов |

| SAL (SHL) | Арифметический сдвиг влево |

| SAR | Арифметический сдвиг вправо |

| SBB | Вычитание с заемом |

| SCAS | Сканирование строк символов |

| SHR | Логический сдвиг вправо |

| STC | Установка флага переноса |

| STD | Установка флага направления |

| STI | Установка флага прерываний |

| STOS | Запись символов в строку |

| SUB | Вычитание |

| TEST | Логическое сравнение операндов |

| WAIT | Ожидание |

| XCHG | Обмен операндов |

| XLAT | Преобразование кодов |

| XOR | Исключающее ИЛИ |

Лекция 37

1.1. Краткие теоретические сведения

1.1.1. Архитектура микроЭВМ

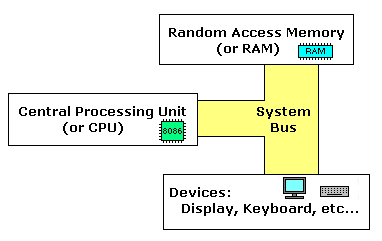

В микроЭВМ, построенных на базе микропроцессоров (МП), все связи между отдельными функциональными блоками осуществляются шинами. Под шиной подразумевается физическая группа линий передачи сигналов, обладающих функциональной общностью (по каждой линии передается один двоичный разряд информации).

Язык ассемблера - язык низкого уровень программирования. Вы должны получить некоторое знание относительно компьютерной структуры, чтобы понять что-нибудь. Простая структура микроЭВМ:

Системная шина - подключает различные компоненты компьютера.

CPU (микропроцессор) - сердце компьютера, большинство вычислений происходит внутри микропроцессора.

RAM (Оперативная память) - место, где программы загружены, чтобы быть выполняемыми.

Физически шины реализуются в виде параллельных проводящих полосок печатной платы или в виде связанных в жгут проводов. Так, например, в эмуляторе Emu8086, организованном на основе микропроцессора 8086, данные передаются к различным его функциональным узлам параллельно по линиям. Эта группа линий передачи данных называется шиной данных. Кроме шины данных, в микроЭВМ выделяют шину адресов и шину управления, служащих соответственно для передачи адресов и управляющих сигналов. Микро-ЭВМ с такой организацией связей относят к системам, основанным на архитектуре с тремя шинами.

Линии шины адреса (ША) и шины управления (ШУ) являются однонаправленными, то есть сигналы по линиям этих шин передаются только в одном направлении. Передаваемые по ША сигналы формируются в МП. Они необходимы для определения пути передачи данных внутри микроЭВМ, например для выбора ячейки памяти, куда необходимо занести или откуда необходимо считать информацию. В определении тракта передачи данных могут принимать участие и управляющие сигналы, подсоединяющие или, напротив, блокирующая восьмиразрядной, что позволяет обращаться к 65536 ячейкам памяти и внешним устройствам.

В отличие от ША и ШУ шина данных (ШД) является шиной двунаправленной. Данные по линиям шины могут передаваться от микропроцессора к какому-либо устройству микроЭВМ или пересылаться в МП от какого-либо устройства, доступ к которому обеспечивают сигналы адресной шины.

Естественно, что в каждый момент времени данные могут передаваться лишь в одном направлении, определяемом режимом работы микропроцессора. К основным режимам работы МП можно отнести:

1) запись данных в память машины;

2) чтение данных из памяти машины;

3) пересылку данных в устройство ввода/вывода;

4) чтение данных с устройства ввода/вывода;

5) выполнение операций с содержимым внутренних регистров микропроцессора.

При реализации последнего режима внешние по отношению к МП шины микроЭВМ не используются, то есть все действия происходят внутри МП. Реализация первых четырех режимов оказывает определяющее влияние на работу шины данных.

Работа по реализации программы любой микроЭВМ, построенной по типу архитектуры с тремя шинами, состоит в выполнении следующих действий для каждой команды программы:

1) микропроцессор формирует адрес, по которому хранится команда, переводя в соответствующее состояние шину адреса;

2) команда считывается из памяти по сформированному адресу и пересылается в микропроцессор;

3) команда дешифрируется (идентифицируется) микропроцессором;

4) микропроцессор "настраивается" на выполнение одного из перечисленных выше пяти основных режимов в соответствии с результатами дешифрирования считанного из памяти кода команды.

Перечисленные выше пять режимов являются основными, но не единственно возможными.

1.1.2. Функциональная схема микропроцессора 8086.

При работе с микроЭВМ пользователю необходимо иметь информацию о структуре МП: числе и назначении регистров и специальных указателей; о системе команд. Число, назначение регистров, флагов и команд пользователь изменить не может. Он может изменить лишь содержимое регистров и использовать команды в любой нужной ему комбинации.

Под регистром подразумевается специальное запоминающее устройство, состоящее из элементов (триггеров), имеющих два устойчивых состояния. Число элементов регистра определяет разрядность. Большинство регистров микропроцессора восьмиразрядные и лишь некоторые шестнадцатиразрядные. Все регистры разбиты на группы и отличаются различным функциональным назначением. Некоторые регистры имеют специальное назначение, другие - многоцелевое. Количество и назначение регистров в микропроцессоре зависит от его архитектуры. Кроме того, различают программно-недоступные и программно-доступные регистры.

Рассмотрим структуру микропроцессора.

Дата добавления: 2016-07-05; просмотров: 8609;