Архитектура компьютера

Архитектура ЭВМ – это абстрактное представление ЭВМ, которое отражает ее структурную, схемотехническую и логическую организацию. Понятие архитектуры ЭВМ является комплексным и включает в себя следующее:

à структурную схему ЭВМ;

à средства и способы доступа к элементам структурной схемы;

à набор и доступность регистров;

à организацию и способы адресации памяти;

à способы представления и форматы данных;

à организацию и разрядность интерфейсов;

à набор машинных команд;

à форматы машинных команд;

à обработку нештатных ситуаций (прерываний).

Программы могут взаимодействовать с устройствами разными способами:

Ø используя вызовы функций операционной системы (DOS, API);

Ø используя вызовы функций базовой системы ввода/вывода (BIOS);

Ø непосредственно взаимодействуя с регистрами периферийных устройств или контроллеров интерфейсов.

Обилие вариантов взаимодействия связано с необходимостью совместимости с младшими моделями компьютера. Любой PC-совместимый компьютер имеет следующие характерные черты:

Ø процессор, совместимый с семейством x86 фирмы Intel;

Ø единую систему распределения пространства адресов памяти;

Ø унифицированное распределение адресов пространства ввода/вывода с фиксированным положением обязательных портов;

Ø систему аппаратных прерываний;

Ø систему прямого доступа к памяти;

Ø набор системных устройств и интерфейсов ввода/вывода;

Ø унифицированные по конструктиву и интерфейсу шины расширения;

Ø базовую систему ввода/вывода (BIOS).

Стандартная архитектура компьютера определяет набор обязательных средств ввода/вывода и средств поддержки периферии – системы аппаратных прерываний (i8259A) и прямого доступа к памяти (i8237A). К обязательным стандартизованным средствам ввода/вывода относятся:

à трехканальный счетчик (XT – i8253, AT – i8254);

à интерфейс клавиатуры и управления (XT – i8255, AT – i88042);

à канал управления звуком;

à графический адаптер

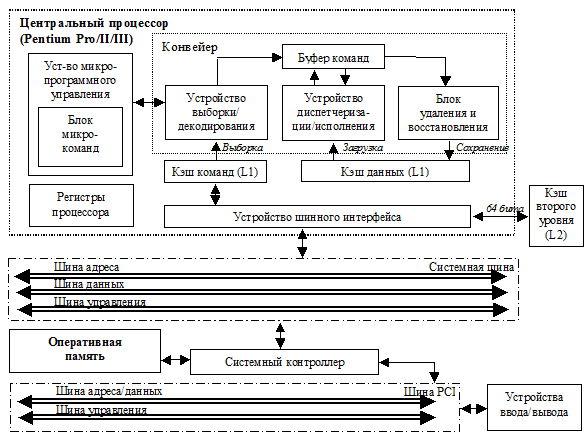

Рассмотрим сложившуюся архитектуру персонального компьютера.

Рис. 4.1. Структурная схема персонального компьютера.

Любая запущенная программа получает в свое распоряжение определенный набор ресурсов микропроцессора. Эти ресурсы необходимы для выполнения и хранения в памяти команд программы, данных и информации о текущем состоянии программы и микропроцессора. Набор этих ресурсов представляет собой программную модель микропроцессора.

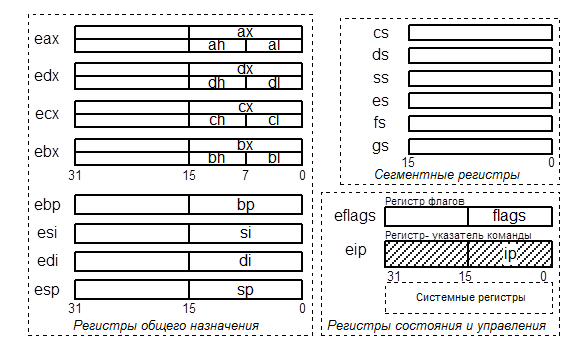

Программную модель микропроцессора составляют:

à набор регистров общего назначения (32 бита: eax, ax, ah, alàa, d, с, b; ebp, bp àbp, si, di, sp);

à набор сегментных регистров (16 бит: cs, ds, ss, es, fs, gs);

à набор регистров состояния и управления (32 бита: eip, eflags и т.д.);

à пространство адресуемой памяти (236-1 Pro/II/III,232-1 i486/Pentium);

à набор регистров устройства вычислений с плавающей точкой (сопроцессора) (80 бит: st(0)..st(7));

à набор регистров целочисленного MMX-расширения (64 бит: mmx0…mmx7);

à набор регистров MMX-расширения с плавающей точкой (128 бит: xmm0…xmm7);

à программный стек.

Рис. 4.2. Основные наборы регистров.

Регистры общего назначения(РОН) используются в программах для хранения операндов логических и арифметических операций; компонентов адреса и указателей на ячейки памяти. Основное применение РОН:

à eax/ax/ah/al (Accumulator register) – аккумулятор. Применяется для хранения промежуточных данных. В некоторых командах использование этого регистра обязательно;

à ebx/bx/bh/bl (Base register) – базовый регистр. Применяется для хранения базового адреса объекта;

à ecx/cx/ch/cl (Count register) – регистр-счетчик. Применяется в командах, производящих повторяющиеся действия;

à edx/dx/dh/dl (Data register) – регистр данных. Так же как и регистр eax/ax/ah/al он хранит промежуточные данные;

à esi/si (Source Index register) – индекс источника;

à edi/di (Destination Index register) – индекс приемника;

à esp/sp (Stack Pointer register) – регистр указателя стека. Содержит указатель вершины стека в текущем сегменте стека;

à ebp/bp (Base Pointer register) – регистр указателя базы кадра стека.

В программной модели микропроцессора имеется шесть сегментных регистров. Это обусловлено аппаратной организацией использования оперативной памяти микропроцессорами Intel в виде трех частей, называемых сегментами. Существуют следующие типы сегментов:

1. Сегмент кода. Содержит команды программы, которые микропроцессор загружает в конвейер. Для доступа к сегменту служит регистр cs (code segment register) – сегментный регистр кода.

2. Сегмент данных. Содержит обрабатываемые программой данные. Для доступа к этому сегменту служит регистр ds (data segment register) – сегментный регистр данных, который хранит адрес сегмента данных текущей программы.

3. Сегмент стека. Область памяти, в которую микропроцессор записывает данные по принципу LIFO (last-in-first-out) – последним вошел, первым вышел. Для доступа к этому сегменту служит регистр ss (stack segment register) – сегментный регистр стека, содержащий адрес сегмента стека.

4. Дополнительный сегмент данных. Если программе не достаточно одного сегмента данных, то она имеет возможность использовать еще три дополнительных. Адреса дополнительных сегментов данных должны содержаться в регистрах es, gs, fs.

Регистры состояния и управлениясодержат информацию о текущем состоянии микропроцессора и команды, которая в данный момент загружена в конвейер:

à регистр флагов eflags/flags (flag register). Регистр используется побитно, т.е. каждый бит имеет определенное функциональное назначение, который называется флагом;

à регистр указателя программы eip/ip (instruction pointer register). Этот регистр непосредственно не доступен программисту и содержит смещение следующей подлежащей выполнению команды относительно содержимого сегментного регистра cs в текущем сегменте команд.

Организация памяти

Физическая память компьютера организована как последовательность ячеек – байтов. Каждому байту соответствует свой уникальный адрес, называемый физическим. Диапазон физических адресов зависит от разрядности шины адреса микропроцессора. Для i486 и Pentium он находится в пределах от 0 до 232-1 (4Гб). Для микропроцессоров семейства P6 – от 0 до 236–1 (64Гб). Аппаратно микропроцессор поддерживает две модели использования оперативной памяти:

à сегментированная модель;

à страничная модель – надстройка над сегментированной моделью. Основное применение связано с организацией виртуальной памяти, что позволяет операционной системе использовать пространство памяти больше, чем объем физической оперативной памяти,

и может работать в следующих режимах:

à режим реальных адресов;

à защищенный режим;

à режим виртуального i8086;

à режим системного управления.

Программы никогда не указывают физические адреса памяти, а работают только с логическими адресами. Это верно для всех режимов работы процессора.

Различают три модели логической организации памяти:

Ø сегментированная модель памяти реального режима (MS-DOS);

Ø сегментированная модель памяти защищенного режима (Windows 9x);

Ø сплошная модель памяти защищенного режима (Windows NT).

Дата добавления: 2020-02-05; просмотров: 941;