Архитектура контроллера прямого доступа к памяти КР580ВТ57

. Контроллер прямого доступа к памяти (КПДП) генерирует управляющие сигналы, необходимые для организации обмена. КПДП содержит четыре канала прямого доступа, каждый из которых обеспечивает передачу блока данных размером до 16К байт с произвольным начальным адресом в диапазоне от 0 до 64К байт [5, 8, 9].

Упрощенная структурная схема КПДП приведена на рис. 2.15,а. В состав БИС входят: двунаправленный двустабильный буфер данных (BD), предназначенный для обмена информацией между МП и КПДП; схема управления чтением/записью (RWCU), адресующая внутренние регистры КПДП и управляющая обменом по шине D(7 — 0); блок управления (СU), содержащий регистры режима и состояния КПДП и обеспечивающий последовательность операций, необходимую для организации режима прямого доступа к памяти; блок управления приоритетами (PCU), обеспечивающий определенный порядок обслуживания запросов внешних устройств: четыре канала прямого доступа (СНО — СНЗ). Каждый, из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

Назначение входных. выходных и управляющих сигналов КПДП приведено при описании выводов микросхемы в табл. 2.15

рис.2.15

рис.2.15

При подключении КПДП к шинам микроЭВМ младший байт адреса памяти выдается по линиям А(3-0) и А(7-4). а старший байт — через шину D(7 — 0). поэтому КПДП обычно подключается вместе с буферным регистром. Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12 показана на рис. 2.15,б.

Для начальной установки КПДП необходимо записать соответствующую информацию в 16-разрядный регистр адреса канала (RGA). в 16-разрядный счетчик циклов канала (СТ) и в 8-разрядный регистр режима, общий для всех каналов. Запись этой информации производится с помощью команды OUT, хотя возможен и другой способ обращения к КПДП как к ячейкам памяти. Запись информации в 16-разрядные регистры осуществляется двумя командами, начиная с младшего байта. Два старших разряда счетчика циклов определяют операцию обмена следующим образом: запись в память — 01. чтение из памяти — 10, контроль — 00 (комбинация 11 запрещена). Состояние КПДП можно контролировать чтением содержимого RGA, СT и 8-разрядного регистра состояния, общего для всех каналов, с помощью команды IN. Для чтения содержимого 16-разрядного регистра используются две команды IN с одной и той же адресной частью, причем сначала происходит считывание младшего байта. В табл. 2.16 приведены коды адресных выводов А(3 — 0) и значение сигнала CS для адресации внутренних регистров КПДП. При программировании КПДП операции записи управляющих слов или чтения состояний внутренних регистров определяются также значениями сигналов

i | or и I | OW.

| Обозначение вывода | Номер контакта | Назначение вывода |

| D(7-0) | 21; 22; 23; 26; 27; 28; 29; 30 | Входы/выходы данных для обмена с МП |

| I | OR | Чтение ввода/вывода — двунаправленный тристабильный вход/выход; входной сигнал L-уровня разрешает чтение ин формации из КПДП в МП; выходной сигнал L-уровня разрешает чтение из ВУ | |

| I | OW | Запись ввода/вывода — двунаправленный тристабильный вход/выход; входной сигнал L-уровня разрешает программирование КПДП; выходной сигнал L-уровня разрешает запись в ВУ | |

| CLK | Вход тактовых импульсов | |

| RESET | Вход установки 0 | |

| А(З-О) | 35; 34; 33; 32 | Двунаправленные тристабильные адресные выводы |

| CS | Выбор микросхемы | |

| A(7-4) | 40; 39; 38; 37 | Тристабильные адресные выходы |

| READY | Готовность — входной сигнал H-уровня указывает на готовность к обмену | |

| HRQ | Запрос захвата — выходной сигнал H-уровня указывает на запрос о доступе КПДП к системным шинам | |

| HLDA | Подтверждение захвата — входной сигнал H-уровня указывает на возможность доступа к системным шинам | |

| MEMR | Чтение из памяти — тристабильный выход; выходной сигнал L-уровня разрешает чтение из ячейки памяти, адресуемой КПДП | |

| MEMW | Запись в память — тристабильный выход; выходной сигнал L-уровня разрешает запись в ячейку, адресуемую КПДП | |

| AEN | Разрешение адреса — сигнал H-уровня используется для блокировки некоторых шин адреса и данных | |

| ADSTB | Строб адреса — сигнал H-уровня указывает на нахождение на шине D(7 — 0) старшего байта адреса ЗУ | |

| TC | Конец счета — сигнал H-уровня определяет выполнение последнего цикла передачи блока данных | |

| MARK | Маркер — сигнал H-уровня указывает, что до конца передаваемого блока необходимо выполнить число циклов обмена кратное 128 | |

| DRQ3- DRQO | 16; 17; 18; 19 | Запросы прямого доступа к памяти каналов СНЗ—СН0: сигнал H-уровня указывает на запрос от ВУ |

| DACK3- DACK0 | 15; 14; 24; 25 | Подтверждение запросов прямого доступа к памяти каналов СНЗ—СНО: сигнал L-уровня указывает на разрешение обмена |

| Ucc | Напряжение питания (+5 В) | |

| GND | » » (0 В) |

Таблица 2.16 Адресация внутренних регистров КПДП

| Регистр | Сигналы управления | ||||

| CS | A3 | A2 | А1 | А0 | |

| RQ0 | |||||

| СТ0 | |||||

| RQ1 | |||||

| CT | |||||

| RQ2 | |||||

| CT2 | |||||

| RQ3 | |||||

| СТЗ | |||||

| Регистр режима (запись) | |||||

| Регистр состояния (чтение) | |||||

| NOP* | X | X | X | X | |

| Примечания. 1. NOP — означает отключение КПДП от шины данных. 2. X — произвольное состояние (X ?[0;1]). |

Формат управляющего слона, записываемого в регистр режима, приведен на рис. 2.15,в. Разряды D3-D0(ЕN3 - ЕN0) задают разрешение обмена по соответствующему каналу, запись нуля в разряд запрещает обмен. Остальные разряды определяют режимы работы канала.

Разряд D4(RP) устанавливает порядок обслуживания запросов от каналов. При RP = 0 задается фиксированный приоритет каналов, и канал 0 имеет высший приоритет. В режиме циклического приоритета (RP= 1) после обслуживания канала ему присваивается низший приоритет, а следующему за ним по номеру каналу — высший. Причем циклический сдвиг приоритетов производится после каждого цикла прямого доступа.

Режим расширенной записи (EW=1) увеличивает за счет смещения переднего фронта длительность сигналов I | OW и MEMW. генерируемых КПДП. Это позволяет ВУ, формирующему сигнал READY по фронту сигнала записи, уменьшить время охлаждения и увеличить скорость обмена.

При TCS = 1 появление сигнала ТС в одном из каналов сбрасывает соответствующий разряд D3 — DO, в результате чего канал отключается. Дальнейшая работа этого канала возможна после перезагрузки регистра режима. Если TCS=0. то появление сигнала ТС не воздействует на разряд разрешения работы канала и заканчивать передачу должно ВУ за счет прекращения выработки сигнала DRQ.

В режиме автозагрузки (AL=l) может работать только второй канал, используя содержимое своих внутренних регистров и внутренних регистров третьего канала. После передачи данных в соответствии с параметрами регистров второго канала и появления сигнала ТС параметры из регистров третьего канала автоматически загружаются в регистры второго канала: флаг обновления (UF) в регистре состояния каналов (рис. 2.15,г) устанавливается в 1. Затем передача данных продолжается в соответствии с новыми параметрами регистров второго канала, а в конце первого же цикла прямого доступа с новыми параметрами флаг UF сбрасывается. Режим автозагрузки позволяет организовать повторяющиеся пересылки блоков данных с одинаковыми параметрами или соединять несколько блоков с разными параметрами.

Разряды D3 — D0 регистра состояний (рис. 2.15,г) устанавливаются одновременно с появлением сигнала ТС соответствующего канала и сбрасываются сигналом RESET при чтении содержимого регистра состояний. Считывание регистра состояний на флаг UF (разряд D4) не влияет; флаг можно сбросить установкой 0 в разряде D7 регистра режима.

Если два старших разряда счетчика циклов канала устанавливают режим контроля (VERIFY). то передача данных не производится, так как не генерируются сигналы управления записью и чтением, все остальные функции прямого доступа сохраняются. Этот режим может использоваться ВУ для контроля принятых данных.

Работу КПДП поясняет диаграмма состояний (рис. 2.15,д) и временные диаграммы основных сигналов (рис. 2.16).

рис.2.16

В начальном состоянии SI запрограммированный на определенный режим КПДП ожидает запроса DRQ от ВУ. Переходя в состояние So. он вырабатывает сигнал HRQ и ожидает поступления от МП сигнала HLDA. После поступления сигнала подтверждения HLDA начинается цикл обмена. В состоянии SI формируется сигнал AEN для блокировки других устройств системы от шин данных и управления, выдается код младших разрядов на выходы А(7-0), а код старших разрядов — на выходы D(7 — 0).

Выдача старших разрядов адреса сопровождается стробирующим сигналом ADSTB для записи их во внешний буферный регистр. В состоянии S2 вырабатывается сигнал DACK. указывающий на начало обмена, а также формируются пары сигналов MEMR, I | OR и МЕMW, I / OW, определяющие направление обмена. В состоянии S3 происходит передача данных в ЗУ или ВУ. Состояние S4 завершает цикл прямого доступа. В этом состоянии при передаче последнего байта выдается сигнал ГС. а в случае конца блока — сигнал MARK. При необходимости согласования быстродействия ЗУ и ВУ с помощью сигнала READY между состояниями S3 и S4 вводится требуемое число состояний ожидания SW. В режиме контроля переход в состояние SW не разрешается.

. Архитектура БИС параллельного интерфейса КР580ВВ55

БИС программируемого параллельного интерфейса КР580ВВ55 предназначена для организации ввода вывода параллельной информации различного формата и позволяет реализовать большинство известных протоколов обмена по параллельным каналам [8. 9]. БИС программируемого параллельного интерфейса (ППИ) может использоваться для сопряжения микропроцессора со стандартным периферийным оборудованием (дисплеем, телетайпом, накопителем).

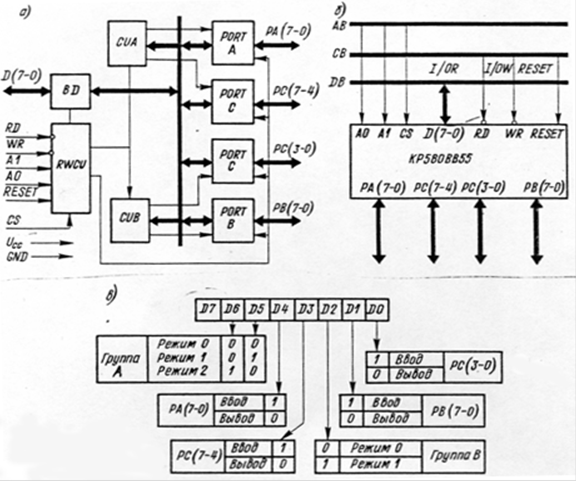

Структурная схема ППИ приведена на рис. 2.11.а. В состав БИС входят: двунаправленный 8-разрядный буфер данных (BD). связывающий ППИ с системной шиной данных: блок управления записью/чтением IRWCU). обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (PORT А. В и С) для обмена информацией с внешними устройствами: схема управления группой A (CUA). вырабатывающая сигналы управления каналом А и старшими разрядами канала С[PC(7 — 4)1: схема управления группой В (CUB). вырабатывающая сигналы управления каналом В и младшими разрядами канала С [PC(3 -О)].

Назначения входных, выходных и управляющих сигналов ППИ приведены при описании выводов микросхемы в табл. 2.13 Сопряжение БИС КР580ВВ55 со стандартной системной шиной показано на рис. 2.11,6. Сигналы управления работой ППИ подаются на блок RWCU (рис. 2.11,а) и вместе с адресными входами А0, А1 задают вид операции, выполняемой БИС (табл. 2.14)

Режим работы каждого из каналов ППИ программируется с помощью управляющего слова. Управляющее слово может задать один из трех режимов: основной режим ввода/вывода (режим 0), стробируемый ввод/вывод (режим 1). режим двунаправленной передачи информации (режим 2). Одним управляющим словом можно установить различные режимы работы для каждого из каналов. Формат управляющего слова представлен на рис. 2.11, в.

.

.

Рис.2.11

Канал А мелеет работать в любом из трех режимов, канал В - в режимах 0 и 1. Канал С может быть использован для передачи данных только в режиме 0, а в остальных режимах он служит для передачи управляющих сигналов, сопровождающих процесс обмена по каналам .4 и В.

Разряд D7 управляющего слова (рис. 2.11, в) определяет либо установку режимов работы каналов (D7 = 1), либо работу ППИ в режиме сброса/установки отдельных разрядов канала C(D7=0). При поразрядном управлении каналом С разряды D3 — D1 определяют номер модифицируемого разряда; разряд D0 задает сброс (D0 = 0) или установку (D0 = 1) модифицируемого разряда; разряды D6 — D4 но используются.

Сброс/ установку разрядов канала С можно использовать для выработки сигналов запроса прерывания от ППИ. Для каждого из каналов А и В в ППИ имеется триггер разрешения прерывания, установка сброс которого осуществляется управляющим словом установки/ сброса определенного разряда канала С. Если триггер разрешения прерывания соответствующего канала установлен (INTE=1). то ППИ может сформировать сигнал запроса прерывания при готовности внешнего устройства к вводу или выводу

Режим 0 применяется при синхронном обмене или при программной организации асинхронного обмена. Микросхема может рассматриваться в этом режиме как устройство, состоящее из четырех портов (два 8-разрядных и два 4-разрядных), независимо настраиваемых на ввод или вывод. Вывод информации осуществляется по команде 0UТ микропроцессора с фиксацией выводимой информации в регистрах каналов, а ввод — по команде IN без запоминания информации

Режим 1 обеспечивает стробируемый однонаправленный обмен информацией с внешним устройством. Передача данных производится по каналам А и В, а линии канала С управляют передачей. Работу канала в режиме 1 сопровождают три управляющих сигнала. Если один из каналов запрограммировать на режим 1, то остальные 13 интерфейсных линий можно использовать в режиме 0. Если оба канала запрограммированы на режим 1. то оставшиеся две интерфейсные линии канала С могут быть настроены на ввод или вывод.

Таблица 2.13. Описание выводов ППИ

| Обозначение вывода | Номер контакта | Назначение вывода |

| D(7-0) | 27; 28; 29: 30; 31; 32; 33; 34 | Вход/выход данных |

| RD | Чтение; L-уровень сигнала разрешает считывание информации из регистра, адресуемого по входам АО, А1 на шину D(7—0) | |

| WR | Запись; L-уровень сигнала разрешает запись информации с шины D(7—0) в регистр ППИ, адресуемый по входам АО, А1 | |

| АО, А1 | 9; 8 | Входы для адресации внутренних регистров ППИ |

| RESET | Сброс; Н-уровень сигнала обнуляет регистр управляющего слова и устанавливает все порты в режим ввода | |

| CS | Выбор микросхемы; L-уровень сигнала подключает ППИ к системной шине | |

| РА(7-0) | 37; 38; 39; 40; 1; 2; 3; 4 | Вход/выход канала А |

| РВ(7-0) | 15; 24; 23; 22; 21; 20; 19; 18 | Вход/выход канала В |

| РС(7-0) | 10; 11; 12; 13; 17; 16; 15; 14 | Вход/выход канала С |

| Ucc | Напряжение питания (+5 В) | |

| GND | » » (0 В) |

В режиме 1 для ввода информации используются следующие управляющие сигналы: строб приема (STB) - входной сигнал, формируемый внешним устройством: указывает на готовность ВУ к вводу информации: подтверждение приема (IBF) — выходной сигнал ППИ. сообщающий ВУ об окончании приема данных в канал; формируется по спаду STB: запрос прерывания (INTR) — выходной сигнал ППИ. информирующий МП о завершении приема информации в канале; H-уровень сигнала устанавливается при STB=L 1BF= 1 и INTE=1; сбрасывается спадом сигнала RD.

Таблица 2.14. Операции, задаваемые управляющими сигналами ППИ

| Операция | Сигналы управления | ||||

| CS | RD | WR | A1 | A0 | |

| Запись управляющего слова из МП | |||||

| Запись в канал А | |||||

| » » » В | |||||

| » » » С | |||||

| Чтение из канала А | |||||

| » » » В | |||||

| » » » С | |||||

| Отключение ППИ от D(7-0) | X | X | X | X | |

| Примечание. X -безразличное состояние сигнала. |

Для операции ввода управление сигналом INTE канала А осуществляется по линии РС4, а канала В — по линии РС2.

Для вывода информации в режиме 1 используются следующие управляющие сигналы: строб записи (OBF) — выходной сигнал, указывающий внешнему устройству о готовности к выводу; формируется по фронту WR; подтверждение записи (АСК) — входной сигнал от внешнего устройства, подтверждающий прием информации из ППИ; запрос прерывания (INTR) — выходной сигнал ППИ, информирующий МП о завершении операции вывода информации; H-уровень сигнала устанавливается по фронту сигнала АСК при OBF=1 и INTR = l; сбрасывается спадом сигнала WR.

Для операции вывода управление сигналом INТЕ канала А осуществляется по линии РС6, а канала В - по линии РС2.

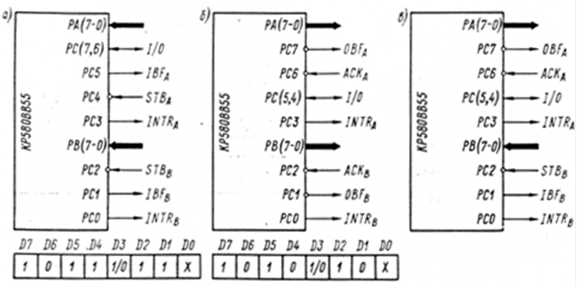

На рис. 2.12,а приведен пример конфигурации ППИ в режиме 1и соответствующее ему управляющее слово для ввода по каналам А, В, а на рис. 2.12,б — для вывода. Не используемые для передачи управляющих сигналов линии РС7, РС6 (рис. 2.12,а) и РС5, РС4 (рис. 2.12,б) могут быть запрограммированы на ввод (DЗ=1) или вывод (D3=0). На рис. 2.12. в приведен вариант конфигурации ППИ в режиме 1 для вывода информации по каналу А и ввода по каналу В. Управляющее слово этого варианта имеет вид 1011D311X, где D3 определяет работу линий РС5, РС4 на ввод или вывод.

рис.2.12

Режим 2 обеспечивает двунаправленную передачу информации по каналу А к внешнему устройству и обратно. Процесс обмена сопровождают пять управляющих сигналов, подаваемых по линиям РС7 — РСЗ. Оставшиеся 11 интерфейсных линий могут настраиваться на режим 0 или режим 1. Распределение сигналов по интерфейсным линиям и управляющее слово режима 2 приведены на рис. 2.14,а. Разряд D0 в этой конфигурации ППИ определяет настройку на ввод или вывод интерфейсных линий РС2, РС1 и РС0. Функции управляющих сигналов аналогичны рассмотренным выше сигналам для режима 1. Управление установкой внутреннего сигнала INTE для операции ввода осуществляется по линии РС4, а для операции вывода — по линии РС6

. Временная диаграмма работы ППИ в режиме 2 представлена на рис. 2.14,б.

На рис. 2.14,в показан один из возможных вариантов комбинированного режима работы ППИ, в котором канал А запрограммирован на режим 2, а канал В — на вывод в режиме 1.

В режимах 1 и 2 возможно проведение контроля за состоянием работы внешнего устройства и ППИ. Контроль осуществляется чтением слова-состояния канала

С по команде OUT. Форматы слова-состояния показаны на рис. 2.14,г. Для режима 1 сигналы I/O в разрядах с определенными номерами указывают на операцию ввода или вывода по интерфейсным линиям канала С с такими же номерами. Для режима 2 значения разрядов D2 — D0 определяются только режимом работы группы В.

Рис.2.14

Дата добавления: 2017-06-13; просмотров: 2409;