Тема 3.4 Основные команды процессора

Форматы команды

Микропроцессор К1810ВМ86 относится к классу однокристальных с фиксированной системой команд. При рассмотрении системы команд удобно обращаться к программной модели МП, содержащей его функциональные узлы (регистры), доступные программисту (рис, 2.1). Общие регистры разбиты на две группы: 1) группа HL, состоящая из регистров АХ, ВХ, СХ, DX, которые предназначены прежде всего для хранения данных и допускают раздельную адресацию их старших (Н) и младших (L) половин; 2) группа PI, содержащая указательные регистры ВР, SP и индексные регистры SI, DI, в которых обычно хранится адресная информация. Для общих и сегментных регистров указаны коды, используемые в форматах команд для их адресации. Регистр флагов F и указатель команд IP адресуются в командах неявно.

| Общие регистры | ||||||||||||||||

| AH(100) | AL(000) | |||||||||||||||

| HL | CH(101) | CL(001) | ||||||||||||||

| DH(110) | DL(010) | |||||||||||||||

| BH(111) | BL(011) | |||||||||||||||

| SP | ||||||||||||||||

| PI | BP | |||||||||||||||

| SI | ||||||||||||||||

| DI | ||||||||||||||||

| Регистр | 7 6 | |||||||||||||||

| флагов | ///////// | OF | DF | IF | TF | SF | ZF | /// | AF | /// | /// | PF | /// | CF | ||

| Указатель | ||||||||||||||||

| команд | IP | |||||||||||||||

| ES | ||||||||||||||||

| Сегментные | CS | |||||||||||||||

| регистры | SS | |||||||||||||||

| DS | ||||||||||||||||

Рис 2.1 Программно-доступные регистры МР ВМ68

Команды МП ВМ86 могут адресовать один или два операнда, причем двухоперандные команды являются, как правило, симметричными, так как результат операции может быть направлен на место любого из операндов. Однако в таких командах один из операндов должен обязательно располагаться в регистре, поскольку имеются команды типа регистр — регистр, регистр — память и память — регистр, но команды типа память — память отсутствуют (за исключением команды пересылки цепочки байт или слов).

В общем виде формат двухоперанднон команды приведен на рис. 2.2, а, где штриховыми линиями обозначены необязательные байты команды. Первый байт команды содержит код операции СОР и два однобитовых поля: направления d и слова w. При d = 1 осуществляется передача операнда или результата операции в регистр, который определяется полем reg второго байта команды; при d = 0—передача из указанного регистра. Поле w идентифицирует тип (разрядность) операндов: при w=] команда оперирует словом, при w = 0 — байтом.

| a) | COP d w | md reg r/m | disp L | disp H | ||

| b) | COP s w | md COP r/m | disp L | disp H | data L | disp H |

| c) | COP w | md COP r/m | disp L | disp H |

Рис . 2.2 Форматы двухоперандных команд

Второй байт, называемый постбайтом, определяет участвующие в операции регистры или регистр и ячейку памяти. Постбайт состоит из трех полей: md — режим, reg — регистр, г/m — регистр/память. Поле reg определяет операнд, который обязательно находится в регистре МП и условно считается вторым операндом. Поле г/m определяет операнд, который может находиться в регистре или памяти и условно считается первым. Способ кодирования внутренних регистров МП в полях reg и г/m представлен в табл. 2.1.

| Таблица 2.1 | |||||

| reg , r/m | w=0 | w=1 | reg , r/m | w=1 | w=1 |

| AL | AX | AH | SP | ||

| CL | CX | CH | BP | ||

| DL | DX | DH | SI | ||

| BL | BX | BH | DI |

Таблица 2.2

| Поле r/m | Эффективный адрес EA | Адресация |

| BX+SI+DISP | Базово - индексная | |

| BX+DI+DISP | ||

| BP+SI+DISP | ||

| BX+DI+DISP | ||

| SI+DISP | Индексная | |

| DI+DISP | ||

| BP+DISP | Базовая | |

| DX+DISP |

Отметим, что поле reg используется для указания регистра только в двухо-перандных командах. Если в команде один операнд, то он идентифицируется полем г/m, а поле reg используется для расширения кода операции.

Поле md показывает, как интерпретируется поле г/m для нахождения первого операнда: если md =11, то операнд содержится в регистре, в остальных случаях — в памяти. Когда адресуется память, поле md определяет вариант использования смешения disp, Находящегося в третьем и четвертом байтах команды:

00, disp = 0 — смещение отсутствует;

00, disp = 0 — смещение отсутствует;

md = 01, disp = disp L — команда содержит 8-битовое смещение, которое расширяется со знаком до 16 бит;

10, disp = dispH, disp L — команда содержит 16-битовое смещение.

10, disp = dispH, disp L — команда содержит 16-битовое смещение.

При md=ll реализуется косвенная адресация памяти и поле r/m определяет правила формирования эффективного адреса ЕА операнда в соответствии с табл. 2.2, где disp означает смешение, заданное в формате команды.

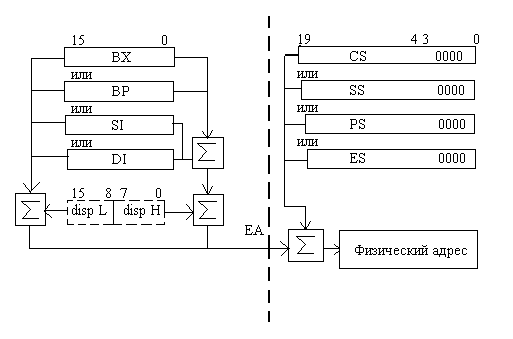

Приведенные а табл. 2.2 правила имеют одно исключение, позволяющее реализовать прямую (абсолютную) адресацию: если md = 00 и r/m=110, то EA = disp H, disp L.Таким образом, имеется три варианта интерпретации поля md и восемь вариантов интерпретации поля г/т, что дает 24 варианта вычисления эффективного адреса ЕА. Суммарные сведения о постбайтовых режимах адресации ЦП ВМ86 приведены в табл. 2.3 и на рис. 2.3.

| Таблица 2.3 | |||||

| Поле | Поле md | ||||

| r/m | |||||

| w = 1 | w = 0 | ||||

| BX+SI | BX+SI+D8 | BX+SI+D16 | AL | AX | |

| DX+DI | DX+DI+D8 | DX+DI+D16 | CL | CX | |

| BP+SI | BP+SI+D8 | BP+SI+D16 | DL | DX | |

| BP+DI | BP+DI+D8 | BP+DI+D16 | BL | BX | |

| SI | SI+D8 | SI+D16 | AH | SP | |

| DI | DI+D8 | DI+D16 | CH | SP | |

| D16 | BP+D8 | BP+D16 | DH | SI | |

| BX | BX+D8 | BX+D16 | BH | DI | |

| Примечание. D8 = disp L (однобайто- Вое смещение ) ; D16 = disp H disp L (двухбайтовое смещение) |

Рассмотренная интерпретация полей md и г/m справедлива для всех форматов команд с постбайтовой адресацией.

ОПЕРАЦИОННОЕ УСТРОЙСТВО ШИННЫЙ ИНТЕРФЕЙС

Рис 2.3 Вычисление физического адреса памяти

Рассмотренная интерпретация полей md и г/m справедлива для всех форматов команд с постбайтовой адресацией.

Подчеркнем смысловое различие двух случаев употребления термина смещение. Смещение disp, содержащееся в команде, интерпретируется как знаковое целое, которое участвует в вычислении эффективного адреса ЕА. С другой стороны, из-за сегментной организации памяти весь эффективный адрес ЕА является смещением (offset) относительно базового адреса сегмента и интерпретируется как без знаковое целое при вычислении физического адреса. В необходимых случаях во избежание ошибок будем называть offset смещением в сегменте. Наиболее общий формат двухоперандной команды с непосредственным операндом приведен на рис. 2.2,6. Необходимость адресации второго операнда отсутствует, и поле reg используется для расширения кода операции. Отсутствует также бит направления d, так как результат операции можно поместить только на место первого операнда. Место этого бита занимает бит s, который является признаком использования одного байта для задания непосредственного операнда при работе со словами. Поля s и w интерпретируются следующим образом:

|

Х0, один байт данных data L;

SW = 01, два байта данных data H, data L;

11, один байт данных, который автоматически расширяется со знаком до 16 бит.

|

Типичный формат однооперандной команды (рис. 2.2,в) содержит поля, назначение которых уже рассмотрено.

Следует отметить, что постбайтовая адресация является весьма универсальной и позволяет адресовать как общие регистры, так н ячейки памяти с указанием любого варианта вычисления эффективного адреса ЕА. Однако при адресации только регистров или аккумулятора постбайт оказывается излишним, если трех битовое поле reg разместить в первом байте команды или использовать неявную адресацию. Эта возможность реализуется в специальных (укороченных) форматах, которые содержат минимально необходимое число байтов. Специальные форматы предусмотрены для команд, выполняющих следующие часто используемые операции: включение содержимого регистра в стек, извлечение из стека в регистр, передача непосредственных данных в регистр, инкремент и декремент содержимого регистра, обмен содержимым аккумулятора АХ и регистра, пересылка между аккумулятором и ячейкой памяти с прямой адресацией, вычитание с участием содержимого аккумулятора и непосредственного операнда. В качестве примера на рис. 3.4.1 приведены стандартный и специальный форматы команды INC г. Программа-ассемблер выбирает более короткий формат команды автоматически.

| a) | 1111111 w | md 000 r/m | disp L | disp H | INC r/m |

| b) | 01000 reg | INC r |

Рис 3.4.1 Пример стандартного (а) и специального (б) форматов команды INC r

Всего можно выделить девять существенно различных форматов команд. В табл. 2.4 приведены форматы команд, не обязательные байты заключены в круглые скобки, а также указаны варианты форматов, различающихся назначением битов bi , первого байта В1 формата команды, в котором содержится код операции СОР. Звездочкой помечены специальные форматы. (В данную таблицу не включены редко используемые двухбайтовые команды ААМ и AAD, оба байта которых заняты кодом операции.)

| Таблица 2.4 | ||

| Формат | Вариант формата | Полный список команд |

| COP | CLS; CMC; STC; CLD; STD; CLI; STI; HLT; WAIT; NOP; RET; IRET; INTO; INT3; PUSHF; POPF; LANF; SAHF; XLAT; CBW; CWD; AAA; DAA; AAS; DAS; LOCK; REP; REPNZ | |

| b0 = w | CMPS; LODS; MOVS; STOS; SCAS; IN ac , DX; OUT DX, ac | |

| B2 - b0 = reg | INC r ;DEC r ; PUSH r ; POP r; XCHG AX ,r | |

| B2 - b0 = COP | PUSH sr ; POP sr | |

| B4 – b3 = sr | ||

| COP | LEA; LDS ;LES | |

| md reg r/m | b0 = w | TEST r,r ; TEST r,m; XCHG r,r; XCHG r,m; |

| (dish L) | b0 = w | MOV r,r ; MOV r,m ; MOV m,r ; ADD r,r ; |

| (dish H) | B1 = d | ADD r,m; ADD r,m; ADC r,m; ADC r,m; ADC m,r; SUB r,r; SUB m,r; SUB r,m; SBB r,r ; SBB r,m ; SBB m,r ; CMP r,r ; CMP r,m ; CMP m,r ; AND r,r; AND r,m; AND m,r; OR r,r ; OR r,m ; OR m,r ; XOR r,r; XOR r,m; XOR m,r; |

| COP | PUSH r; PUSH m; POP r; POP m; JMP (r) ; | |

| md COP r/m | CALL (r); JMP (m); CALL(m); | |

| (dial L) | b0 = w | INC m ; DEC m ;NEG ; NOT ; NUL ; IMUL ; DIV; |

| (dial H) | IDIV | |

| b0 = w | RCL;RCR;ROL; ROR; SAL;SAR;SHL;SHR | |

| b1 = v | ||

| COP | MOV m,d ; MOV r,d; AND m,d ;AND r,d ; | |

| md COP r/m | OR m,d ;OR r,d ;XOR m,d ; XOR r,d ; | |

| (disp L) | TEST m,d ; TEST r,d ; SMP m,d ; SMP r,d ; | |

| (disp H) | b0 = w | ADD m,d ; ADD r,d ; ADC m,d ; ADC r,d ; |

| data L | SUB m,d ; SUB r,d ; SBB m,d ; SBB r,d ; | |

| (data H) | ||

| COP | RET d | |

| data L | b0 = w | ADD ac,d; ADC ac,d; SUB ac,d; SBB ac,d; |

| (data H) | CMP ac,d; ADD ac,d; OR ac,d; XOR ac,d; TEST ac,d; | |

| B2 - b0 = reg | MOV r,d | |

| B3 = w | ||

| COP | JMP disp16 ; JMP disp8 ; Jcond disp8 ; | |

| (disp L) | CALL disp16 ; | |

| (disp H) | b0 = w | MOV ac,m; MOV m,ac(при disp L disp H ) |

| COP | MOV sr,m; MOV sr,r ;MOV m,sr; | |

| md OSR r/m | MOV r,sr; | |

| (disp L) | ||

| (disp H) | ||

| COP | IN addr8; OUT addr8 | |

| Addr8 | ||

| COP | JMP addr ; CALL addr (тип FAR) | |

| Offset L | ||

| Offset H Seg L Seg H |

Способы адресации

Команды ЦП ВМ86 реализуют весьма разнообразные способы адресации, что упрощает организацию и использование сложных структур данных, а также расширяет возможности отдельных команд и повышает гибкость их применения.

Регистровая адресация. Операнд находится в одном из общих регистров МП или в одном из сегментных регистров. Регистр может быть определен в байте кода операции или в постбайте, в котором выделены 3-битовые поля reg и г/m (при md = 11). Команды, оперирующие содержимым регистров, являются наиболее короткими и выполняются за наименьшее время, так как не требуют вычисления ЕА и выполнения цикла шины для обращения к памяти. Для многих команд с регистровой адресацией предусмотрены специальные укороченные форматы.

Непосредственная адресация. Непосредственными операндами являются константы длиной 8 или 16 бит, которые размещаются в последних байтах команды (младший байт следует первым). Доступ к таким операндам в ВМ86 осуществляется очень быстро, поскольку во время выполнения команды они находятся во внутренней очереди команд. Имеются команды, позволяющие манипулировать непосредственными операндами и содержимым общих регистров или ячеек памяти. Однако отсутствуют команды непосредственной загрузки сегментных регистров и включения константы в стек. Поэтому эти операции осуществляются с помощью промежуточной загрузки общего регистра или ячейки памяти.

Прямая адресация является простейшим способом адресации ячейки ЗУ, при котором эффективным адресом ЕА является содержимое байтов смещения disp команды. В командах преобразования данных этот способ реализуется при использовании постбайта с полями md=^00 и r/m= 110. Для пересылок между аккумулятором и памятью предусмотрен укороченный формат.

Разновидностью этого способа является длинная прямая адресация, при которой в формате команды содержатся четыре байта, указывающие базовый адрес сегмента и сегментное смешение offset. В этом случае обеспечивается доступ к ячейке с любым логическим адресом, т. е. к произвольной ячейке во всем пространстве адресов 1 Мбайт, но длинная прямая адресация используется только в командах межсегментных переходов и вызовов подпрограмм. Другая разновидность прямой адресации применяется для указания портов ввода— вывода в двухбайтовых командах IN и OUT, второй байт которых содержит адрес (номер) порта.

Косвенная регистровая адресация. В командах преобразования данных эффективный адрес ЕА равен содержимому одного из "регистров SI, DI, ВХ и ВР при соответствующем кодировании полей md и reg постбайта; md = 00; r/m= 100, 101, 111 и md=01, r/m = 110; disp L = 0. В командах безусловного перехода и вызова подпрограммы с регистровой косвенной адресацией допускается указание любого 16-битового общего регистра (при md=ll; r/m = -000,..., 111).

Данный способ адресации позволяет вычислять адреса во время выполнения программ, что часто требуется, например, для обращения к различным элементам таблиц данных. При модификации содержимого регистра одна и та же команда оперирует различными ячейками памяти, что позволяет организовать вычислительные циклы. Изменение содержимого регистра обычно осуществляется с помощью команд инкрементирования и декрементирования, а также других арифметических команд и команды загрузки эффективного адреса LEA. Разновидностью этого способа является косвенная адресация портов ввода — вывода с помощью содержимого регистра DX в однобайтовых командах IN и OUT.

Базовая адресация. Эффективный адрес операнда ЕА вычисляется путем суммирования содержимого базовых регистров ВХ или ВР и смещения disp (при md = 0l. 10 и г/т = 1 II, 110). При использовании ВХ происходит обращение к операнду в текущем сегменте данных, а при использовании ВР — в текущем сегменте стека. Смещения, содержащиеся в команде, могут иметь длину 8 или 16 бит и интерпретируются как знаковые целые, представленные в дополнительном коде.

Базовая адресация обычно используется для подступа к элементам структур данных, когда смешение (номер) элемента известно на стадии разработки программы (при ее ассемблировании), а базовый (начальный) адрес структуры должен вычисляться при выполнении программы. Модификация содержимого базового регистра позволяет обратиться к одноименному элементу различных структур данных.

Индексная адресация.Значение ЕА вычисляется как сумма смещения disp, находящегося в команде, и содержимого индексного регистра SI или DI (при md=01,10и r/m:=100, 101). Данный способ обычно применяется для обращения к различным элементам одномерного массива (таблицы) данных, когда смещение определяет известный при ассемблировании начальный адрес массива, а индексный регистр, содержимое которого может модифицироваться при выполнении программы, определяет элемент массива. По существу индексная адресация в ВМ86 аналогична базовой.

Базовая индексная адресация.Эффективный адрес ЕА равен сумме содержимого базового регистра ВХ или ВР, индексного регистра SI или Di и смещения disp, находящегося в команде (в частном случае смещение может отсутствовать). Этот способ реализуется при следующем кодировании полей пост-байта: md 11; г/т = 000, 001, 010, 011 иобеспечивает наибольшую гибкость адресации, так как два компонента адреса можно определить и варьировать при выполнении программы. Это удобно при обращении к элементам матриц, т. е. к двумерным массивам, представляемым в памяти как совокупность одномерных массивов.

Относительная адресацияЦП ВМ86 реализуется только по отношению к указателю команд IP, так что сегментное смещение вычисляется как сумма смещения disp, находящегося в команде, и текущего значения IP. При этом значение IP равно адресу байта, следующего за рассматриваемой командой, которая в это время выполняется микропроцессором. В ВМ86 относительная адресация не используется в командах, оперирующих данными, а применяется только в командах условных и безусловных переходов, вызовов подпрограмм и управления циклами. Смещение по отношению к содержимому IP не зависит от размещения программ в адресном пространстве памяти, что обеспечивает позиционную независимость команд. При автоматизированном ассемблировании программы указывается метка команды, которой передается управление, а необходимое смещение вычисляется программой-ассемблером.

Неявная адресация.Объект, содержимым которого манипулирует команда, указывается с помощью первого байта команды вместе с кодом операции без выделения специального поля для этой пели. Чаще всего этот специфический способ адресации встречается в однобайтовых командах, где адресуемым объектом являются аккумулятор, регистр флагов или отдельные флаги. В частности, в командах обработки цепочек неявно используются индексные регистры, причем регистр SI адресует первый элемент цепочки-источника, а регистр DI—первый элемент цепочки-получателя.

Резюме

При обращении к оперативной памяти используются логические и физические адреса ОЗУ .

Логические адреса ОЗУ состоят из СЕГМЕНТА : СМЕЩЕНИЯ ( 4600 : 3000 )

Сегмент (4600н) – указывает на начало области памяти ( по умолчанию 64Кб ), а смещение (3000н)– указывает адрес (смещение от начального адреса сегмента) внутри сегмента. Смещение (ЕА) определяется типом используемой команды

На физическом уровне используется физический адрес, который и передаётся по общей шине – шине адреса. Значение физического адреса определяется из логического адреса путём сложения значения сегмента сдвинутого влево на 1н разряд или 0000в и значения смещения 4600:3000 46000н + 3000н = 49000н

01000110000000000000в + 0011000000000000в= 01001001000000000000в

Адрес выполняемой команды определяется значением регистров CS:IP

Адрес вершины СТЕКА определяется значением регистров SS:SP

Тема 3.5 Организация и принципы работы памяти.

Память является одним из основных элементов любой вычислительной системы. Элементы памяти в том или ином виде присутствуют в каждом конструктивном модуле PC

Для работы ЭВМ необходимо иметь внешнюю и внутреннюю память.

Внешняя память предназначена для длительного хранения данных, которые сохраняются и после выключения ЭВМ.

Внутренняя память для хранения данных на момент работы ЭВМ

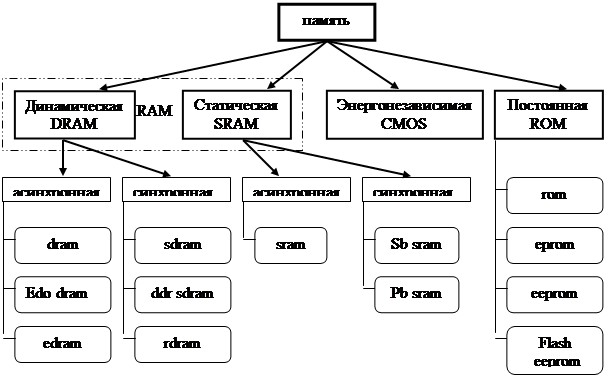

Рассмотрим организацию внутренней памяти рис. 3-5-1.

Недостаток оперативной памяти состоит в том, что она временная, то есть при отключении питания оперативная память полностью очищается, и данные, не записанные на внешний носитель, будут потеряны.

Основная задача RAM – предоставлять по требованию CPU необходимую информацию Это означает, что данные в любой момент должны быть доступны для обработки.

Рис. 3-5-1

Запоминающим элементом динамической памяти ( DRAM ) является конденсатор, который может находиться в заряженном – «1» или разряженном – «0» состоянии. В идеальном конденсаторе заряд может храниться неограниченное время. В реальном конденсаторе существует ток утечки, поэтому информация, записанная в динамическую память, со временем будет утрачена, так как конденсаторы запоминающих элементов полностью разрядятся.

Чтобы пояснить этот процесс, представим элемент памяти как ведро с водой, которое может быть либо пустым (состояние 0, соответственно Out), либо полным (состояние 1, соответственно In). Однако в этом ведре имеются такие маленькие дырки, что вода (информация) вытекала бы по капле, если бы "водоносу" (специальной логической схеме) не было поручено компенсировать убыток воды (данных) так, чтобы уровень ее оставался неизменным. Этот процесс называется регенерацией памяти (Refresh). Деятельность "водоноса" имеет огромное значение, поэтому ему нельзя мешать. Это означает, что CPU имеет доступ к данным, находящимся в RAM, только в течение циклов, свободных от регенерации.

Единственным способом регенерации хранимой в памяти информации является выполнение операции чтения/записи данных. Если информация заносится в динамическую память, а затем в течение нескольких миллисекунд остается невостребованной, она будет утрачена, так как конденсаторы запоминающих элементов полностью разрядятся.

Регенерация памяти происходит при выполнении каждой операции чтения или записи. Однако нет гарантии, что при выполнении любой программы произойдет обращение ко всем ячейкам памяти, поэтому имеется специальная схема, которая через определенные промежутки времени (например, каждые 2 мс) будет осуществлять доступ (для считывания) ко всем строкам памяти. В эти моменты CPU находится в состоянии ожидания. За один цикл схема регенерирует все строки динамической памяти.

Принцип работы

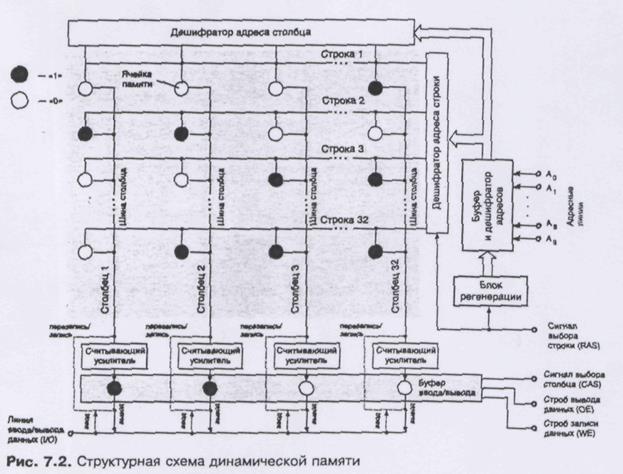

Ячейки памяти организованы в матрицу, состоящую из строк и столбцов. Полный адрес ячейки данных включает два компонента — адрес строки (row Адрес, бит) и адрес столбца (column Адрес, бит). На рис. 7.2 представлена матрица, состоящая из 32 строк и 32 столбцов, то есть из 1024 ячеек.

Когда CPU (или устройство, использующее канал DMA) обращается к памяти для чтения информации, на входы микросхемы поступает строб вывода данных OE (Output Enabled), затем подается адрес строки и одновременно с ним (или с задержкой) сигнал RAS (Row Адрес, бит Strobe). Это означает, что каждая шина столбца соединяется с ячейкой памяти выбранной строки. Адрес ячейки поступает по адресным линиям (в нашем случае их десять) на дешифратор, который преобразует поступивший набор нулей и единиц в номер строки. Емкость конденсатора очень мала (доли пикофарады) и его заряд тоже мал, поэтому используется усилитель, подключенный к каждой шине столбца динамической памяти. Информация считывается со всей строки запоминающих элементов одновременно и помешается в буфер ввода/вывода. С незначительной задержкой после сигнала RAS на входы динамической памяти подается адрес столбца и сигнал CAS (Column Адрес, бит Strobe). При чтении данные выбираются из буфера ввода/вывода и поступают на выход динамической памяти в соответствии с адресом столбца. При считывании информации из ячеек памяти происходит ее разрушение, поэтому производится перезапись считанной информации: выходы регистра строки снова соединяются с общими шинами столбцов памяти, чтобы перезаписать считанную информацию из строки. Если ячейка имела заряд, то она снова будет заряжена еще до завершения цикла чтения. На ячейки, которые не имели заряда, напряжение не подается.

Если выполняется запись в память, то подается строб записи WE (Write Enable) и информация поступает на соответствующую шину столбца не из буфера, а с входа памяти в соответствии с адресом столбца. Таким образом, прохождение данных при записи задается комбинацией сигналов, определяющих адрес столбца и строки, а также сигналом разрешения записи данных в память.

Основные характеристики микросхем памяти

Основными характеристиками элементов (микросхем) памяти являются:

§ Тип

§ Емкость

§ Разрядность

§ Быстродействие

§ Временная диаграмма

Емкость и разрядность

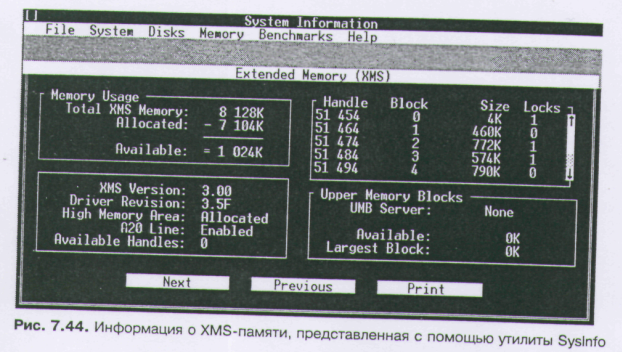

На рис. 7.2 представлена структура микросхемы памяти, имеющая одну линию ввода/вывода. Из такой микросхемы CPU может одновременно считать информацию о XMS-памяти можно получить с помощью утилиты Syslnfo входящей в пакет Norton Utilities (рис. 7.44).

Чтобы иметь доступ к этой памяти, необходим специальный драйвер, с помощью которого данные пересылаются из стандартной памяти в расширенную и обратно. Выполнение программ, размещенных в расширенной памяти, не предусмотрено. Драйвер, реализующий XMS. переводит CPU в защищенный режим, т. е. режим, в котором можно адресовать всю память.

Этот драйвер мы уже упомянули в предыдущем разделе. Он, как и EMM386.EXE, поставляется вместе с DOS и Windows и называется HIMEM.SYS. Определяется в файле CONFIG.SYS в командной строке типа:

Device = C: \ DOS \ HIMEM.SYS:

Дальнейшие сведения, касающиеся распределения оперативной памяти с помощью файлов CONFIG.SYS и AUTOEXEC.BAT

Виртуальная память

Объем оперативной памяти системы определяется объемом модулей памяти, установленных на материнской плате. Программы в процессе их работы и данные располагаются в ячейках этой памяти, откуда могут быть востребованы процессором по мере необходимости.

Для увеличения объема памяти системы была разработана концепция виртуальной памяти. Суть этой концепции заключается в том, что на жестком диске создается файл размером несколько десятков мегабайт (Swap-файл — Файл обмена), являющийся как бы расширением оперативной памяти. Когда все ячейки реальной оперативной памяти заняты, а для работы программ необходима память, менеджер виртуальной памяти освобождает физическую память, перенося часть информации, которая давно не использовалась, в файл обмена.

Предположим, что операционной системе необходимо 80 Мбайт памяти, чтобы загрузить все запушенные программы, но на PC установлено только 32 Мбайт RAM. В этом случае запускается менеджер виртуальной памяти, который создает на жестком диске файл обмена размером 80 — 32 = 48 Мбайт. Процессор будет обращаться к 80 Мбайт памяти, "не подозревая", что не все из этих ячеек памяти располагаются в модулях памяти, что часть их находится на жестком диске.

Концепция виртуальной памяти широко применяется в многозадачных операционных системах (Windows 95/98, Windows NT и др.). Без виртуальной памяти мы не смогли бы, например, готовя итоговый отчет, одновременно работать с большой таблицей Excel, набирать текст в текстовом редакторе, работать с базой данных и получать сообщения по E-mail. Для этого необходима оперативная память очень большого объема, которой, как правило, всегда не хватает.

Не следует забывать, что жесткий диск работает в тысячи раз медленнее, чем оперативная память, поэтому попытка загрузить одновременно большое количество программ приведет к непрерывному обращению к жесткому диску и, в конечном счете, к зависанию системы.

Дата добавления: 2017-06-13; просмотров: 3267;