Контроллер динамической памяти

(КДП) обеспечивает мультиплексирование адреса системной шины, выработку управляющих сигналов CAS и RAS[3:0] (для селекции модулей ОЗУ), а также внутреннюю (по таймеру) или внешнюю (прозрачную) регенерацию.

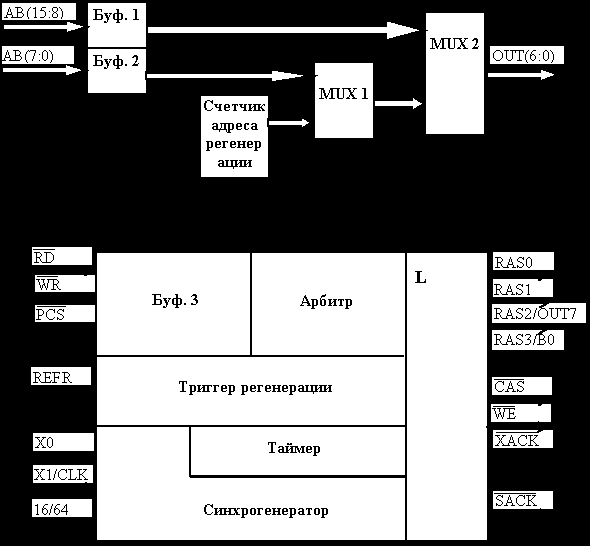

Структурная схема контроллера (Рис. 7.) включает в себя :

- буферные схемы Буф.1,2,3 для подключения системной шины адреса и управления;

- счетчик адреса регенерации;

- мультиплексоры MUX1,2;

- схему управления с тактовым генератором, таймером и триггером регенерации, арбитром и логической схемой L для формирования управляющих сигналов.

КДП обеспечивает преобразование сигналов системной шины МПС в сигналы управления динамическим ОЗУ (см. Рис. 7.16), причем может работать в двух режимах : "16/64" (на память 16K или 64K соответственно). В режиме "16" две старшие линии адреса используются для формирования одного из сигналов RAS\[0..3], в режиме "64" КДП может управлять двумя банками по 64K, причем сигнал RAS появляется на одном из выходов RAS0 или RAS1 - в зависимости от состояния линии RAS3\/B0, которая в режиме "64" становится входом, определяющим номер банка ОЗУ.

Регенерация может осуществляться в двух режимах - внутреннем и внешнем. Если вход REFR остается неактивным 10..16 мкС, то формируется запрос на цикл регенерации от внутреннего таймера, причем в случае конфликта арбитр отдает предпочтение циклу памяти. Таким образом, и при регенерации по таймеру используются свободные такты шины. При внешней регенерации запрос должен быть сформирован на входе REFR.

Сигнал PCS - "Защищенный выбор кристалла" отличается от традиционного CS тем, что если PCS сформирован, то цикл ЗУ аннулировать нельзя.

RD, WR - запросы на циклы чтения и записи соответственно.

X0, X1 - выводы для подключения кварцевого резонатора при работе с внутренним генератором. При работе с внешним генератором на вход X0 подается высокий потенциал, а на X1 - частота CLK внешнего генератора.

Выходной сигнал SACK\ вырабатывается КДП в начале цикла обращения к памяти. Если запрос от МП приходится на цикл регенерации, то SACK\ задерживается до начала цикла чтения/записи.

Выходной сигнал XACK\ ("Готовность данных") вырабатывается в конце цикла чтения/записи.

Сигналы SACK\ и XACK\ можно использовать для управления потенциалом на входе READY микропроцессора.

Рис. 7.16. Контроллер динамического ОЗУ

Регенерация "размещение данных"

В некоторых, достаточно редких частных случаях, можно воспользоваться способом регенерации "размещением данных". Так, если, например, память изображения дисплея является составной частью единого ОЗУ МПС и МП регулярно обращается в эту область для поддержания изображения на экране, то достаточно расположить область ОЗУ дисплея в памяти МПС таким образом, чтобы она "перекрывала" все строки накопителя (достигается соответствующим подбором адресов), чтобы каждое обращение к области ОЗУ дисплея, помимо регенерации изображения, регенерировала и всю память МПС.

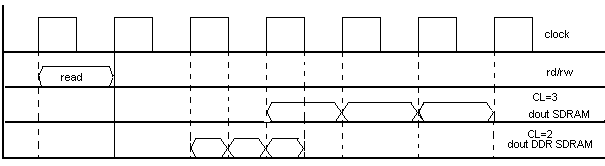

SDRAM и DDR SDRAM

Самой распространенной памятью на сегодняшний день для IBM PC являются два вида памяти

SDRAM synchronic dynamic random access memory

DDR SDRAM double data rate synchronic dynamic random access memory

Рис. 7.17. Временные диаграммы работы SDRAM и DDR SDRAM

CL(CAS latency) – количество тактов до первого DOUT

Дата добавления: 2017-03-12; просмотров: 2953;