Серия быстродействующих БИС ортогональной регистровой памяти

Интенсивное развитие многопроцессорных вычислительных систем (МВС) выдвигает новые требования к элементной базе электронно-вычислительной аппаратуры. При разработке МВС с перестраиваемой структурой возникает необходимость создания быстродействующих устройств для преобразования кодов цифровой информации из последовательного в параллельный и наоборот с одновременным перераспределением этой информации между рядами передатчиков и приемников.

Такими устройствами могут служить последовательно-параллельные регистры сдвига, выполненные в виде ортогональных матриц статической регистровой памяти. Известные матричные статические регистры имеют малую информационную емкость (не более 4x4 бит).

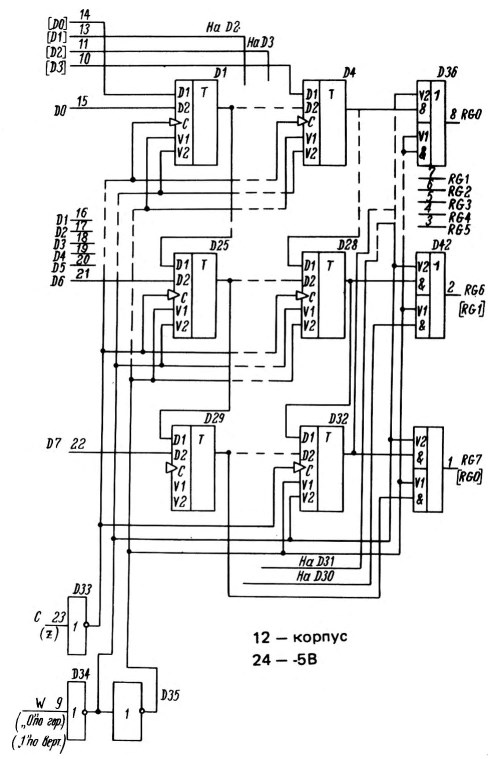

Для реализации указанного класса устройств разрабатывается серия микросхем ортогональной регистровой памяти (ОРП) с различной организацией матричного регистра сдвига. Создана микросхема ОРП-1 (рис. 1) с матричным регистром сдвига информационной емкостью 4x8 бит, выполненная на ТТАШ схемах, разрабатывается микросхема ОРП-2 емкостью 8х8 бит.

Рис. 1. Функциональная электрическая схема БИС ОРП-1

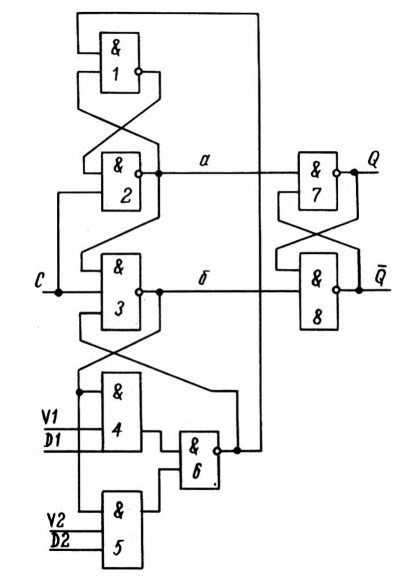

В качестве элементов матричного регистра сдвига Д1—Д32 использованы триггеры DV-типа, функциональная схема которых приведена на рис. 2. Входные шины (ДО)—(ДЗ) служат для ввода информации в столбцы, ДО—Д7 — в строки матричного регистра. Шина «С» является входом синхронизации. Шина «W» обеспечивает управление сдвигом информации в матричном регистре: при подаче сигнала «лог. 0» осуществляется сдвиг матричного регистра по строкам, при подаче «лог. 1» - по столбцам. При сдвиге по строкам на выходные шины RG0—RG7 поступает информация из последнего столбца матричного регистра, а при сдвиге по столбцам — из последней строки.

Рис. 2. Функциональная электрическая схема элемента матричного регистра сдвига

Микросхема ОРП-1 имеет регулярную матричную структуру, на кристалле размером 3,7x3,9 мм2 содержится около 1500 элементов.

Основные электрические характеристики микросхемы ОРП-1:

- Время распространения сигнала при управлении по входу С, н.. – 60

- Время опережения сигналов, подаваемых на входы D и W относительно входа С, нс… - 25

- Время удержания сигнала, подаваемого на вход D относительно входа С, нс ... – 20

- Максимальная тактовая частота, МГц… - 15

- Рассеиваемая мощность, мВт… - 500

Остальные электрические характеристики, за исключением пониженной нагрузочной способности, аналогичны параметрам микросхем серии 530.

В микросхеме ОРП-2 используются ионолегированные резисторы. При организации матричного регистра 8x8 бит размер кристалла микросхемы составляет 4x4,5 мм2, а рассеиваемая мощность — 800 мВт.

Дальнейшее развитие этой серии направлено на увеличение информационной емкости и быстродействия матричного регистра сдвига. При использовании в матрице ОРП микромощных вентилей с пониженным логическим перепадом может быть достигнута информационная емкость регистра сдвига 8x32 или 16х16 бит.

Применение микросхем ОРП в многопроцессорных вычислительных системах с программируемой структурой позволит сократить в 4—5 раз количество микросхем в процессорной части системы. Указанные преимущества обеспечивают эффективное использование описанных микросхем в системах цифрового анализа сигналов, быстродействующих интерфейсах и других устройствах электронно-вычислительной аппаратуры.

Литература:

1. Каляев А. В. Многопроцессорные вычислительные системы с программируемой архитектурой.— Электронная промышленность, 1983, вып. 1, с. 9—12.

2. The bipolar digital integrated circuits: Data Book.— Dales, Texas: Texas Instruments, 1981, p. 564 —565.

Дата добавления: 2023-11-20; просмотров: 1951;