Аппаратные элементы компьютерной логики

Логический элемент компьютера — это часть электронной логичеcкой схемы, которая реализует элементарную логическую функцию.

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и другие (называемые также вентилями), а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния — “1” и “0” в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению “истина” (“1”), а низкий — значению “ложь” (“0”).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

Таблица истинности это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний.

Логические (функциональные) схемы

1) Схема И.

Схема И реализует конъюнкцию двух или более логических значений.

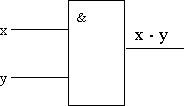

Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис. 1. Таблица истинности — в таблице 1.

Рис. 1

| Таблица 1

|

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением: z = xЧy (читается как "x и y").

Операция конъюнкции на функциональных схемах обозначается знаком “&” (читается как "амперсэнд"), являющимся сокращенной записью английского слова and.

2. Схема ИЛИ

Схема ИЛИ реализует дизъюнкцию двух или более логических значений.

Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

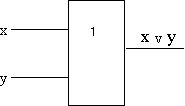

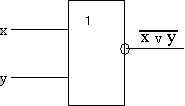

Условное обозначение схемы ИЛИ представлено на рис. 2. Знак “1” на схеме — от устаревшего обозначения дизъюнкции как ">=1" (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y (читается как "x или y"). Таблица истинности — в табл. 2.

Рис. 2

| Таблица 2

|

3. Схема НЕ

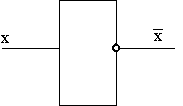

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом x этой схемы и выходом z можно записать соотношением z = x, где x читается как "не x" или "инверсия х".

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение инвертора — на рисунке 3, а таблица истинности — в табл. 3.

Рис. 3

| Таблица 3

|

4. Схема И-НЕ

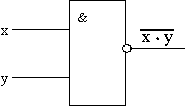

Схема И-НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И.

Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  читается как "инверсия x и y".

читается как "инверсия x и y".

Условное обозначение схемы И-НЕ представлено на рисунке 4. Таблица истинности схемы И-НЕ — в табл. 4.

Рис. 4

| Таблица 4

|

5. Схема ИЛИ-НЕ

Схема ИЛИ-НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ.

Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  , читается как "инверсия x или y". Условное обозначение схемы ИЛИ-НЕ представлено на рис. 5.

, читается как "инверсия x или y". Условное обозначение схемы ИЛИ-НЕ представлено на рис. 5.

Таблица истинности схемы ИЛИ-НЕ — в табл. 5.

Рис. 5.

| Таблица 5.

|

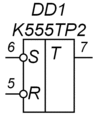

14.Асинхронный и синхронный триггер [2].

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время. Однако, этот маленький промежуток времени при определенных условиях может создавать ошибки. Именно для этого и существуют синхронные триггеры, которые позволяют запоминать состояние только в определенные промежутки времени

15.Асинхронный D-триггер [2].

Асинхронная установка D-триггера в единичное или нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на входы /S и /R. В это время входы D и С не влияют. В остальном аналогичен синхронному. Является тиггером задержки

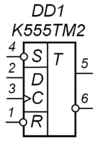

16.Синхронный D-триггер [2].

D-триггер (D от англ.delay — задержка[13][14][15] либо от data[16] - данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Является тиггером задержки

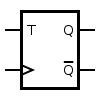

17.Асинхронный T-триггер [2].

Асинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по каждому тактовому импульсу на входе С.

Т-триггер (от англ. Toggle - переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2.

18.Синхронный T-триггер [2].

Синхронный Т-триггер[17], при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе. Т-триггер (от англ. Toggle - переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2.

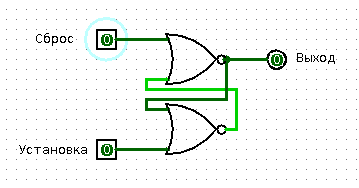

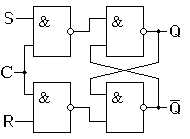

19.Асинхронный RS-триггер [2].

RS-триггер, или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

20.Синхронный RS-триггер [2].

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется опасные гонки), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены.

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

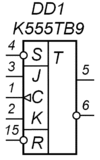

21.JK-триггер [2].

JK-триггер отличается от RS-триггера прежде всего тем что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров.

JK-триггеры подразделяются на универсальные и комбинированные. Универсальный JK-триггер имеет два информационных входа J и K. По входу J триггер устанавливается в состояние Q=1, /Q=0, а по входу K-в состояние Q=0, /Q=1.

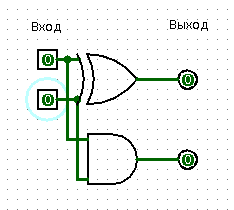

22.Полусумматор и сумматор с переносом [2].

Сумматоры нужны для сложения чисел.

Полусумматор — логическая схема, имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Полусумматор используется для построения двоичных сумматоров. Полусумматор позволяет вычислять сумму A+B, где A и B — это разряды двоичного числа, при этом результатом будут два бита S и C, где S — это бит суммы по модулю 2, а C — бит переноса.

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

23.Шифратор [2].

шифратором, или кодером называется комбинационное логическое устройство для преобразования чисел из десятичной системы счисления в двоичную. Входам шифратора присваиваются значения десятичных чисел, поэтому подача активного логического сигнала на один из входов воспринимается как подача соответствующего десятичного сигнала. Если шифратор имеет n входов, то на выходе не более чем 2^n. Если выходов максимум, относительно входа, то он полный

Дешифратор

| дешифратор – это устройство, преобразующее цифровой сигнал, в какой либо кодировке в другую, не закодированную форму. |

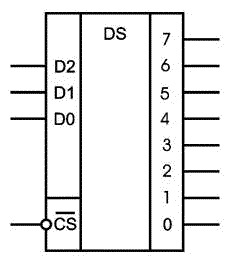

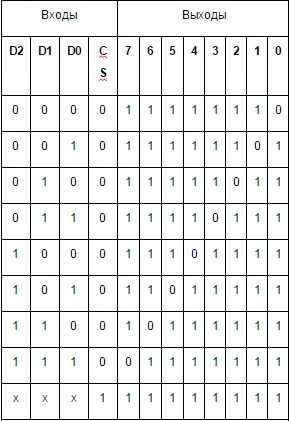

Главное назначение дешифратора – выбор одного из устройств, номер которого приходит на вход дешифратора. В качестве таких выбираемых устройств часто выступают различные цифровые микросхемы, имеющие вход выбора кристалла (  CS). При этом сигналы с выходов дешифратора поступают на входы

CS). При этом сигналы с выходов дешифратора поступают на входы  CS выбираемых микросхем. Именно по этому активным сигналом на выходе дешифратора является сигнал логического нуля. Для лучшего понимания логики работы дешифратора изучите его таблицу истинности на рисунке 25. В этой таблице появилось новое обозначение. Знак «X» в таблице истинности означает, что на этом входе может присутствовать любое значение (0 или 1). При этом сигнал ни на одном из выходов не изменится.

CS выбираемых микросхем. Именно по этому активным сигналом на выходе дешифратора является сигнал логического нуля. Для лучшего понимания логики работы дешифратора изучите его таблицу истинности на рисунке 25. В этой таблице появилось новое обозначение. Знак «X» в таблице истинности означает, что на этом входе может присутствовать любое значение (0 или 1). При этом сигнал ни на одном из выходов не изменится.

Регистр памяти

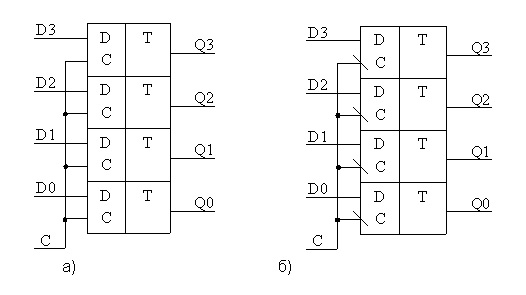

Регистры памяти предназначены для временного хранения многоразрядных двоичных кодов. Такие регистры обычно представляют собой параллельную группу синхронных D триггеров необходимой разрядности. Так, например, четырехразрядный регистр памяти со статическим управлением выполняют по схеме (рис.1.8а). Такой регистр повторяет входное слово, если тактовый сигнал С = 1, и запоминает, фиксирует это слово, если С = 0. Поэтому регистр со статическим управлением иногда называют «прозрачным фиксатором». Схема регистра с динамическим управлением, или как его иногда называют «регистра D-типа", представлена на рис.1.8б.

Дата добавления: 2017-01-16; просмотров: 2109;