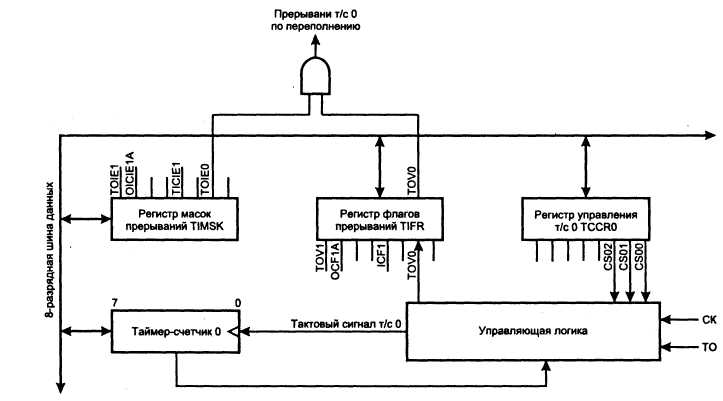

РАЗРЯДНЫЙ ТАЙМЕР/СЧЕТЧИК 0

8-разрядный таймер/счетчик может получать импульсы тактовой частоты - CK, импульсы с предварительного делителя (CK/8, CK/64, CK/256 или CK/1024), импульсы с внешнего вывода или быть остановлен соответствующими установками регистра TCCR0. Флаг переполнения таймера находится в регистре TIFR. Биты управления таймером расположены в регистре TCCR0. Разрешение и запрещение прерываний от таймера управляется регистром TIMSK.

При работе таймера/счетчика от внешнего сигнала, внешний сигнал синхронизируется с тактовым генератором ЦПУ. Для правильной обработки внешнего сигнала, минимальное время между соседними импульсами должно превышать период тактовой частоты процессора. Сигнал внешнего источника обрабатывается по спадающему фронту тактовой частоты процессора.

8-разрядный таймер/счетчик можно использовать как счетчик с высоким разрешением, так и для точных применений с низким коэффициентом деления тактовой частоты. Более высокие коэффициенты деления можно использовать для медленных функций или измерения временных интервалов между редкими событиями.

Рис.16.2. Структурная схема таймера/счетчика 0.

РЕГИСТР УПРАВЛЕНИЯ ТАЙМЕРОМ/СЧЕТЧИКОМ 0 - TCCR0

Бит 7 6 5 4 3 2 1 0

┌───┬───┬───┬───┬───┬────┬────┬────┐

$33($53)│ - │ - │ - │ - │ - │CS02│CS01│CS00│ TCCR0

└───┴───┴───┴───┴───┴────┴────┴────┘

Чт./зап.(R/W) R R R R R R/W R/W R/W

Начальн.знач. 0 0 0 0 0 0 0 0

Биты 7..3 - зарезервированы. В AT90S2313 эты биты зарезервированы и всегда читаются как 0.

Биты 2,1,0 - CS02, CS01, CS00 - выбор тактовой частоты. Эти биты задают коэффициент деления предварительного делителя.

| CS02 | CS01 | CS00 | Описание |

| Таймер/счетчик остановлен | |||

| CK | |||

| CK/8 | |||

| CK/64 | |||

| CK/256 | |||

| CK/1024 | |||

| Внешний вывод T0, нарастающий фронт | |||

| Внешний вывод T0, спадающий фронт |

Таблица 16.1. Выбор коэффициента предварительного деления

Условие Stop запрещает/разрешает функционирование таймера/счетчика. В режимах деления используется частота тактового генератора. При использовании работы от внешнего источника предварительно должен быть установлен соответствующий бит регистра направления данных (0 - включает ножку на ввод).

Дата добавления: 2016-12-27; просмотров: 1790;