ПРОГРАММИРУЕМЫЕ АНАЛОГОВЫЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ (ПАИС)

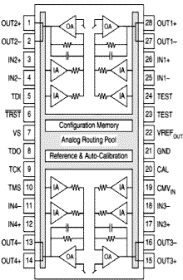

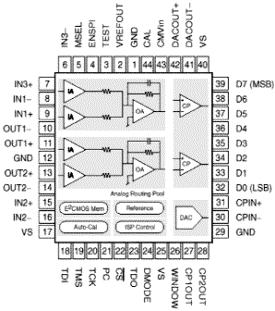

Современная аппаратура обработки сигналов немыслима без аналоговой предварительной обработки, преобразования данных с датчиков и формирования управляющих напряжений и токов для исполнительных элементов. Появился довольно новый класс устройств - программируемые аналоговые интегральные схемы (ПАИС, в зарубежной терминологии FPAA, Field Programmable Analog Array). Количество фирм - производителей ПАИС достаточно велико. Один из авторитетных производителей матричных структур Lattice предлагает ПАИС семейства ispPAC (In-System Programmable Analog Circuit). В его состав входят микросхемы ispPAC10 (рис. 9.1) и ispPAC20 (рис. 9.2).

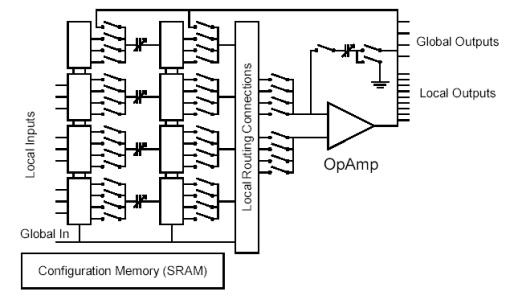

Рис. 9.1. Структура ispPAC10 Рис. 9.2. Структура ispPAC20

Заложенная в эту серию архитектура основывается на следующих базовых функциональных ячейках: инструментальный усилитель (IA), выходной усилитель (OA), реализованных по схеме сумматора/интегратора, 2,5-вольтовый источник опорного напряжения (Reference, ИОН), 8-разрядный ЦАП с выходом по напряжению, и сдвоенный компаратор (CP). Аналоговые входы и выходы ячеек (кроме ИОН) для повышения динамического диапазона обрабатываемых сигналов выполнены по дифференциальной схеме. Два IA и один OA образуют макроячейку, называемую PAC-блоком, в которой выходы IA соединены с суммирующими входами OA. ispPAC10 имеет четыре такие макроячейки, а ispPAC20 — две. В состав ispPAC20 также входят ячейки ЦАП и компараторов. В макроячейке программируются коэффициент усиления IA в диапазоне от -10 до +10 с шагом 1, величина емкости конденсатора обратной связи в OA (128 возможных значений) и включение/выключение сопротивления обратной связи в OA.

Средства внутренней трассировки (Analog Routing Pool) позволяют выполнить соединения между входными контактами микросхемы, входами и выходами макроячеек, выходом ЦАП и входами компараторов. Объединение нескольких макроячеек позволяет строить схемы перестраиваемых активных фильтров, основанные на использовании звена интегратора, на диапазон частот от 10 до 100 кГц.

Для повышения точности по постоянному току предусмотрен режим автокалибровки, который выполняется всегда при включении питания, а также при подаче фронта импульса на специальный цифровой вход CAL микросхемы. В процессе автокалибровки минимизируется напряжение смещения выхода макроячейки с запрограммированными конкретными коэффициентами усиления в ней.

8-разрядный ЦАП допускает параллельную или последовательную загрузку. Формируемое им после подачи питания выходное напряжение задается при программировании микросхемы. Для компараторов допускается программирование включения/выключения гистерезиса их характеристики.

Микросхемы работают с одним напряжением питания +5 В, поэтому рабочая точка в микросхеме сдвигается на 2,5 В, вырабатываемые ячейкой ИОН. Есть также возможность перепрограммирования смещения внутренней рабочей точки конкретного PAC-блока на величину напряжения, поданного на специальный аналоговый вход CMVIN.

Главной тенденцией развития и совершенствования аналоговых микросхем состоит в неуклонном улучшении параметров, определяющих погрешности обработки сигналов. Lаttice объявляет о пригодности ПАИС семейства ispPAC для 12-разрядных систем сбора и обработки данных. Рассмотрим основные параметры этих ПАИС. Типовое значение приведенного ко входу температурного дрейфа дифференциального выходного напряжения смещения макроячейки согласно спецификации равно 50 мкВ/°C (второй вход макроячейки не используется). Диапазон изменения выходного напряжения на отдельном выходе микросхемы составляет 1…4 В при нагрузке 300 Ом между дифференциальными выходами, то есть размах напряжения между ними равен 6 В. В случае использования АЦП с дифференциальным входом и общим с ispPAC питанием +5 В возможно достижение полного использования диапазона входных сигналов АЦП до 5 В. Это даст значение единицы младшего разряда (ЕМР) в 1,25 мВ. Отсюда видно, что существуют значительные ограничения сверху на коэффициент усиления в макроячейке с учетом диапазона рабочих температур. Эксплуатационный диапазон температур микросхем равен –40… +85°C.

Основные параметры схем ispPAC:

- Типовой входной ток макроячейки — 3 пА.

- Выходное напряжение ИОН имеет разброс не более ±2% и типовой дрейф 50 ppm/°C. (ppm - это сокращение от parts per million, на сколько миллионных долей меняется ёмкость при изменении температуры на 1°С).

- Погрешность установки частоты полюса в схеме активного фильтра не более 5 %.

- Время установления ЦАП (до 0.1 %) не более 6 мкс

- Типовое время переключения компаратора при напряжении скачка 10 мВ — 750 нс.

- Число циклов стирания/перепрограммирования — не менее 10 000.

- Максимальный ток потребления — 23 мА для ispPAC10 и 21 мА для ispPAC20.

Конфигурирование микросхемы осуществляется через JTAG-интерфейс с помощью загрузочного кабеля от параллельного порта PC или имеющегося в системе микроконтроллера.

Проектирование устройств серии ispPAC поддерживается САПРом PAC-Designer. Этот пакет обеспечивает в графическом виде редактирование схемы путем проведения конкретных внутренних соединений и задания величин программируемых параметров, ее моделирование, создание конфигурационного файла и его загрузка.

Разводку и задание значений параметров выполняют вручную. Но в системе также имеется библиотека некоторых готовых решений, в том числе и для построения активных фильтров. Процесс проектирования несложен, и результаты получаются достаточно быстро.

Lattice не является единственным производителем ПАИС. Так, компания Fast Analog Solution (www.fas.co.uk), которая входит в группу ZETEX, предлагает такие микросхемы в серии TRAC. Фирма обозначает их как Field Programmable Analog Devices (FPAD)

Архитектура этих ПАИС приведена на рис. 9.3

Рис.9.3. Архитектура ПАИС TRAC020

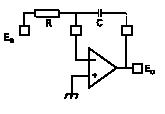

Каждая ячейка содержит операционный усилитель и конфигурируемые цепи обратной связи, что позволяет реализовывать базовые блоки аналоговой обработки сигналов. Так, на рис 4.4. представлен интегратор

Рис.9.4. Схема интегратора

Следует отметить, что цепи обратной связи могут содержать как линейные, так и нелинейные элементы (рис.9.5), что позволяет строить и функциональные преобразователи.

Рис.9.5 Схема интегратора с нелинейным элементом

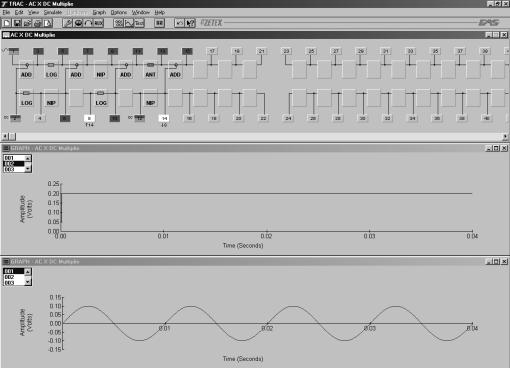

Поставляемое программное обеспечение обладает достаточно широкими возможностями по вводу параметров и моделированию устройств. На рис.9.6 представлено окно программы с загруженным проектом перемножителя "логарифм - антилогарифм" и результатами его моделирования во временной области.

Рис.9.6 Окно программы с проектом перемножителя

"логарифм - антилогарифм" и результатами его моделирования

во временной области

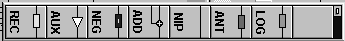

Тип каждой ячейки можно задать с помощью панели инструментов, приведенной на рис.9.7

Рис.9.7 Панель инструментов ячеек

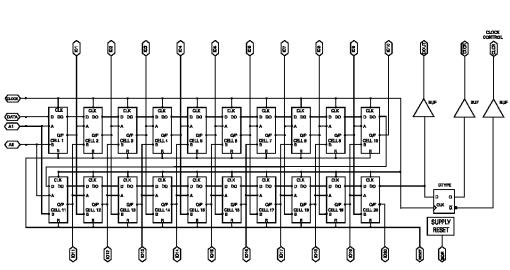

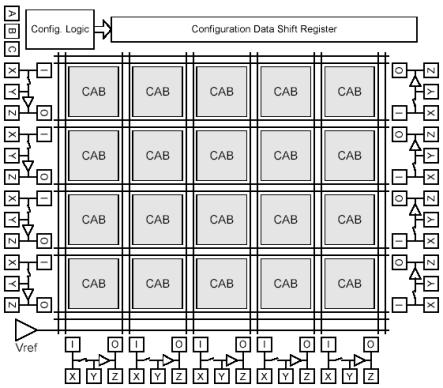

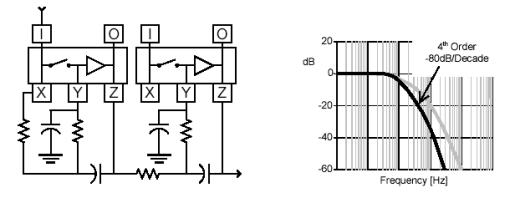

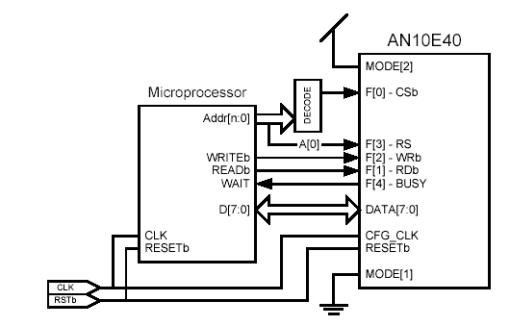

Отличительная особенность ПАИС компании Anadigm AN10E40 состоит в том, что они представляют собой матричную структуру (4 x 5 ячеек), причем каждая из ячеек выполнена на ОУ с переключаемыми конденсаторами (switched capacitor). Архитектура ПАИС AN10E40 компании Anadigm представлена на рис.9.8.

Рис.9.8. Архитектура ПАИС AN10E40 компании Anadigm

Структура каждой ячейки представлена на рис.9.9.

Рис.9.9. Структура ячейки ПАИС AN10E40

Из рис.9.9. видно, что основное применения ПАИС AN10E40 компании Anadigm - реализация фильтров и линейных устройств обработки сигналов. Пример реализации фильтра 4 порядка представлен на рис.9.10

Рис.9.10. Реализация фильтра 4 порядка

Каждая ячейка позволяет реализовать звено второго порядка. Конфигурация ПАИС может осуществляется с помощью микроконтроллера, встроенного в систему (рис.9.11)

Рис.9.11. Реализация звена второго порядка.

В данном случае ПАИС занимает определенную область в адресном пространстве контроллера, а конфигурационные данные хранятся в его памяти или постоянной памяти системы.

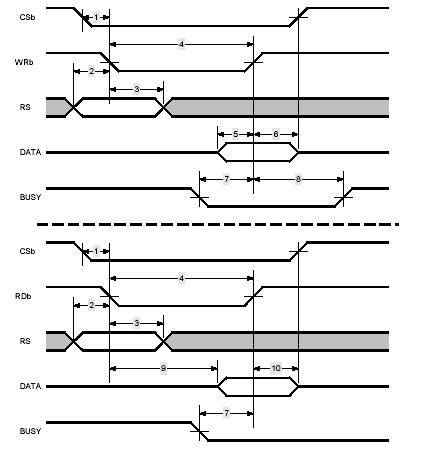

Временные диаграммы конфигурации ПАИС приведены на рис.9.12

Рис.4.12. Временные диаграммы конфигурации ПАИС

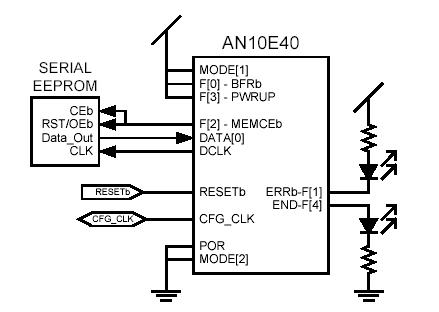

Конфигурация ПАИС возможна также и с применением последовательного ПЗУ (рис.9.13).

Рис.9.13. Конфигурация ПАИС с применением последовательного ПЗУ

Для отладки проектов, выполненных на ПАИС, фирма Anadigm выпускает специализированную отладочную плату (рис.9.14), позволяющую провести отработку проекта.

Рис.9.14. Отладочная плата ПАИС фирмы Anadigm

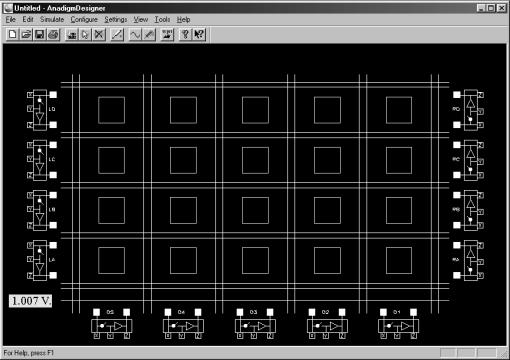

Программное обеспечение AnadigmDesigner имеет удобные средства ввода проекта, моделирования и загрузки конфигурации. На рис.9.15 представлено главное окно программы AnadigmDesigner

Рис.9.15. Главное окно программы AnadigmDesigner

Отладочные платы позволяют провести отработку решений в реальной системе. Они содержит достаточное количество буферных элементов и каналов ввода-вывода для подачи необходимых тестовых сигналов. В настоящее время имеется разнообразные программируемые аналоговые структуры, которые в значительной мере облегчают процесс разработки.

10. ПРОГРАММИРУЕМЫЕ РЕЛЕ

Использование программируемого реле можно рассмотреть напримере реализации программы управления установкой автоматизированной сушки подшипниковых колец после её разработки при помощи графа переходов. Первичная очистка колец подшипника осуществляется путем естественной промывки технологической жидкостью на шлифовальном станке. Автоматизированная установка сушки колец необходима для их подготовки к консервации. При этом дополнительно осуществляется вторичная очистка деталей подшипников от абразивных и металлических частиц.

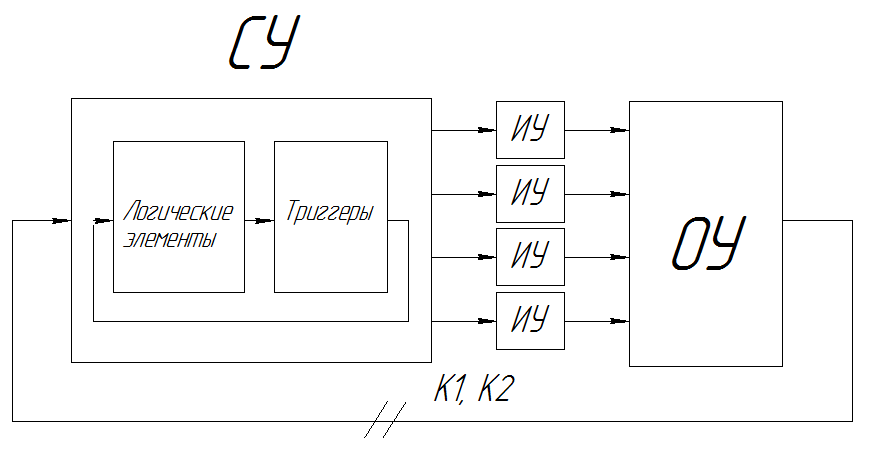

Рис.10.1. Структурная схема

Установка управляется от контроллера и состоит из следующих устройств:

- узла подачи колец в зону сушки;

- узла вращения подшипниковых колец;

- узла подачи воздуха на рабочую поверхность колец.

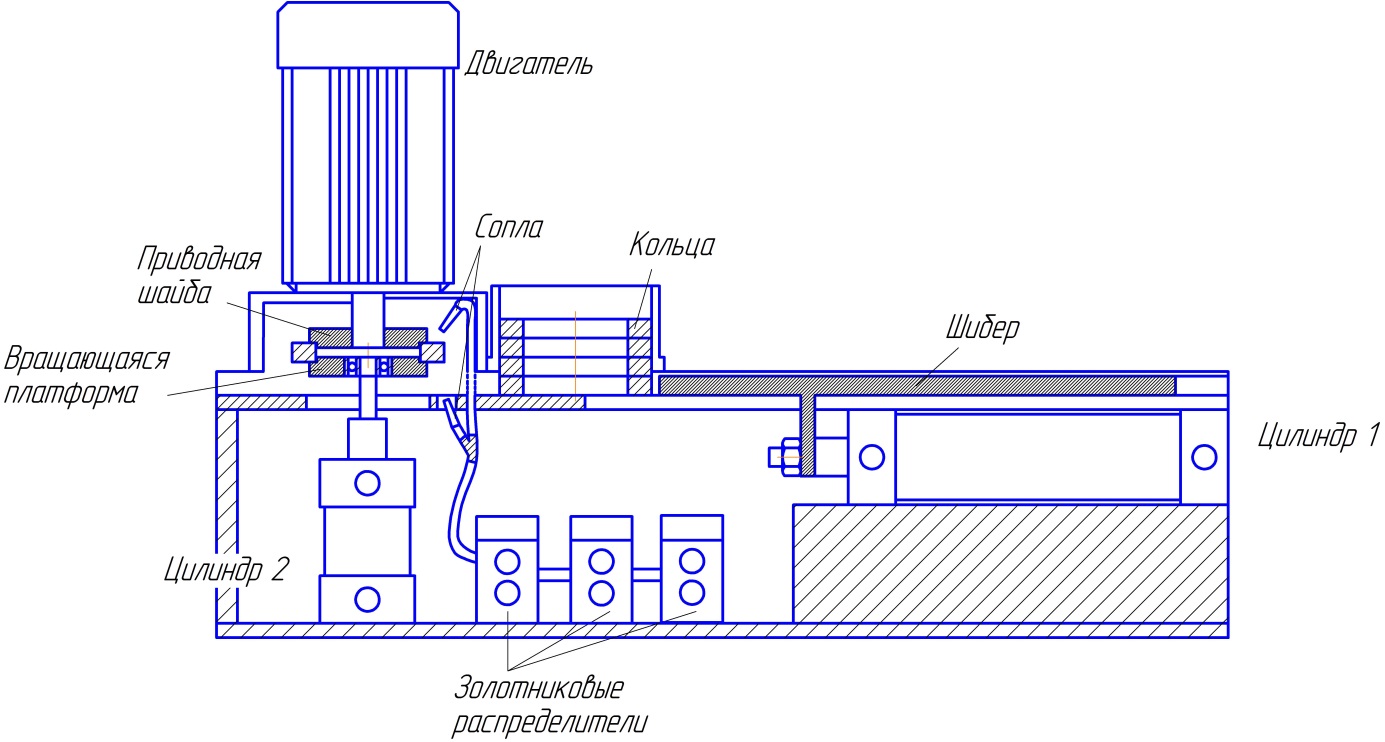

Узел подачи колец в зону сушки состоит из пневматических цилиндров, которые управляются с помощью золотниковых распределителей. Шток первого цилиндра соединен с шибером, толкающим кольцо подшипника до вращающейся платформы, поднимаемой вторым цилиндром до упора в приводную шайбу. Начальное «назад» и конечное «вперед» положения шибера, контролируются контактным датчиком K1, сигнализирующим о прибытии шибера в конечное положение, после чего шибер отправляется в начальное положение. Второй цилиндр поднимает платформу с кольцом в верхнее положение, где происходит вращение кольца, и его обдув. Продолжительность вращения платформы и обдува задается контроллером. В верхнем положении также стоит контактный датчик K2, отправляющий сигнал на контроллер. По прошествии определенного времени привод вращения отключается и кольцо опускается в свое начальное положение.

Рис. 10.2. Схема установки автоматизированной сушки

подшипниковых колец

Рассмотрим вербальное пошаговое описание алгоритма управления сушкой подшипниковых колец:

1. При нажатии кнопки «ПУСК» (Z) или «ПУСК N» (Zn) шибер начинает движение вперед и толкает кольцо до платформы. При этом зажигается светодиод «ПУСК» или «ПУСК N».

2. После того как шибер дошел до конечного положения «вперед», срабатывает датчик K1.

3. Сигнал с датчика K1 отправляет шибер в начальное положение «назад», при этом сигнал с датчика обнуляется.

4. Как только перестает приходить сигнал с датчика K1, включается привод подъема кольца.

5. Когда кольцо доходит до верхнего положения, срабатывает датчик K2.

6. Сигнал с датчика K2 запускает привод вращения кольца и его обдув, а также таймер T на tn секунд.

7. По истечении tn секунд, таймер Т отправляет сигнал на выключение вращения и обдува кольца. После остановки кольцо опускается в нижнее положение.

8. Если в пункте 1 была нажата кнопка «ПУСК» (Z), на этом цикл заканчивается.

9. При нажатии в пункте 1 кнопки «ПУСК N» (Zn), вышеописанный цикл автоматически повторяется n раз, число n задается в программе.

10. Остановка программы в любой момент времени осуществляться с помощью кнопки «СТОП». Происходит сброс программы.

Дата добавления: 2021-01-26; просмотров: 1392;