QUIT CLR LATC PGFOR PGBAK

Перейти к пункту <QUIT> .Указать свободную зону вокруг размещаемых РЭК командой CLR. Перейти к пункту CLR <Пробел>,указать свободную зону по оси X, по оси Y.Величину можно принять по умолчанию. Перейти к пункту <QUIT> .

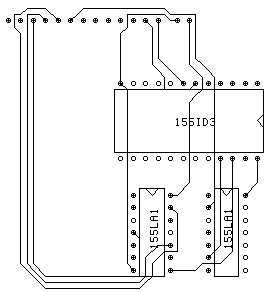

Теперь требуется осуществить улучшение размещения, используя итерационный алгоритм попарных перестановок как самих корпусов РЭК, так и взаимозаменяемых вентилей в одноименных РЭК. Командами перестановок будут, соответственно, IMPR/COMP и IMPR/GATE.После этой команды произойдёт расстановка РЭК, рис. 7.5.

Рис. 7.5. Расстановка РЭК

Результаты авторазмещения в ряде случаев требуют ручной коррекции. C помощью команд MOVE – перемещение и ROT – вращение можно осуществить ручное размещение РЭК. После этого следует сохранить файл командой SYS/SAVE.

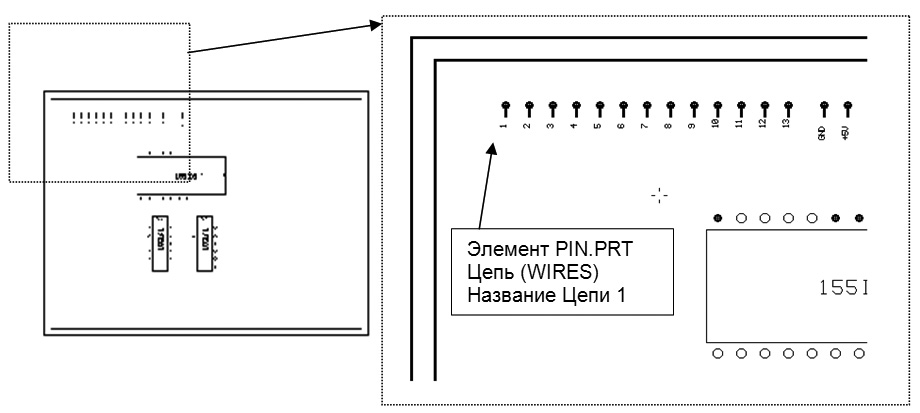

Затем следует перейти к пункту PLACE <Пробел>. У печатной платы есть выводы (разъем), которые обозначены цифрами 1,2,3,4...12. Чтобы их создать, требуется воспользоваться программой PC-CARDS.Для этого нам понадобится специальный РЭК - PIN.PRT. Этот файл требуется найти и скопировать к себе в директорию 1.

Далее необходимо:

- запустить PC-CARDS;

- загрузить файл a.pkg.

Для удобства размещения выводов следует отключить сетку размещения РЭК или слой LAT1.Для этого перейдите к команде DRAW->LINE. Выберите в левом нижнем углу экрана слой COMP или какой-либо другой, но не LAT1.Перейдите к команде VLYR и напротив неё установите значение OFF.

Далее следует:

- командой ENTER/COMP вставить в место размещения вывода 1 элемент PIN.PRT (на вопрос "New layers may be added.Continue?" выбрать ответ YES);

- расположите РЭК PIN.PRT в местах выводов 1...12;

-командой ENTER/WIRE нарисуйте небольшой участок цепи от элемента PIN;

- командой NAME/NETназовите цепи именами 1...12;

(на вопрос Net ... exist.Merge? выбрать ответ YES);

- после этого сохраните файл. Пример приведён на рис.7.6.

Рис. 7.6. Пример размещения выводов

Командой F5 скопируйте файл a.pkg в файл a.plc. Автоматизированное получение топологии (трассировки) ПП происходит в программе PC-ROUTE:

-запуститьPC-ROUTE;

- нажать клавишу HOME на клавиатуре и перейти к пункту Enter database name:, где ввести имя файла a <Enter>,после чегодолжно ввестись имя файла a.plc;

-нажать клавишу <Escape>, перейти к пункту Route <Еnter>;

- перейти к пункту <<Start>> <Enter>;

-разведённая печатная плата должна сохраниться в файле с именем a.pcb.

Разведённую печатную плату можно просмотреть с помощью программы PC-CARDS:

-запустить PC-CARDS;

- загрузить файл a.pcb;

- перейти к пункту DRAW/LINE: в левом нижнем углу будет отображаться слой, который сейчас активен (в данный момент, COMP), измените его на слой PIN;

- перейти к пункту VLYR меню;

- отключить слой LAT1, то есть напротив слоя поставить значение OFF.

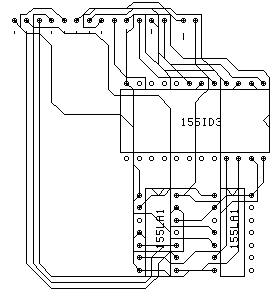

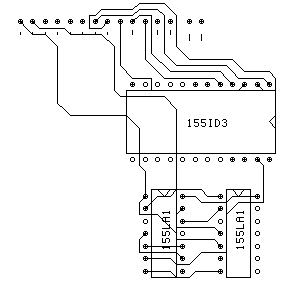

В данный момент видны два слоя (рис. 7.7):

Рис. 7.7. Общий вид условно прозрачной печатной платы

слой SOLDER – слой пайки,

слой COMP – слой компонентов.

Делая один слой активным-ON, а другой нет-OFF, мы можем видеть каждую из сторон печатной платы (рис. 7.8).

|

|

Сторона компонентов, слой COMP Сторона пайки, слой SOLDER

Рис.7.8. Рисунки слоев печатной платы

8 ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ

ИНТЕГРАЛЬНЫЕ СХЕМЫ

Еще недавно в распоряжении разработчика цифровых электронных устройств имелась лишь "жесткая" логика. Искусство проектирования заключалось в достижении поставленной цели с помощью минимального числа микросхем, способных выполнять лишь строго определенные функции. Устройство отлаживали и совершенствовали, перерезая печатные проводники и "навешивая" проволочные перемычки и дополнительные детали. Нередко ошибки, допущенные на этапе проектирования, удавалось исправить только ценой изготовления новой печатной платы.

Микропроцессоры ситуацию почти не изменили, ведь каждый из них требует довольно сложной "обвязки" из обычных логических элементов. К тому же во многих случаях специализированные цифровые устройства решают задачу эффективнее универсальных микропроцессорных.

Революция началась с появлением микросхем ППЗУ и программируемых логических матриц (ПЛМ или PLD - programmable logical device). Пережигая с помощью программатора предусмотренные в них плавкие перемычки, разработчик получил возможность реализовать в одной микросхеме десяток почти любых логических функций. Но микросхему с лишней пережженной перемычкой приходилось выбрасывать. Типичные представители однократно программируемых ППЗУ и ПЛМ - отечественные приборы серий 556 и 1556. Многократно программируемые ПЗУ с ультрафиолетовым стиранием, к сожалению, мало подходят для реализации логических функций из-за недостаточного быстродействия.

Некоторое распространение получили "заказные" микросхемы на основе БМК — базовых матричных кристаллов, выпускавшихся, например, в сериях К1515, К1520. БМК содержит сотни логических элементов и способен заменить несколько десятков микросхем малой и средней степени интеграции. Элементы соединяют прямо на кристалле по нужной заказчику схеме на последних этапах производственного цикла. Естественно, заказывать такие микросхемы имеет смысл при потребности не менее нескольких сотен штук, а изменить что-либо в готовом приборе уже невозможно.

Дальнейшее развитие технологии ПЛМ и БМК привело к созданию программируемых логических интегральных схем (ПЛИС). Реализуемые ими функции можно многократно изменять, нередко для этого даже не нужно извлекать микросхему из устройства, в котором она работает.

Подобно БМК, кристалл ПЛИС содержит большое число однотипных логических элементов. Основное отличие в том, что соединяют элементы в нужном порядке с помощью электрически программируемых перемычек — ключей на полевых транзисторах. А в каждом логическом элементе имеются переключатели (мультиплексоры), программируя которые, можно изменять выполняемые функции.

Почти все внешние выводы ПЛИС универсальны. Любой из них может служить входом, выходом или быть двунаправленным. Некоторые выводы имеют дополнительные функции, например, служат для программирования конфигурации микросхемы, что, однако, не исключает их использования в качестве обычных входов или выходов.

По внутренней структуре и способу запоминания конфигурации ПЛИС фирмы XILINX можно разделить на два вида: FPGA (field programmable gate array - матрица вентилей, программируемых электрическим полем) и CPLD (complex programmable logic device - сложная программируемая логическая матрица).

К FPGA относят микросхемы серий ХС2000, ХС3000, ХС4000, ХС5200, ХС6000 и SPARTAN. Подобно ОЗУ, они сохраняют заданную конфигурацию только при включенном питании и "забывают" ее после выключения. Каждый раз, включив питание, такую ПЛИС необходимо программировать заново. Программу обычно хранят в установленном на одной плате с ПЛИС загрузочном ПЗУ, которое может быть последовательным одноразрядным или обычным восьмиразрядным. Способ загрузки конфигурации задают логическими уровнями на управляющих входах. Процедура перезаписи выполняется автоматически, после чего ПЛИС переходит в рабочий режим.

В одном ПЗУ допускается хранить информацию для нескольких ПЛИС. Одна из них служит ведущей (master) и, закончив собственную загрузку, управляет записью данных в ведомые (slave) микросхемы. Назначение ведущей или ведомой никак не влияет на логические функции, выполняемые ПЛИС после загрузки.

Специально для совместной работы с ПЛИС фирма XILINX разработала и выпускает серию однократно программируемых последовательных ПЗУ ХС1700 информационной емкостью, достаточной для всех выпускаемых этой фирмой ПЛИС структуры FPGA.

К CPLD относят микросхемы серий ХС7000 и ХС9500. Они сохраняют конфигурацию независимо от наличия питающего напряжения. В микросхемы ХС7000 конфигурацию заносят с помощью программатора, а стирают ультрафиолетовым излучением. Такие ПЛИС устанавливают, как правило, в уже отлаженные устройства. Для отладки новых изделий они неудобны из-за длительной (до часа) процедуры очистки.

Микросхемы серии ХС9500, выполненные по технологии FLASH, можно неоднократно программировать, не извлекая из устройства, в которое они установлены. Для этого в них предусмотрен специальный порт JTAG. Чтобы записать исходную конфигурацию или внести в нее изменения, выводы этого порта через несколько буферных микросхем соединяют кабелем с портом LPT персонального компьютера.

Порт JTAG полезен не только для программирования. Через него компьютер может получить информацию о логических уровнях на всех выводах ПЛИС и в контрольных точках внутри нее. Возможность организовать такой порт предусмотрена и в ПЛИС структуры FPGA последних серий. Выводы микросхемы, занятые портом JTAG, мргут служить и обычными входами/выходами.

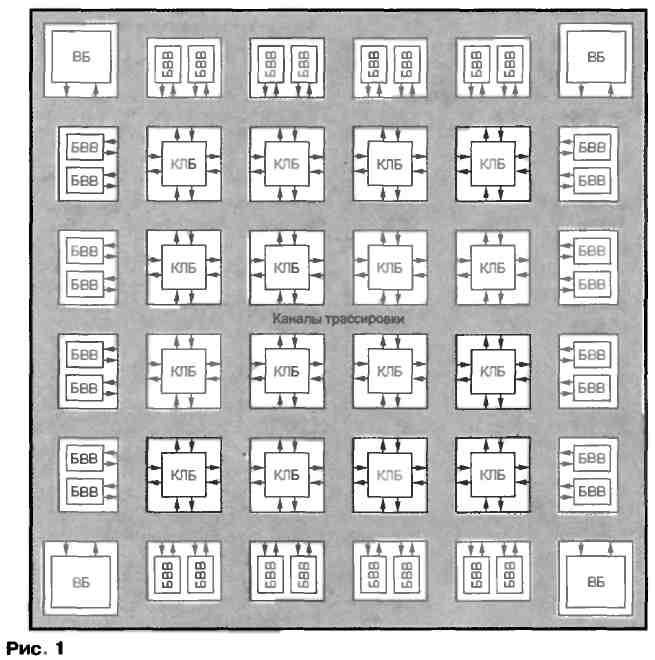

На рис. 8.1 схематически показана структура кристалла микросхемы FPGA. Его центральную часть занимает матрица конфигурируемых логических блоков (КЛБ), а по периметру находятся блоки ввода/вывода (БВВ), соединенные с контактными площадками. Представление о сложности современных ПЛИС дает таблица 1, где приведены сведения о числе КЛБ и БВВ, имеющихся в FPGA серии ХС4000. Вентили и триггеры в данном случае не самостоятельные элементы, а входят в состав указанных блоков.

Рис.8.1. Структура кристалла микросхемы FPGA

Таблица 8.1

Число КЛБ и БВВ, имеющихся в FPGA серии ХС4000

| Микросхема | На кристалле имеются | Длина программы, бит | |||

| КЛБ | БВВ | Вентили | Триггеры | ||

| ХС4005 ХС4010 ХС4013 ХС4020 ХС4028 ХС4036 ХС4044 ХС4052 ХС4062 ХС4085 | 784 1024 1286 1600 1936 2304 3136 | 5000 10000 13000 20000 28000 36000 44000 52000 62000 85000 | 151 910 283 376 393 580 521 832 668 132 832 480 1 014 876 1 215 320 1 433 812 1 924 940 |

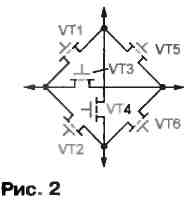

Каждый из БВВ способен быть входным или выходным, а связанный с ним внешний вывод микросхемы — входом (IPAD), выходом (OPAD) или быть двунаправленным (IOPAD). По углам кристалла расположены вспомогательные узлы. Свободную от логических элементов площадь занимают каналы трассировки, где проложено большое число проводников, на пересечениях которых находятся программируемые ключи. Каждый ключ состоит из шести полевых транзисторов, соединенных, как показано на рис. 8.2.

Рис.8.2. Схема ключа

Задавая открытое или закрытое состояние каждого транзистора, можно соединить КЛБ между собой и с БВВ нужным образом.

К сожалению, такая структура не всегда позволяет реализовать необходимую конфигурацию. В сложных устройствах с большим числом длинных нерегулярных связей удается использовать не более половины ресурсов кристалла.

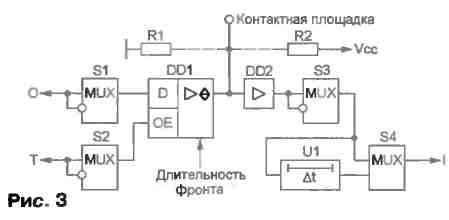

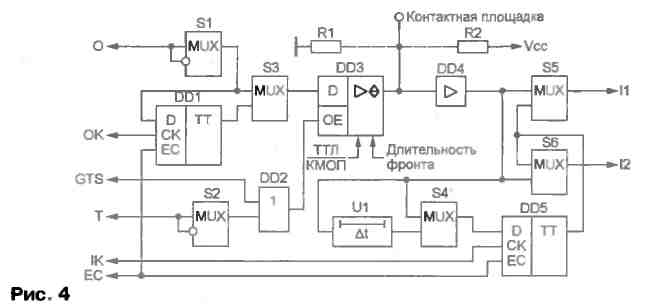

Схема самого простого БВВ (он применяется в микросхемах серии ХС5200) показана на рис. 8.3. Контактная площадка кристалла соединена с выходом управляемого буфера DD1 и с входом буфера DD2. Предусмотрена возможность задать исходный логический уровень на входе, связывая контактную площадку с общим проводом через резистор R1 или с шиной питания через резистор R2. Программируемые переключатели S1, S2 обеспечивают прямую или инверсную связь БВВ с матрицей КЛБ. С помощью переключателя S3 при необходимости инвертируют входной сигнал. Линия задержки U1 служит для выравнивания времен распространения сигналов по различным цепям ПЛИС. Буфер DD1 снабжен устройством программирования длительности фронта выходного сигнала. Пологий фронт, не снижая внутреннего быстродействия ПЛИС, избавляет от "звона" при плохом согласовании внешней нагрузки БВВ.

Рис 8.3. Схема простого БВВ

БВВ микросхем FPGA других серий сложнее (рис. 8.4) и дополнительно снабжены двумя D-триггерами, с помощью которых можно запоминать значения входных и выходных сигналов. В некоторых случаях предусмотрена настройка на логические уровни сигналов, характерные для микросхем структуры КМОП или ТТЛ.

Рис.8.4. Схема БВВ

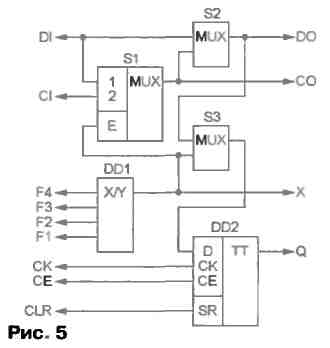

КЛБ микросхемы серии ХС5200 состоит из четырех микроячеек, выполненных по схеме, приведенной на рис. 8.5. Каждая ячейка содержит генератор произвольной логической функции четырех переменных DD1 (РПЗУ на 16 бит) и триггер DD2. Все четыре триггера одного КЛБ имеют общие входы сигналов асинхронного сброса (CLR), синхронизации (СК) и разрешения (СЕ).

Рис.8.5. Схема микроячейки

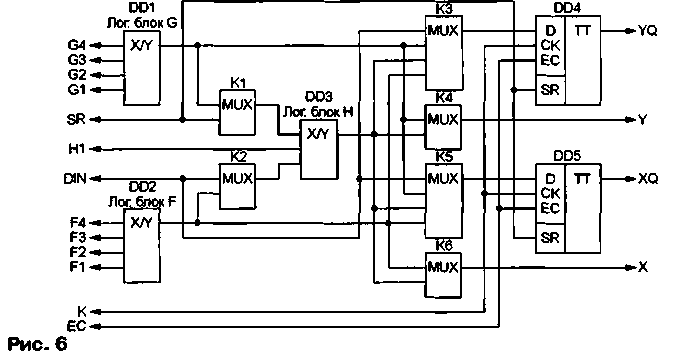

В состав КЛБ микросхем FPGA серий ХС3000 ХС4000 и Spartan (рис. 8.6) входят по два логических блока (DD1, DD2) и D-триггер (DD4, DD5). Выходные сигналы блоков DD1 и DD2 могут быть дополнительно обработаны логическим блоком DD3.

Рис 8.6. Состав КЛБ микросхем FPGA серий ХС3000 ХС4000

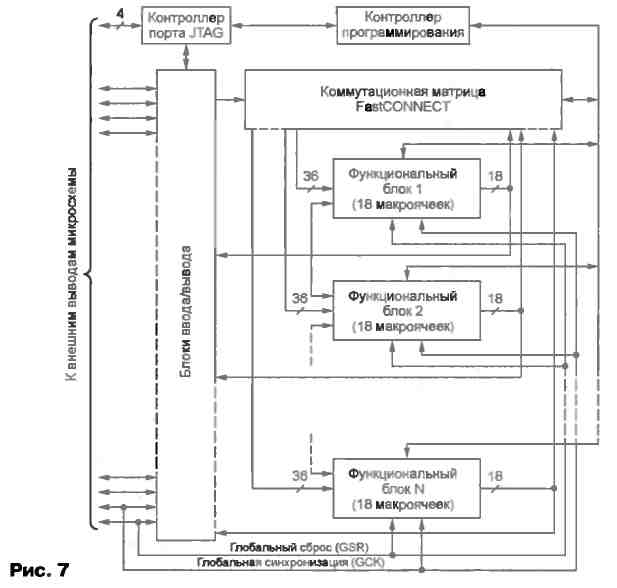

По сравнению с FPGA, структура CPLD более "крупнозерниста". Рассмотрим ее на примере микросхем серии ХС9500, структурная схема которых приведена на рис. 8.7, а сведения о составе — в табл. 8.2. Указанные там же максимальные частоты относятся к 16-разрядным двоичным счетчикам, реализованным на таких ПЛИС. Следует иметь в виду что рассматриваемая серия — сравнительно медленная. Счетчики из элементов других ПЛИС способны работать на частотах до 350 МГц.

Рис.8.7. Структура CPLD

Таблица 8.2

Сведения о составе микросхем серии ХС9500

| Микросхема | На кристалле имеются | Макс, частота счета, МГц | |

| Макроячейки | Вентили | ||

| ХС9536 | |||

| ХС9572 | |||

| ХС95108 | |||

| ХС95144 | |||

| ХС95216 | 111,1 | ||

| ХС95288 | 111,1 |

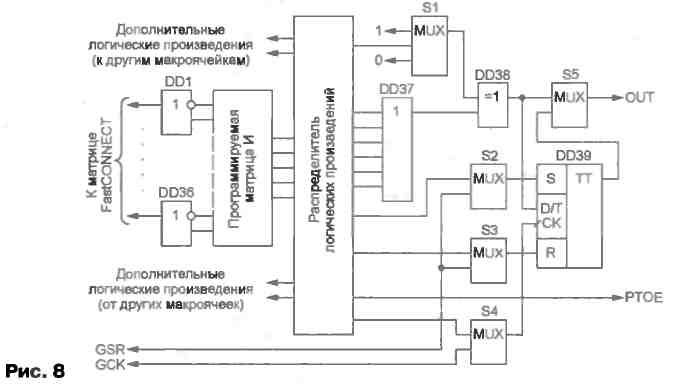

Схема макроячейки логического блока ПЛИС серии ХС9500 приведена на рис.8.8. С помощью программируемой матрицы И формируют до пяти логических произведений 36-ти переменных, еще два произведения можно взять от соседних макроячеек. На выходе элемента ИЛИ (DD37) образуется логическая сумма этих произведений, которая поступает на вход переключателя S5 и триггера DD39 в прямом или проинвертированном виде в зависимости от положения программируемого переключателя S1. В одном из положений последнего инверсией управляет сигнал, сформированный в распределителе логических произведений. Сигналами с других выходов распределителя тактируют, устанавливают и сбрасывают триггер DD39. Изменив положение переключателей S2—S4, эти функции можно выполнять с помощью глобальных сигналов синхронизации и сброса, поступающих непосредственно с выводов ПЛИС.

Рис.8.8. Схема макроячейки логического блока ПЛИС серии ХС9500

В составе БВВ ПЛИС серии ХС9500 имеются только буферы ввода и вывода, триггеров в них нет. Перевести выход БВВ в активное состояние можно с помощью сигнала РТОЕ, поступающего от макроячейки, либо одного из глобальных сигналов GOE1 —GOE4, формируемых специальным программируемым логическим блоком из входных сигналов ПЛИС. Цепи OUT и РТОЕ каждой макроячейки ПЛИС CPLD связаны только с одним блоком ввода/вывода, который в свою очередь соединен с определенным внешним выводом. В FPGA такой жесткой связи нет.

Соединения функциональных блоков между собой и с входными цепями БВВ реализуют с помощью программируемой коммутационной матрицы, фирменное название которой FastCONNEC можно перевести как "быстрое соединение". Матрица обладает регулярной структурой, обеспечивает одинаковую задержку распространения всех сигналов и, самое главное, гарантирует трассировку всех необходимых связей. Последнее позволяет произвольным образом распределять по выводам ПЛИС внешние цепи разрабатываемого устройства.

Приступая к проектированию устройства на ПЛИС, следует подготовить его схему с помощью любого их известных схемных редакторов, например, популярного ORCAD. При этом нет необходимости разбираться в тонкостях логической организации ПЛИС. Устройство создают из типовых логических элементов, триггеров, буферов, мультиплексоров, сумматоров дешифраторов, счетчиков, регистров сдвига, в том числе — эквивалентов распространенных микросхем серии 74 (отечественный аналог — серия К155). Фирма XILINX предлагает разработчикам готовые библиотеки таких элементов, а задачу "упаковки" устройства в ПЛИС решает специализированная система автоматизированного проектирования (САПР) XILINX FOUNDATION. Кроме имени исходного файла со схемой, системе достаточно сообщить типы микросхемы и ее корпуса. Главный результат работы САПР — двоичный файл, предназначенный для загрузки в ПЛИС. Она создает и вспомогательные текстовые файлы, например, с описанием реализованного САПР распределения внешних цепей по выводам ПЛИС.

Замечательная особенность XILINX FOUNDATION — встроенная программа логического моделирования, позволяющая на любом этапе ввода схемы проверить работу отдельных узлов, а затем и всего устройства. Достаточно назначить контрольные точки (входы и выходы), "подать" входные тестовые сигналы и просмотреть временные диаграммы выходных. При вводе сложных схем оперативное моделирование позволяет обнаружить и вовремя исправить грубые ошибки. Число контрольных точек может достигать тысячи. Так как работа спроектированного устройства зависит не только от правильной реализации логических функций, но и от скорости переключения элементов и распространения сигналов, есть возможность выполнить моделирование с учетом задержек. Но эта операция доступна только после размещения всех элементов устройства на кристалле и полной трассировки связей.

САПР снабжена программами автоматической упаковки типовых элементов в кристалл и трассировки связей. Дополнительно для ПЛИС многих типов предусмотрено «ручное управление» конфигурацией с помощью специального редактора. Однако эту трудоемкую работу следует предпринимать только в крайних случаях, если, например, необходимо добиться максимального быстродействия проектируемого устройства или САПР не справляется с задачей в автоматическом режиме.

Фирменный пакет программ XIUNX FOUNDATION стоит довольно дорого. Фирма предлагает бесплатную версию ПЛИС, позволяющей делать все, за исключением последнего этапа — получения файла "прошивки". Чтобы спроектировать устройство, можно подготовленные и проверенные исходные данные, полученные в бесплатной версии САПР, отправлять по электронной почте на сайт фирмы XILINX, где их оттранслируют в загрузочный файл и вернут обратно.

Дата добавления: 2021-01-26; просмотров: 584;