Логические элементы

Выше уже были упомянуты три логические схемы – И, ИЛИ и НЕ. Рассмотрим их подробнее. В простейшем варианте схемы И (второе название – конъюнктор) и ИЛИ (дизъюнктор) имеют по два входа и один выход (входов может и больше, однако принцип действия схем при этом не изменяется). Количество входов часто включают в название схемы вместе с ее функцией: так, схему И с двумя входами обозначают как 2И. Условное обозначение схемы 2И приведено на рис.11.1. В табл. 11.1, именуемой «таблицей истинности» или «таблицей состояния» показана связь сигнала на выходе схемы с входными. Поскольку каждый сигнал может принимать только два значения, то возможны четыре комбинации входных сигналов. Очевидно, что уровень U1 на выходе схемы И достигается только при наличии такого же уровня одновременно на всех ее входах (и на первом входе, и на втором).

| Табл. 11.1 | |||||||||||||||

| ||||||||||||||||

| Рис.11.1 |

Схема И является, в известной степени, аналогом электронного ключа. Однако все входные сигналы схемы И «равноправны», в то время как в аналоговых электронных ключах к управляющему сигналу ставят более жесткие требования (он должен быть двухуровневым), в то время как второй входной сигнал может быть любым. Таким образом, в цифровой электронике ключ эквивалентен схеме И, а в аналоговой – нет.

| Табл. 11.2 | |||||||||||||||

| ||||||||||||||||

| Рис.11.2 |

На рис.11.2 приведено условное обозначение схемы 2 ИЛИ, а табл.11.2 является ее «таблицей истинности» («таблицей состояния»). В рассматриваемом случае также возможны четыре комбинации входных сигналов, однако в отличие от схемы И на выходе схемы ИЛИ U1 «появляется», если хотя бы на одном из входов имеет место такой сигнал (или если U1 подан на несколько входов сразу). Таким образом, на выходе схемы ИЛИ U1 оказывается вероятнее, чем U0 – именно этот факт подчеркивает значок единицы внутри прямоугольника на условном обозначении схемы.

Проще всех «логика» схемы НЕ (условное обозначение – рис.11.3, «таблицей истинности» - табл. 11.3). Если на входе этой схемы U1, то на выходе U0и наоборот. Эта операция с сигналом называется логической инверсией. В привычном нам десятичном счислении инверсным к +1 значением является −1, но в «булевой» алгебре отрицательных чисел нет, да и вообще выбор невелик: если не «единица» - значит «ноль». О различии в инверсиях в аналоговой и цифровой частях электроники следует постоянно помнить.

| Табл. 11.3 | ||||||||||||

| |||||||||||||

| Рис.11.3 |

Схемы И, ИЛИ и НЕ можно реализовать на самых разных элементах – на диодах, транзисторах, многосеточных радиолампах, магнитных колечках и т.д. Однако в течение последних десятилетий их выпускают исключительно в виде монокристаллических интегральных микросхем, причем в одном кристалле как правило содержится несколько логических схем.

11.2. RS-триггер

Триггер – это схема с двумя устойчивыми состояниями, поменять которые можно только, подав входное воздействие. Тем не менее, триггер в схемотехническом плане исключительно близок к ждущему мультивибратору, чуть дальше отстоит от мультивибратора автоколебательного. В последние десятилетия триггеры выпускают исключительно в виде монокристаллических интегральных микросхем, однако для понимания физики процессов в этой важнейшей цифровой схеме вернемся в прошлое и рассмотрим триггер на биполярных транзисторах.

Схема триггера на транзисторах приведена на рис. 11.4. Схема отличается абсолютной симметричностью, однако это не является ее главной особенностью. Сравнение схемы триггера со схемой транзисторного ждущего мультивибратора рис. 10.9 показывает, что у ЖМВ имеется зарядная цепь в составе конденсатора и базового сопротивления, а у триггера ее заменяет базовый делитель (у ЖМВ такой делитель тоже есть, но он единственный, а у триггера делителей два).

В этом схемотехническом решении заключено главное отличие триггера от мультивибратора: ведь базовый делитель задает устойчивость состояния схемы. У ЖМВ делитель один – и устойчивое состояние единственное, у триггера делителей два – соответственно и два устойчивых состояния. Перезаряд конденсатора в ЖМВ вызывает самопроизвольное переключение этой схемы, у триггера конденсатора нет – не может быть и самопроизвольного переключения.

|

| Рис.11.4 |

Поскольку входные (переключающие) воздействия должны поступать на базы обоих транзисторов триггера, то схема имеет два входа. Наличие дифференцирующих цепей и диодных ограничителей во входных цепях делает входные воздействия краткосрочными. Если на входе триггера длительное время поддерживался уровень U0, то при его замене на U1 короткий импульс через входную цепь достигнет базы соответствующего транзистора, а при переходе U1от к U0 – не пройдет через диодный ограничитель. Подача двух и более сигналов подряд на один и тот же вход приведет к переключению триггера только по первому импульсу, да и то если он поступит в базу запертого транзистора.

Выходные сигналы триггера формируются на коллекторах транзисторов. Если транзистор открыт (находится в зоне насыщения), то на его коллекторе практически ноль и выходной сигнал схемы - U0. Если же транзистор закрыт (находится в зоне отсечки), то потенциал коллектора близок к напряжению коллекторного питания и воспринимается как U1. Поскольку оба транзистора не могут быть одновременно открыты или одновременно закрыты (объяснение этого факта см. в п. 10.4 ), то это означает, что состояние одного выхода логически инверсно состоянию другого выхода. Иначе говоря, если на одном выходе U1, то на другом - U0 и наоборот.

Поскольку схема триггера абсолютно симметрична, приходится различать входы и выходы на уровне условной маркировки. Так, один из выходов считается «главным» и обозначается буквой Q. Тогда второй выход называется «инверсным» и для сигнала на нем используется  (черта в «булевой» алгебре означает инверсию). Различают и входы: вход, при подаче сигнала на который на главном выходе устанавливается «единица» (если ее там не было), называется S-входом; вход, при подаче сигнала на который на главном выходе устанавливается «ноль» (если его там не было), называется R-входом.

(черта в «булевой» алгебре означает инверсию). Различают и входы: вход, при подаче сигнала на который на главном выходе устанавливается «единица» (если ее там не было), называется S-входом; вход, при подаче сигнала на который на главном выходе устанавливается «ноль» (если его там не было), называется R-входом.

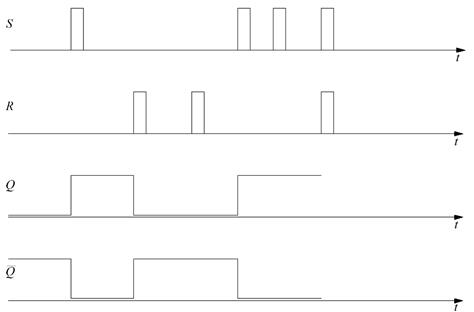

Поскольку триггер имеет два входа, то его называют триггером с раздельными входами, а по буквам маркировки входов – RS-триггером. Принцип действия схемы поясняют диаграммы напряжений на ее входах и выходах рис.11.5. Обращает на себя внимание ситуация, когда на оба входа одновременно поступают импульсы: один из них стремится открыть запертый транзистор, второй – поддержать открытое состояние другого транзистора.

|

| Рис.11.5 |

Поскольку одновременно транзисторы открыться не могут, возникает «противоборство» с неопределенным результатом. Эксплуатировать схему, на выходах которой то или иное состояние может установиться случайно, невозможно. Поэтому RS-триггер дополняют двумя схемами 2И – такой триггер называется JK- триггером.

Рассмотрением принципа действия RS-триггера воспользуемся также для пояснения термина «коэффициент разветвления по выходу» (или, что то же самое – «нагрузочная способность»). Эти понятия одинаково справедливы для всех типов триггеров и имеют большое значение при создании сложных цифровых схем. Выше уже упоминалась одна из главных угроз цифровой электроники – перепутывание U1 и U0. Очевидно, что эта угроза нарастает, если уровни логической единицы и логического нуля отклоняются от номинальных значений и сближаются друг с другом и с порогом.

Определим значения U1 и U0 ненагруженного триггера. U0 формируется на коллекторе открытого (насыщенного) транзистора и его значение в вольтах равно падению напряжения между коллектором и эмиттером тразистора (эмиттер при этом заземлен), иначе говоря U0 = ∆Uкэ нас.

U1 также выделяется на коллекторе, но закрытого (находящегося в режиме отсечки) транзистора, через который течёт небольшой ток неосновных носителей Iко. Этот ток протекает также через коллекторное сопротивление Rк, создавая на нем падение напряжения. Через Rк течет также ток базового делителя Iдел.. Наличие обоих токов приводит к тому, что потенциал коллектора закрытого транзистора меньше напряжения источника коллекторного питания Ек (а значит и уровень U1) равен

U1 = Ек − (Iко + Iдел.)∙Rк.

Формула для уровня логической единицы получена для случая ненагруженного триггера – очевидно, что работа схемы в режиме, когда сигнал с ее выхода никуда не поступает, практически бессмысленна. Но, если к триггеру подключить нагрузку, то через нее и через Rк потечет ток нагрузки Iн. Уровень логической единицы понизится и составит

U1 = Ек − (Iко + Iдел. + Iн)∙Rк.

При N нагрузках (принимается, что в цифровой электронике все нагрузки одинаковы) происходит дальнейшее понижение U1 до уровня

U1 = Ек − (Iко + Iдел. + N Iн)∙Rк.

Максимальное количество нагрузок N, при котором сохраняется условие U1 >Uпор, называют нагрузочной способностью (или коэффициентом разветвления, подразумевая под этим термином разветвление сигнала с выхода триггера по входам других цифровых схем). При проектировании сложных цифровых схем следует иметь в виду, что приближение количества нагрузок к предельному значению с одной стороны упрощает схему, а с другой – повышает вероятность перепутывания нуля с единицей.

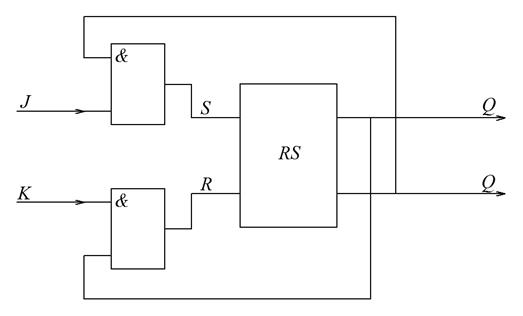

11.3. JK- триггер

JK-триггер относится к группе триггеров с раздельными входами. Название схемы по-русски принято читать или на немецкий лад «йот-ка-триггер», или на французский – «жи-ка-триггер». Функциональная схема JK- триггера приведена на рис.11.6. Как видно, JK- триггер состоит из RS-триггера и двух схем 2И. Внешний вход J через одну из схем И соединен со входом S RS-триггера, а вход K – со входом R.

|

| Рис.11.6 |

(внимание: в названиях JK- триггера и RS-триггера входы, выполняющие одну и ту же функцию, расположены в разном порядке!).

Поскольку одна из схем И соединена с главным выходом RS-триггера, а вторая – с его инверсным выходом, то всегда одна из них блокирует прохождение сигнала с внешнего входа JK- триггера на внутренний вход RS-триггера. Одновременное поступление импульсов на оба входа RS-триггера исключено. Входной сигнал пройдет только через схему И, соединенную с выходом, на котором сигнал имеет значение U1. Триггер обязательное однозначно переключается во всех случаях одновременной подачи импульсов на оба входа.

Счетный триггер

Принципиальная электрическая схема счетного триггера на транзисторах (Т-триггера) приведена на рис.11.7. От схемы RS-триггера (рис.11.4.) она отличается наличием так называемого счетного входа (Т-входа), соединенного одновременно с базами обоих транзисторов.

|

| Рис.11.7. |

Импульс, поступающий на счетный вход, за счет разветвленного диодного ограничителя сам «выбирает» траекторию своего движения по электрическим цепям и всегда поступает в базу запертого транзистора, вызывает его отпирание и, как следствие, переключение триггера.

Таким образом, каждый импульс, поступающий на счетный вход, переключает триггер. Однако результат лишь кажется однозначным – он зависит от первоначального (после подключения схемы к источнику питания) состояния схемы. Например, если первоначально правый транзистор был отперт, т. е. на главном выходе был уровень U0, то по поступлению первого счетного импульса он сменится на U1. А если правый транзистор был заперт, то смена уровней будет обратной.

Первоначальное переключение, если оно оказалось нежелательным, неустранимо – уровень U1 на главном выходе будет устанавливаться по каждому нечетному импульсу на Т-входе – а при ином исходном состоянии по каждому четному. Чтобы устранить указанную неопределенность, в триггере кроме счетного входа предусматривают наличие S-входа («входа установки единицы» - на главном выходе) и R-входа («входа установки нуля»).

Принцип действия схемы поясняют диаграммы напряжений на ее входах и выходах рис.11.8.

|

| Рис.11.8. |

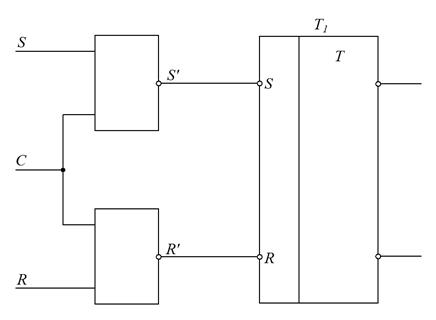

Синхронный триггер

При значительном количестве триггеров (в электронных устройствах их количество достигает миллионов) необходимо обеспечить их синхронное переключение. Эту задачу решает высокостабильный тактовый генератор (синхронизатор), а сами синхронизируемые триггеры соединяют с его выходом. Пример синхронизации RS-триггера изображен на рис.11.9. Триггер, на

|

| Рис.11.9 |

который не поступает синхросигнал, называют асинхронным, а при наличии синхронизации – синхронным; при этом в название триггера добавляют букву С (в английском языке слово «синхронизация» начинается с этой буквы, произносимой как «си»). Таким образом, на рис.11.9 изображена функциональная схема RSС –триггера.

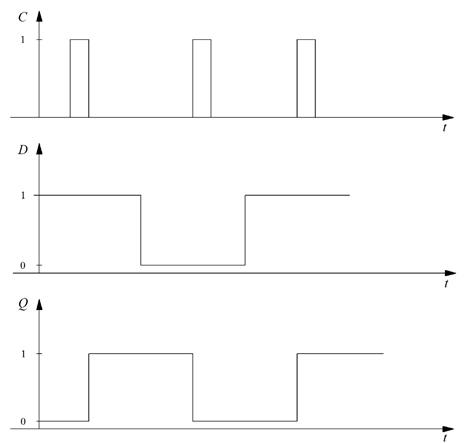

Принцип действия схемы поясняют диаграммы напряжений на ее входах и выходах рис.11.10.

Триггер задержки

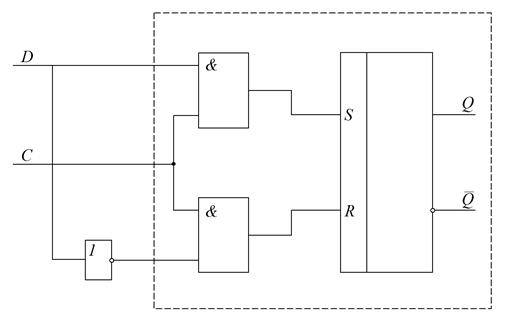

Триггер задержки (или D-триггер) является одним из вариантов синхронного триггера. Его функциональная схема приведена на рис.11.11., а принцип действия поясняют диаграммы напряжений на ее входах и выходах рис.11.12.

Можно представить D-триггер, как комбинацию RSС –триггера и схемы НЕ (а RSС –триггер, в свою очередь, является комбинацией RS –триггера и двух схем И). Наличие инвертора приводит к тому, что сигналы на R’ и S’-входах RSС –триггера оказываются взаимно инвертированными. Однако до одного из входов RS- триггера они доходяттолько при поступлении тактового импульса.При этом на выходе Q триггера воспроизводится сигнал со входа D. Таким образом, триггер является повторителем входного сигнала, но с задержкой во времени.

|

| Рис.11.10 |

|

| Рис.11.11 |

|

| Рис.11.12 |

Дата добавления: 2016-10-07; просмотров: 2112;