Синхронні лічильники

У Розділі 7 в якості скінченних автоматів розглядалися лічильники, в яких синхросигнали та інформаційні сигнали, що записуються в тригери, розділені по входу. В таких схемах інформаційний сигнал, що записується у тригер, підготовляється одразу після встановлення попереднього значення, а синхросигнал подається паралельно на всі тригери. Час підготовки tП – це час, який необхідно враховувати як час розповсюдження сигналу через допоміжні логічні елементи, і він завжди має величину, значно меншу, ніж час перемикання одиночного тригера. Тому швидкодія подібного типу лічильників має бути значно більшою, ніж швидкодія лічильників з послідовним переносом. Лічильники такого типу називаються лічильниками з паралельним переносом.

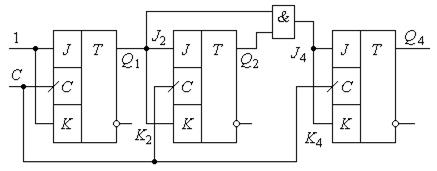

Виходячи з цього, розглянемо синтез синхронного лічильника з паралельним переносом з використанням JK-тригерів, який забезпечить коефіцієнт M = 8.

Таблиця станів лічильника, а також сигнали управління J та K входів тригерів приведені у табл. 8.2 (умовним позначенням * зображений байдужий стан відповідного входу).

Таблиця 8.2.

| Cn | Q4n | Q2n | Q1n | Q4(n+1) | Q2(n+1) | Q1(n+1) | J4 | K4 | J2 | K2 | J1 | K1 |

| * | * | * | ||||||||||

| * | * | * | ||||||||||

| * | * | * | ||||||||||

| * | * | * | ||||||||||

| * | * | * | ||||||||||

| * | * | * | ||||||||||

| * | * | * | ||||||||||

| * | * | * |

Рис.8.9.

Використовуючи карти Карно для входів J4 , K4 , J2 , K2 , J1 , K1 (рис. 8.9), знаходимо вирази для сигналів їх збудження. Відповідно, схема лічильника приведена на рис. 8.10.

Рис.8.10.

Узагальнюючи отриманий результат, можна стверджувати, що, якщо для лічильника з M = 2:

J1 = 1; K1 = 1;

для лічильника з M = 4:

J2 = Q1 ; K2 = Q1 ;

для лічильника з M = 8:

J4 = Q1 Q2 = J2 Q2 ; K4 = Q1 Q2 = K2 Q2 ;

то для лічильника з M = 16 матимемо:

J8 = Q1 Q2 Q4 = J4 Q4 ; K8 = Q1 Q2 Q4 = K4 Q4 .

Відповідно, для лічильника з M = N :

JN = Q1 Q2 …Q(N – 1) = J(N – 1) Q(N – 1) ; KN = Q1 Q2 …Q(N – 1) = K(N – 1) Q(N – 1) .

Для синхронних лічильників зворотного рахунку (віднімаючих) аналогічно можемо записати:

За аналогією з асинхронними лічильниками, з використанням допоміжної логіки синхронні лічильники можуть бути реверсивними.

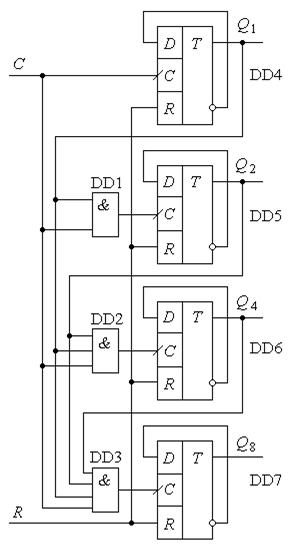

Прикладом лічильника з паралельним переносом є мікросхема КМОН К1561ИЕ10, спрощена схема якої приведена на рис. 8.11.

Рис.8.11.

Лічильник виготовлений на D-тригерах DD4…DD7, які працюють у режимі Т-тригерів. Допоміжна логіка DD1…DD3 забезпечує швидкий доступ послідовності імпульсів, що підраховуються, до синхровходу. При подачі сигналу високого рівня на R-вхід усі прямі виходи тригерів Q1 , Q2 , Q4 , Q8 встановлюються у нульовий стан. За зрізом першого тактового сигналу вихід Q1 тригера DD4 встановлюється в “1” і цим підготовлює доступ синхросигналу до синхровходу тригера DD5. Другий імпульс своїм зрізом встановить тригер DD4 у початковий стан, а DD5 – в “1”.

Цей процес триватиме доти, поки всі тригери не будуть встановлені у стан, при якому Q1 = Q2 = Q4 = Q8 = 1. Наступний за цим (шістнадцятий) синхроімпульс встановить всі тригери в нуль, і цикл закінчиться.

Як випливає з роботи лічильника, всі тригери сприймають імпульси вхідної послідовності практично одночасно, аналогічно відбувається зміна їх станів, що забезпечує високу швидкодію лічильника. Фактично вона визначається часом перемикання тригера і незначною, порівняно з ним, затримкою вхідної логіки.

З аналізу роботи лічильника бачимо, що перемикання кожного наступного тригера при приході чергового імпульсу має місце лише тоді, коли всі попередні тригери встановлені в “1”. Математично це можна виразити наступною формулою:

, (8.6)

, (8.6)

де Qin – стан i-го тригера до подачі імпульсу; pi = Q0n ∙ Q1n ∙ … ∙ Q(i – 1)n – узагальнений сигнал перенесення.

У розглянутих лічильниках, на відміну від пристроїв з послідовним перенесенням, напрямок рахунку не залежить від типу динамічного входу тригера, а визначається виключно тим, який з виходів тригера (прямий чи інверсний) використовується для формування сигналу перенесення. Оскільки ми впевнились, що лічильник, схема якого приведена на рис. 8.11, є додаючим, то при використанні інверсних виходів тригерів отримаємо лічильник віднімаючий. Таким чином алгоритм перемикання в реверсивних лічильниках (додавання/віднімання) залишається незмінним.

Недоліки лічильників з паралельним перенесенням полягають, перш за все, у критичності до тривалості вхідних імпульсів та їх фронтів. Тому при використанні таких пристроїв слід звертати увагу на довідкові дані по цим параметрам. Обумовлено це тим, що, незважаючи на те, що тригери лічильника перемикаються майже одночасно і час установки двійкового коду tКУ на виході лічильника фактично визначається часом установки тригера tT , але для підготовки до наступного перемикання необхідно, щоб пройшов деякий час, який називається часом підготовки tП . За цей час послідовно формуються сигнали перенесення на всіх входах елементів І. Величина tП залежить від встановленого в попередньому такті коду.

Складність практичної реалізації лічильника з великим значенням модуля М є другим їх недоліком. Це обумовлено ускладненням логіки переносу з великою кількістю входів.

Задача нарощування лічильників розв’язується декількома шляхами. Наприклад, у мікросхемі К1561ИЕ10 синхровхід запаралелюється через елемент АБО допоміжним інверсним входом  . Цей вхід дає можливість організувати рахунок як за фронтом імпульсу, так і за зрізом, а при послідовному нарощуванні використовується як вхід асинхронного вводу від виходу Q8 попереднього лічильника. Такий спосіб нарощування називається комбінованим (послідовно-паралельним).

. Цей вхід дає можливість організувати рахунок як за фронтом імпульсу, так і за зрізом, а при послідовному нарощуванні використовується як вхід асинхронного вводу від виходу Q8 попереднього лічильника. Такий спосіб нарощування називається комбінованим (послідовно-паралельним).

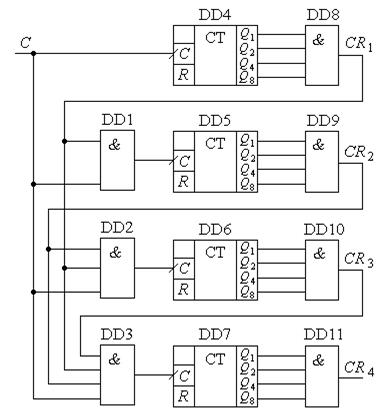

Рис.8.12.

На практиці часто використовуються структури з комбінованим паралельно-паралельним перенесенням. Особливість такого перенесення ілюструється рис. 8.12. За аналогією зі схемою рис. 8.11, логічні елементи DD1…DD3 забезпечують паралельне перенесення від лічильників DD4…DD7. Формування сигналів перенесення CR1…CR4 з кожного лічильника виконують логічні елементи DD8…DD11 при умові, що виходи Q1…Q8 кожного з лічильників встановлені в “1”. У такій структурі лічильника швидкодія визначається часом установки коду tКУ . Ця величина практично визначається часом установки коду в межах одного лічильника. Час підготовки tП max у лічильнику визначається сумою затримок у логічних елементах І. Тому максимальна частота перемикання визначатиметься як:

. (8.7)

. (8.7)

Дата добавления: 2016-09-26; просмотров: 3497;