Совершенствование структурной и логической организации ЭВМ

Это направление совершенствования однопроцессорных ЭВМ традиционной архитектуры фон Неймана предусматривает повышения производительности ЭВМ за счет:

· повышения информационной емкости обрабатываемых данных;

· применения сопроцессоров;

· использование кэш-памяти.

· создание RISC-процессоров;

· реализация конвейеризации и параллелизма.

Повышение информационной емкости обрабатываемых данных достигается за счет:

· повышения разрядности системной шины и процессора, разделения единой шины данных и программ на две (количественная составляющая);

· использование элементов, в которых реализована не двоичная система счисления, а троичная и т. д. (качественная составляющая).

Увеличение скорости обработки данных и пропускной способности системной шины путем увеличения числа параллельно передаваемых по шине бит, требует увеличения разрядности системной шины и процессоров. Разрядность системной шины процессоров сначала была увеличена с 8 до 16, а затем до 32 и 64 бит, и далее до 128 бит. В настоящее время создание 128 разрядных процессоров и системной шины не является пределом.

Использование процессоров и системной шины с повышенной разрядностью приводит к возможности распараллеливания однотипных операций по обработке данных, что в свою очередь, приводит к повышению производительности компьютера. То, что выполнялось за два и более тактов, можно выполнить за один такт.

Однако на пути повышения разрядности системной шины и процессора лежат конструктивные факторы, в этом случае не удается получить компактные элементы, возникают проблемы, связанные с огромным числом внутрисхемных соединений, разводки контактов и монтажа микросхем.

Другое решение проблемы состоит в эффективном использовании линий передачи информации в кристалле. Это достигается, например, за счет применения многозначных (m-значных) элементов, позволяющих обрабатывать сигналы, имеющие m устойчивых состояний. Использование полупроводниковой технологии при создании многозначных элементов, принимающих несколько состояний, носит несколько искусственный характер и эффективно лишь по некоторым критериям. Специалисты считают, что использование многозначных элементов будет востребовано в компьютерах, созданных с учетом нейро- и биотехнологий.

Сегодня на рынок активно продвигаются двуядерные процессоры. Двуядерные процессоры появились в конце 2005 года и совместимы с существующими платами. Кроме того, они совместимы по инфраструктуре с одноядерными предшественниками. Для более простого понимания представим, например, что если на двухпроцессорных серверах и рабочих станциях, установить по два двуядерных процессора в старые системы, то можно получить четырехпроцессорную систему по цене двухпроцессорной.

Применение сопроцессоров. Процессоры с фиксированной системой команд из конструктивных и технологических соображений содержат минимально необходимый набор команд. В этих процессорах многие функции реализуются программно с помощью численных методов. К таким функциям, например, относят тригонометрические и экспоненциальные функции, операции умножения и деления чисел с плавающей запятой, операции преобразования матриц.

Переход к аппаратной реализации вычислительных процессов позволяет существенно повысить скорость обработки информации за счет вычисления на аппаратном, а не микропрограммном уровне и упрощает программное обеспечение.

При проектировании сопроцессоров необходимо определить приемлемый баланс между жесткой специализацией на определенный алгоритм (класс алгоритмов) и возможностью реализации различных алгоритмов. Специализированные устройства позволяют достичь максимальной производительности при решении задачи, на которую они ориентированы, однако стоимость их разработки удовлетворяет сравнительно узкий круг потребителей, что не является экономически эффективным.

Построение сопроцессора, выполняющего узкий класс алгоритмов, целесообразно в случае, если выполняется одно из условий.

· производительность сопроцессора играет решающую роль, важность выполняемых задач позволяет пренебречь его стоимостью.

· Сопроцессор, несмотря на его узкую специализацию, будет использован в больших количествах.

· стоимость разработки и изготовления мала – это возможно для сопроцессоров, состоящих из небольшого числа типов простых ячеек и при наличии системы автоматизированного проектирования и технологичностью производства.

Кэш-память(Cache -тайник, тайный склад). Значительное влияние на производительность вычислительных систем фон-неймановской архитектуры оказывают время доступа к памяти и ее пропускная способность (скорость пересылки, достигаемая при обмене информацией). Кэш-память, представляющая собой быстродействующее запоминающее устройство, размещенное на одном кристалле с процессором. Эта память служит высокоскоростным буфером между процессором и относительно медленной основной памятью. При обращениях к памяти соответствующие значения предварительно помещаются в кэш. При последующих операциях чтения/записи обращения происходит в основном к кэш-памяти и время на простой процессора не затрачивается.

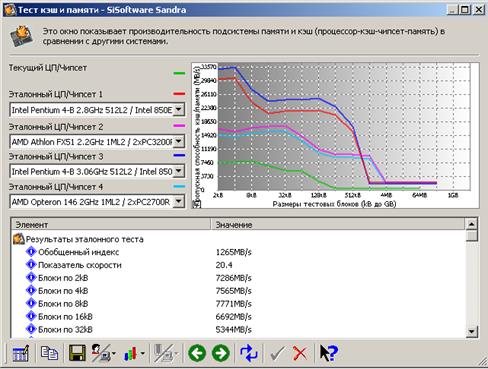

Производительность кэш-памяти определяется временем доступа к ней и вероятностью удачных обращений. Эта вероятность зависит от объема кэш памяти. С увеличением его размера повышается вероятность того, что следующее обращение будет удачным, т.е. необходимая информация окажется в кэш памяти. Однако, необходимо учитывать, тот факт, что с ростом объема блоков обрабатываемой информации, производительность компьютеров с различной частотой процессоров и объемами кэш памяти, становится сопоставимой. Это находит отражение в результатах тестирования производительности компьютеров с различными чип сетами, например, с помощью информационной и диагностической утилиты SiSoftware Sandra, которые отображены на рисунке ниже.

Рис. Производительность подсистемы памяти и кэш (процессор-кэш-чипсет-память) в сравнении с другими системами.

Кстати, о строении двуядерных процессоров не используется общий кэш второго уровня. На практике гораздо проще разместить на кристалле два ядра с независимыми блоками кэш-памяти. Системой такой процессор будет абсолютно прозрачно восприниматься, как два физических процессора. Каждое ядро будет обращаться к своему эксклюзивному кэшу.

Использование RISC-процессоров.Распространенная на начальном этапе развития ЭВМ архитектура CISC (Complex Instruction Set Computers) ориентирована на избыточные набор команд и способы адресации. Избыточность набора команд ЭВМ – не единственный путь совершенствования фон-неймановской архитектуры процессоров. Альтернативой ему является упрощение набора команд. Этот путь заключается в упрощении, а не в усложнении, как было принято ранее, архитектуры процессоров, что позволяет снизить сложность и стоимость их разработки. В результате оказывается возможным отказаться от микропрограммного принципа управления процессором в пользу аппаратного. Созданные архитектуры получили название RISC-архитектур (Reduced Instruction Set Computer) – архитектур ЭВМ с упрощенной системой команд.

Выбор между RISC и CISC архитектурами зависит от области применения процессоров. RISC-процессоры удобны при использовании их в качестве элементарных процессорных устройств с высокой степенью распараллеливания операций, а CISC-процессоры эффективны в тех областях, где требуется поддержка аппаратными средствами высоконадежного программного обеспечения. Для обеспечения превосходства RISC-процессоров над CISC необходимо создать большое количество программ, специально ориентированных на реализацию RISC-процессоров.

Масштабируемая процессорная архитектура SPARC (Scalable Processor Architecture) компании Sun Microsystems является наиболее широко распространенной RISC-архитектурой. Процессоры с архитектурой SPARC лицензированы и изготавливаются по спецификациям Sun несколькими производителями, среди которых следует отметить компании Texas Instruments, Fujitsu, LSI Logic, Bipolar International Technology, Philips, Cypress Semiconductor и Ross Technologies. Эти компании осуществляют поставки процессоров SPARC не только самой Sun Microsystems, но и другим известным производителям вычислительных систем, например, Solbourne, Toshiba, Matsushita, Tatung и Cray Research.

Конвейеризация и параллелизм. Эти методы являются одними из наиболее эффективных для разработки архитектур с повышенными технико-экономическими возможностями. Их применение возможно для однопроцессорных и многопроцессорных ЭВМ. Когда мы говорили о повышении производительности компьютера за счет использования процессорах и системных шин с повышенной разрядностью, а также двуядерных процессорах, то именно конвейеризация и параллелизм позволяют решить эту задачу.

Процесс конвейеризация предусматривает разбиение команды в процессоре на элементарные операции. Для выполнения операций каждого типа используются специализированные исполнительные устройства. Принцип конвейеризации заключается в том, что во время выполнения команды с упреждением производится выборка из памяти очередной команды. Тем самым сокращается длительность цикла выполнения команды.

Другой путь повышения производительности числовой обработки заключается в расширении типового набора команд векторными командами. Эти команды предусматривают выполнение единой операции над несколькими данными, хранящимися в соответствующих векторных регистрах. Особенно эффективны векторные операции при организации циклических процессов.

Дата добавления: 2020-10-25; просмотров: 583;