Характеристики микропроцессоров фирмы Intel

| Наименование МП | Тактовая частота, Мгц | Индекс iCOMP | Разрядность ШД (внутренняя/ внешняя) | Адресуемая память/ разрядность ША | Сопроцессор | Снижение потребления энергии | Примечание |

| 16/16 | 1 Мб/20 | 40000 транз | |||||

| 16/8 | l Мб/20 | ||||||

| 16/16 | 16 Мб/24 | 130000 трата | |||||

| 80386SL | 16/16 | 16 Мб/24 | Есть | ||||

| 80386SX | 32/32 | 16 Мб/24 | |||||

| 80386DX | 32/32 | 4 Г6/32 | |||||

| 80486SL | 32/32 . | 4 Г6/32 | Нет | Есть | |||

| 80486SX | 32/32 | 4 Г6/32 | Нет | ||||

| 80486SX2 | - | 32/32 | 4 Г6/32 | ||||

| 80486SX2 | 32/32 | 4 Г6/32 | |||||

| 80486DX | 32/32 | 4 Г6/32 | Встр. | ||||

| 80486DX2 | 32/32 | 4 Г6/32 | Встр. | 1,2 млн транз. | |||

| 80486DX2 | 32/32 | 4 Г6/32 | Встр. | ||||

| 80486DX4 | 32/32 | 4 Г6/32 | Встр. | ||||

| 80486DX4 | 32/32 | 4 Г6/32 | Встр. | ||||

| Over Drive | 32/32 | 4 Г6/32 | Встр. | Аналог 486DX2 | |||

| Pentium | 64,32/64 | 4 Г6/32 | Встр. | 6,7 млн транз. | |||

| Pentium | 64,32/64 | 4 Г6/32 | Встр. | ||||

| Pentium | 64,32/64 | 4 Г6/32 | Встр. | ||||

| Pentium | 64,32/64 | 4 Г6/32 | Встр. | ||||

| Pentium | - | 64,32/64 | 4 Г6/32 | Встр. | |||

| Pentium | 64,32/64 | 4 Г6/32 | Встр. | ||||

| Pentium Pro | о 150 | ||||||

| Pentium Pro | о 200 |

В персональных ЭВМ нашли применение не только микропроцессоры фирмы Intel. Крупнейшими производителями аналогов микропроцессорам Intel (клонов) являются фирмы Cyrix и AMD.

Фирма Cyrix выпускает микропроцессоры М-1 и М-2, аналогичные Pentium, но превосходящие его по производительности. Так, М-1 с тактовой частотой 150 МГц по производительности эквивалентен МП Pentium с тактовой частотой 200 МГц.

Фирма AMD, завоевавшая около 30% рынка МП в России, выпускает микропроцессоры К-5 и К-6, являющиеся соответственно аналогами Pentium и Pentium Pro.

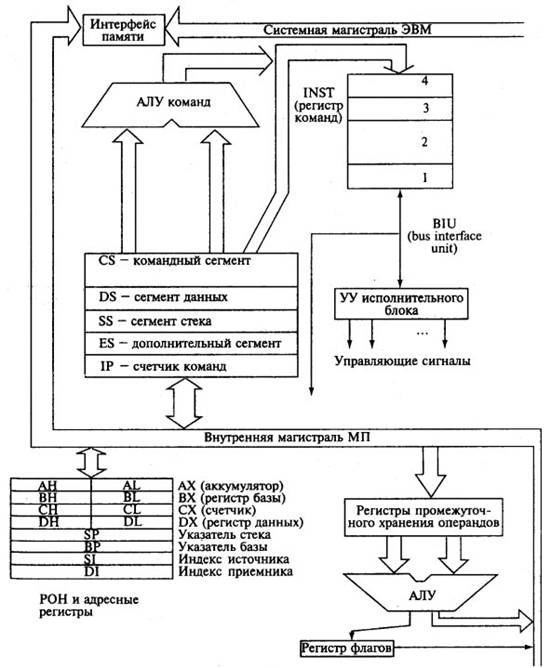

Структурная схема базовой модели МП фирмы Intel приведена на рис.5.5.

[an error occurred while processing this directive]

Рис.5.5. Структурная схема микропроцессора

Условно микропроцессор можно разделить на две части: исполнительный блок (Execution Unit - EU) и устройство сопряжения с системной магистралью (Bus Interface Unit - ВШ).

В исполнительном блоке находятся: арифметический блок и регистры общего назначения (РОН). Арифметический блок включает арифметико-логическое устройство, вспомогательные регистры для хранения операндов и регистр флагов.

Восемь регистров исполнительного блока МП (АХ, ВХ, СХ, DX, SP, ВР, SI, DI), имеющих длину, равную машинному слову, делятся на две группы. Первую группу составляют регистры общего назначения: АХ, ВХ, СХ и DX, каждый из которых представляет собой регистровую пару, составленную из двух регистров длиной в 0.5 машинного слова: аккумулятор, или регистр АХ состоит из регистров АН и AL. Регистр базы (Base Register) ВХ состоит из регистров ВН и BL. Счетчик (Count Register) СХ включает регистры СН и CL. Регистр данных (Data Register) DX содержит регистры DH и DL. Каждый из коротких регистров может использоваться самостоятельно или в составе регистровой пары. Условные названия (аккумулятор, регистр базы, счетчик, регистр данных) не ограничивают применения этих регистров - эти названия говорят о наиболее частом использовании их или об особенности использования того или иного регистра в той иди иной команде.

Вторую группу составляют адресные регистры SP, BP, SI и DI (в старших моделях количество адресных регистров увеличено). Эти регистры активно используются по функциональному назначению и в других целях их применятъ не рекомендуется. В качестве адресного регистра часто используется РОН ВХ. Программно допускается использование регистров BP, DI и SI в качестве регистров для хранения операндов, но отдельные байты в этих регистрах недоступны. Основное их назначение - хранить числовые значения, реализуемые при формировании адресов операндов.

Устройство сопряжения с системной магистралью содержит управляющие регистры, конвейер команд, АЛУ команд, устройство управления исполнительным блоком МП и интерфейс памяти (соединяющий внутреннюю магистраль МП с системной магистралью ПЭВМ).

Управляющие регистры BIU: CS (указатель командного сегмента), DS указатель сегмента данных), SS (указатель сегмента стека), ES (указатель дополнительного сегмента) и др. служат для определения физических адресов ОП - операндов и команд. Регистр IP (Instruction Pointer) является указателем адреса команды, которая будет выбираться в конвейер команд в качестве очередной команды (в отечественной литературе такое устройство называется счетчик команд).Конвейер команд МП хранит несколько команд, что позволяет при выполнении линейных программ совместить подготовку очередной команды с выполнением текущей.

К управляющим регистрам МП относится и регистр флагов, каждый разряд которого имеет строго определенное назначение. Обычно разряды регистра флагов устанавливаются аппаратно при выполнении очередной операции в зависимости от получаемого в АЛУ результата. При этом фиксируются такие свойства получаемого результата, как нулевой результат, отрицательное число, переполнение разрядной сетки АЛУ и т.д. Но некоторые разряды регистра флагов могут устанавливаться по специальным командам. Некоторые разряды имеют чисто служебное назначение (например, хранят разряд, (выпавший” из АЛУ во время сдвига) или являются резервными (т.е. не используются).

Все флаги младшего байта регистра устанавливаются арифметическими или логическими операциями МП. Все флаги старших байтов, за исключением флага переполнения, устанавливаются программным путем, для этого в МП имеются команды установки флагов (STC, STD, STI), сброса (CLC CLD, CLI), инвертирования (CMC).

ICH — контроллер-концентратор ввода-вывода — южный мост (southbridge) — обеспечивает взаимодействие между ЦП и жестким диском, картами PCI, интерфейсами IDE, SATA, USB и пр. Также иногда к чипсетам относят микросхему Super I/O, которая подключается к южному мосту и отвечает за низкоскоростные порты RS232, LPT, PS/2.

5) Системы команд МП

Систему команд, реализуемую МП, принято разделять на группы команд в соответствии с их функциональным назначением. По этому признаку выделяют пять групп команд: 1) пересылки информации, 2) арифметических операций; 3) логических операций; 4) ветвления; 5) управления.

Группу команд пересылки информации образуют команды организации двустороннего обмена между внешней памятью и блоком РОН или между различными регистрами блока РОН.

Группа команд арифметических операций выполняет такие операции, как суммирование — ADD, вычитание — SUBTRACT, добавление единицы — INCREMENT или вычитание единицы —DECREMENT. эта группа команд адресует только один из операндов, иторой операнд хранится в аккумуляторе. Результат выполнения операции фиксируется в аккумуляторе.

Группа команд логических операций содержит команды, реализующие операции И (AND), ИЛИ (OR), исключающее ИЛИ (EXCLUSIVE OR), и также сравнение (COMPARE) над данными. Так же кик команды арифметических операций, эти команды адресуют только один из операндов, второй операнд всегда находится в аккумуляторе. Результат операции образуется в аккумуляторе.

Группа команд ветвления образуется набором условных и безусловных команд перехода JUMP и JUMP IF, команд вызова подпрограмм CALL и команд возврата RETURN. Группа команд JUMP IF используется тогда, когда по результату выполнения некоторой операции выбирается направление дальнейших вычислений.

Команды CALL и RETURN служат для организации связи основной программы с подпрограммами, т. е. для входа в подпрограмму и последующего возврата к основной программе. В МП-системах и микро-ЭВМ команды «той группы получили широкое применение, так как по Подпрограммам выполняются как арифметические операции типа умножения, деления, вычисления некоторых функций, так и операции ввода-вывода.

Группу команд управления образуют команды, управляющие процедурами ввода-вывода информации, операциями со стеком, и команды проверки текущего состояния процессора. В этой группе команд наибольшую сложность представляют вопросы использования команд ввода-вывода информации. Организация системных пересылок является наиболее трудной частью работы разработчика и программиста МП-системы. Она требует детального знания как методов программирования, так и внутренней логической организации МП, интерфейса системы и достаточно сложных алгоритмов управления адаптерами периферийных устройств.

6) Взаимодействие элементов при работе микропроцессора

Работой МП управляет программа, записанная в ОП ЭВМ. Адрес очередной команды хранится в счетчике команд IP (Instruction Pointer) и в одном из сегментных регистров, чаще всего в CS. Каждый из них в реальном режиме имеет длину 16 бит, тогда как физический адрес ОП должен иметь длину 20 бит. Несогласованность длины машинного слова (16 бит) и длины физического адреса ОП (20 бит) приводит к тому, что в командах невозможно указать физический адрес ОП - его приходится формировать, собирать из разных регистров МП в процессе работы.

В реальном режиме вся ОП делится на сегменты (длина сегмента - 64 Кбайта). Адрес ОП разделяется на две части: номер сегмента в ОП (база сегмента) и номер ячейки внутри данного сегмента (смещение относительно начала сегмента). Базовый адрес сегмента образуется добавлением к номеру сегмента справа четырех нулей. Поскольку последние четыре разряда абсолютного (физического) адреса сегмента всегда нулевые, сегмент может начинаться не с любой ячейки ОП, а только с “параграфа” - начала 16-байтного блока ОП. В структуре микропроцессора имеется несколько регистров сегментов, например в i8086 - четыре:

С S - программный сегмент;

DS - сегмент данных (информационный сегмент);

SS - стековый сегмент;

ES - расширенный сегмент (дополнительный сегмент данных).

Номер ячейки внутри сегмента (смещение) называется также исполнительным адресом. В большинстве случаев в адресной части команды указывается именно исполнительный адрес - номер сегмента чаще всего подразумевается по умолчанию. Однако допускается указание и полного адреса ОП в виде префиксной структуры: “сегмент: смещение”. Если сегмент в команде не указывается, значит, работа ведется внутри текущего сегмента (характер выполняемой работы и какой из сегментных регистров определяет текущую базу сегмента, зависят от вида выполняемой команды).

Номер сегмента так же, как и смещение, имеет длину 2 байта. При вычислении физического адреса ОП сегмент и смещение суммируются, но сегмент перед суммированием сдвигается влево на 4 бита. В результате суммирования образуется физический адрес ОП длиной 20 бит.

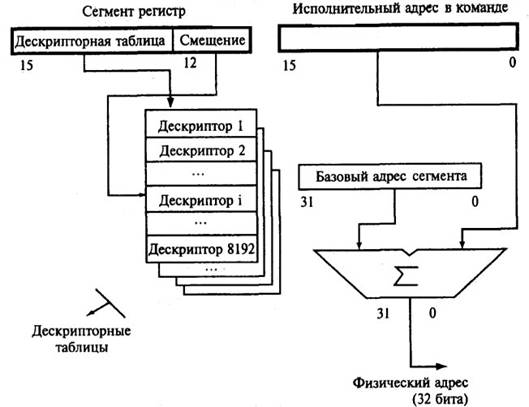

В защищенном режиме базовые адреса сегментов хранятся в дескрипторных таблицах и имеют длину 24 или 32 бита (в зависимости от типа МП). В сегментных же регистрах хранится селектор, содержащий номер дескрипторной таблицы и дескрипторное смещение, т.е. порядковый номер дескриптора (в котором и хранится базовый адрес сегмента) в данной дескрипторной таблице (рис.5.6).

Рис. 5.6. Формирование физического адреса ОП в защищенном режиме

Физический адрес очередной команды через внутреннюю магистраль МП и интерфейс памяти поступает на шину адреса системной магистрали. Одновременно из устройства управления (УУ) исполнительного блока на шину управления выдается команда (управляющий сигнал) в ОП, предписывающая выбрать число, находящееся по адресу, указанному в системной магистрали. Выбранное число, являющееся очередной командой, поступает из ОП через шину данных системной магистрали, интерфейс памяти, внутреннюю магистраль МП на регистр команд (INST).

Из команды в регистре команд выделяется код операции, который поступает в УУ исполнительного блока для выработки управляющих сигналов, настраивающих микропроцессор на выполнение требуемой операции.

В зависимости от используемого в команде режима адресации организуется выборка необходимых исходных данных.

Триггеры некоторых типов используют значения выходного сигнала для формирования управляющих сигналов на входах запоминающей ячейки. Это может привести к непредсказуемой последовательности его переключений. При построении отдельных схем на основе триггеров, например, регистров сдвига, необходимо, чтобы значения выходных сигналов триггера не изменялись на то время, пока производится их запись и значения его выходных сигналов в другой триггер, но сам этот триггер должен воспринимать значения с выхода некоторой другой триггерной схемы.

7) Существует шесть типов исключительных ситуаций FPU:

недействительная операция (#I)

стековые операции (#IS)

арифметические операции (#IA)

денормализованный операнд (#D)

деление на нуль (#Z)

переполнение (#O)

антипереполнение (#U)

неточный результат (#P)

Каждому исключению соответствует флаг индикации в регистре состояния FPU (SW) и бит маски в регистре управления FPU (CW). Биты маски используются для разрешения/запрещения соответствующих исключений, а флаги для их индикации.

При возникновении исключения, когда соответствующий бит маски сброшен, устанавливается соответствующий флаг в регистре состояния и выдается сигнал, сообщающий процессору об ошибке сопроцессора. В случае, когда бит маски исключения установлен, внешний сигнал не выдается, но флаг все равно устанавливается. Таким образом, используя эффект накопления ошибок, программное обеспечение может замаскировать все исключения до выполнения вычислений, затем произвести вычисления и проверить содержимое всех флагов для выяснения того, какие исключения произошли во время вычислений. Помимо этого, в режиме замаскированных исключений одна команда FPU может вызвать сразу несколько исключений и, соответственно, установку сразу нескольких флагов (после встречи первого исключения выполнение команды продолжается и могут возникнуть другие исключения). Демаскирование исключений изменяет режим реагирования FPU — начинают выдаваться специальные сигналы при возникновении исключений.

В современных процессорах (Intel286 …) предусмотрено два механизма сообщения процессору о возникновении исключения FPU.

Первый механизм использует специальную особую ситуацию #MF (Ошибка сопроцессора), которая генерируется автоматически при поступлении команды FPU/MMX/3DNow!, следующей за командой, вызвавшей ошибку. В процессорах Intel486 … это достигается внутренними средствами, а в Intel286, Intel386 при подаче сигнала от сопроцессора на соответствующий вход процессора (ERROR#).

Второй механизм работает в т.н. стиле MS-DOS. В этом случае ошибки сопроцессора обнаруживаются через внешнее прерывание, которое генерируется аппаратурой по сигналу от сопроцессора. Такой стиль поддерживается всеми процессорам архитектуры x86 для совместимости с программным и аппаратным обеспечением компьютеров PC XT, AT.

В процессорах с интегрированным FPU (Intel486 …) предусмотрен внутренний механизм выбора режима сообщения об ошибках FPU. Этот механизм управляется битом CR0.NE . Если NE установлен, действует внутренний механизм, обеспечивающий генерацию ошибки сопроцессора #MF сразу по поступлении очередной команды FPU/MMX/3DNow! вслед за командой, вызвавшей незамаскированное исключение (с помощью регистре управления сопроцессора CW можно замаскировать все исключения).

Если NE сброшен, реакция на исключительния FPU происходит в стиле MS-DOS. В этом режиме задействуются специальные выводы FERR# и IGNNE# (вывод FERR# аналогичен выводу ERROR# сопроцессоров Intel287 и Intel387 и обычно подключается к внешнему программируемому контроллеру прерываний).

Протокол реакции на исключения FPU имеет некоторые отличия в различных моделях процессоров и сопроцессоров. Отличия эти касаются в первую очередь режима реакции в стиле MS-DOS и момента генерации ошибки сопроцессора (сразу по возникновении или при поступлении следующей команды FPU/MMX/3DNow!). В современных микропроцессорах наиболее универсальным и жестко регламентированным является режим внутренней генерации ошибки сопроцессора (CR0.NE = 1), который является основным, режим реакции в стиле MS-DOS поддерживается для совместимости. Подробное описание механизма реакции на исключения сопроцессора приведено в Intel® 64 and IA-32 Architectures Software Developer’s Manual. Volume 1: Basic Architecture.

Первопричиной генерации исключения сопроцессора могут быть только команды FPU.Команды MMX и 3DNow!, хотя и изменяют содержимое некоторых регистров, но не оказывают влияния на состояние FPU. Для индикации SIMD-исключений используется другой механизм, основанный на новых регистрах.

Скалярный процессор — это простейший класс микропроцессоров. [1] Скалярный процессор обрабатывает один элемент данных за одну инструкцию (SISD, Single Instruction Single Data), типичными элементами данных могут быть целые или числа с плавающей запятой. В векторных процессорах (SIMD, Single Instruction Multiple Data), в отличие от скалярных, одна инструкция работает с несколькими элементами данных.

Дата добавления: 2016-05-30; просмотров: 4002;