Описание внутренних регистров ПДП

Контроллер имеет 344 бита внутренней памяти, организованной в виде регистров. Первые пять регистров имеются в каждом из 4-х каналов.

Регистр начального адреса (Base Address Register). В этом регистре задается стартовый адрес ОЗУ, с которого начинается передача. Регистр содержит 16 разрядов и определяет адрес внутри заданной страницы памяти размером 64К.

Регистр начального счетчика циклов (Base Word Count Register). В этом регистре задается начальное число циклов передачи для программируемого канала. Фактическое число передаваемых во время работы ПДП элементов данных на единицу превышает заданное число циклов.

Регистр текущего адреса (Current Address Register). Начальное значение заносится в этот регистр одновременно с регистром начального адреса. В дальнейшем в ходе передачи значение текущего адреса автоматически увеличивается или уменьшается (конкретное направление изменения задается при программировании в регистре режима). Если разрешена автоинициализация, то после окончания передачи в регистр автоматически устанавливается значение из регистра начального адреса.

Регистр текущего счетчика циклов (Current Word Count Register). Регистр содержит текущее значение счетчика циклов (число оставшихся циклов передачи). Отображаемое в нем число циклов всегда на единицу меньше числа еще не переданных элементов данных, так как изменение значения в этом регистре проиводится в конце цикла передачи, уже после фактической передачи элемента данных, а конец передачи фиксируется в момент переполнения счетчика (изменение его значения с 0 на 0FFFFh).

Регистр режима (Mode Register). Данный регистр задает режимы работы своего канала контроллера (используются 5 младших разрядов):

разряды 0-1: 00=проверка,

01=запись (в память),

10=чтение (из памяти)

11=недопустимая комбинация

разряд 2: 1- автоинициализация разрешена

0- автоинициализация запрещена

разряд 3: 0=увеличение текущего адреса при обмене

1=уменьшение текущего адреса при обме

разряды 4-5: 00=режим передачи по требованию

01=режим одиночной передачи

10=режим блочной передачи

11=каскадный режим.

Следующий набор регистров является общим для всех каналов.

Регистр команд (Command Register). Этот 8-битный регистр управляет работой контроллера. Он программируется, когда контроллер находится в состоянии программирования и очищается командами сброса "Reset" и "Master Clear". Назначение битов регистра команд:

разряд 0: 0=запретить передачу память-память, 1=разрешить

1: 0=запретить фиксацию адреса в канале 0, 1=разрешить

2: 0=разблокировать, 1=заблокировать контроллер

3: 0=нормальная временная диаграмма, 1=сжатие времени

4: 0=фиксированные приоритеты, 1=циклический сдвиг

5: 1=режим расширенной записи, 0=задержки при записи

6: 0=активным считается высокий уровень DREQ, 1=низкий

7: 0= активным считается высокий уровень DACK, 1=низкий

Регистр состояния (Status Register). Регистр отражает текущее состояние запросов и передач по всем четырем каналам. Биты 0 - 3 устанавливаются в единицу после завершения передачи по каналам 0 - 3 (бит 0 - канал 0, бит 1 - канал 1 и т.д.), если не задан режим автоинициализации. Эти биты очищаются после команды сброса контроллера и после каждой операции считывания состояния из регистра состояния. Биты 4 – 7 указывают по какому из каналов 0 - 3 активен в текущий момент сигнал запроса на ПДП.

Регистр масок (Mask Register). Каждый бит этого 4-битового регистра маскирует/демаскирует свой канал ПДП, при этом значение 1 маскирует канал, значение 0 демаскирует канал и разрешает прием сигнала запроса по этому каналу.

Регистр запросов (Request Register). Сигнал запроса на ПДП (DREQ) может быть издан как обслуживаемым устройством, так и программно. Для программного издания сигнала запроса по одному из 4-х каналов ПДП необходимо установить соответствующий бит в 4-разрядном регистре запросов. Запрос на ПДП может быть отменен записью нулевого значения в соответствующий бит регистра. Бит запроса очищается автоматически при окончании передачи по данному каналу. Все биты запросов очищаются при сбросе контроллера. Для того, чтобы воспринимать программные запросы на ПДП, канал должен находится в режиме блоковой передачи.

Рабочий регистр (Temporary Register). Этот 8-разрядный регистр используется для хранения элемента данных, передаваемого в режиме фиксированного адреса при передаче память-память или для временного хранения передаваемого байта при всех остальных режимах передачи.

Системный таймер

Все ВМ используют программируемый системный таймер (ПСТ), выполняющий три основных функции:

§ генерацию прерываний от системных часов, вызывающих инкремент счетчика системного времени в ячейке 0000:046Ch - счетчик тиков таймера (области данных BIOS);

§ генерацию запросов на регенерацию памяти;

§ генерацию звуковых сигналов.

При инициализации BIOS устанавливает свой обработчик для прерывания таймера. Этот обработчик каждый раз увеличивает на 1 текущее значение четырехбайтовой переменной - счетчик тиков таймера. Если этот счетчик переполняется (прошло более 24 часов с момента запуска таймера), в ячейку 0000:0470h заносится 1.

Другое действие, выполняемое стандартным обработчиком прерывания таймера - контроль за работой двигателей НГМД. Если после последнего обращения к НГМД прошло более 2 секунд, обработчик прерывания выключает двигатель. Ячейка с адресом 0000:0440h содержит время, оставшееся до выключения двигателя. Это время постоянно уменьшается обработчиком прерывания таймера. Когда оно становится равно 0, обработчик выключает двигатель НГМД.

Последнее действие, которое выполняет обработчик прерывания таймера - вызов прерывания INT 1Ch. После инициализации системы вектор INT 1Ch указывает на команду IRET, т.е. ничего не выполняется. Программа может установить собственный обработчик этого прерывания для того чтобы выполнять какие-либо периодические действия.

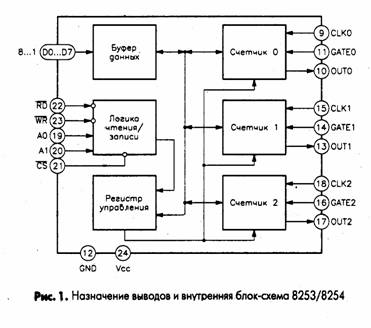

В качестве ПСТ ранее применялась микросхема Intel 8254, роль которой на современных системных платах берет на себя чипсет, сохраняя полную программную совместимость. ПСТ представляет собой трехканальные программируемые счетчики-таймеры (рис. 4.3) с независимыми входами CLK – вход счетных импульсов и GATE – вход разрешения счета и выходом OUT, изменяющим состояние по окончании счета.

|

Каждый канал (счетчик 0, 1, 2) содержит регистры:

· состояния канала RS (8 разрядов);

· управляющего слова RSW (8 разрядов);

· буферный регистр OL (16 разрядов);

· регистр счетчика CE (16 разрядов);

· регистр констант пересчета CR (16 разрядов).

Регистр счетчика CE работает в режиме вычитания. Его содержимое уменьшается по заднему фронту сигнала CLK при условии, что на вход GATE установлен уровень логической 1. В зависимости от режима работы таймера при достижении счетчиком CE нуля тем или иным образом изменяется выходной сигнал OUT.

Буферный регистр OL предназначен для запоминания текущего содержимого регистра счетчика CE без остановки процесса счета. После запоминания буферный регистр доступен программе для чтения.

Регистр констант пересчета CR может загружаться в регистр счетчика, если это требуется в текущем режиме работы таймера.

Регистр состояния канала RS и управляющего слова RSW предназначены, соответственно, для определения текущего состояния канала и для задания режима работы таймера.

Возможны шесть режимов работы таймера. Они разделяются на три типа:

- Режимы 0, 4 - однократное выполнение функций.

- Режимы 1, 5 - работа с перезапуском.

- Режимы 2, 3 - работа с автозагрузкой.

В режиме однократного выполнения функций перед началом счета содержимое регистра констант пересчета CR переписывается в регистр счетчика CE по сигналу CLK, если сигнал GATE установлен в 1. В дальнейшем содержимое регистра CE уменьшается по мере прихода импульсов CLK. Процесс счета можно приостановить, если подать на вход GATE уровень логического 0. Если затем на вход GATE подать 1, счет будет продолжен дальше. Для повторения выполнения функции необходима новая загрузка регистра CR, т.е. повторное программирование таймера.

При работе с перезапуском не требуется повторного программирования таймера для выполнения той же функции. По фронту сигнала GATE значение константы из регистра CR вновь переписывается в регистр CE, даже если текущая операция не была завершена.

В режиме автозагрузки регистр CR автоматически переписывается в регистр CE после завершения счета. Сигнал на выходе OUT появляется только при наличии на входе GATE уровня логической 1. Этот режим используется для создания программируемых импульсных генераторов и генераторов прямоугольных импульсов (меандра).

Программирование ПСТ осуществляется через порты ввода/вывода со следующими адресами:

· 40h - канал 0;

· 41h - канал 1;

· 42h - канал 2;

· 43h - управляющий регистр.

Формат управляющего регистра приведен на рис. 4.4.

Поле B определяет формат константы, использующейся для счета – (В=0) двоичный или (В=1) двоично-десятичный. В двоично-десятичном режиме константа задается в диапазоне 1-9999.

Поле M определяет режимы работы ПСТ:

- 0 - прерывание от таймера;

- 1 - программируемый ждущий мультивибратор;

- 2 - программируемый генератор импульсов;

- 3 - генератор меандра;

- 4 - программно-запускаемый одновибратор;

- 5 - аппаратно-запускаемый одновибратор.

Поле RW определяет способ загрузки констант через однобайтовый порт. Если в этом поле задано значение 00, это управляющее слово будет использоваться для фиксации текущего содержимого регистров счетчика CE в буферном регистре OL с целью чтения программой. Это код команды CLC - фиксация регистров. Код канала, для которого будет выполняться фиксация, должен быть указан в поле SC. Поля M и B при этом не используются.

Поле SC определяет номер канала, для которого предназначено управляющее слово. Если в этом поле задано значение 11, будет выполняться чтение состояния канала.

Как указывалось в начале раздела одна из функций выполняемых ПСТ – генерация звуковых сигналов. В компьютере большинство операций обмена данными регулируется параллельным программируемым адаптером(ППА). Этот адаптер содержит три 8-разрядных регистра; два из них используются для операций ввода данных, а один - для вывода. Выходному регистру ППА соответствует номер порта 61Н. Динамиком можно управлять в двух режимах, задаваемых значениями двух битов выходного регистра ППА. Если бит 0 равен 1, то системный таймер (ПСТ) задает частоту звучания динамика. Если бит 1 равен 1, то динамик начинает издавать звук и продолжает звучать до тех пор, пока бит 1 не станет равным 0.

Системные регистры

Системные регистры предназначены для обслуживания ЦП при многозадачной обработке. Для этого ЦП переводится в защищенный режим. Прежде, чем процессор перейдёт в защищённый режим, должна быть определена глобальная дескрипторная таблица GDT (Global Descriptor Table), так как все сегменты и прочие системные объекты должны быть описаны в дескрипторной таблице.

Глобальная дескрипторная таблица GDT - это область памяти, в которой находятся дескрипторы. Процессору всё равно, где именно вы расположили эту таблицу, но в любом случае она будет находиться в первом мегабайте адресного пространства, потому что только из режима реальных адресов можно перевести процессор в защищённый режим. Также подразумевается, что сама таблица GDT будет выровнена на границу 8 байт, так как дескрипторы, из которых она состоит, имеют 8-байтный размер. Такое выравнивание позволит процессору максимально быстро обращаться к дескрипторам, что, естественно,

увеличивает производительность.

Число дескрипторов, определённых в GDT, может быть любым, от 0 до 8192. Нулевой дескриптор, т.е. определённый в самом начале GDT, процессор не использует, обращение к такому дескриптору могло бы быть, когда поле Index селектора равно 0. Если всё же в программе встречается обращение к нулевому дескриптору, то процессор генерирует исключение и не позволит доступ к такому дескриптору. В связи с этим, везде в литературе рекомендуется использовать нулевой дескриптор как шаблон, на основе которого программа может создавать новые дескрипторы, но на практике их удобнее создавать иными способами, о которых мы ещё будем говорить.

GDT используется процессором всё время, пока он находится в защищённом режиме. Параметры GDT хранятся в специальном 48-разрядном регистре GDTR:

Рис. 4.5. Формат регистра GDTR.

Адрес начала GDT - это тот адрес, по которому размещена таблица.

Предел таблицы GDT - это максимальное смещение относительно её начала. Например, создаётся GDT, состоящую из 3-х дескрипторов - для сегментов кода, стека и данных. Общее число дескрипторов будет равно четырём, потому что первым по счёту будет идти нулевой дескриптор, а за ним уже остальные три:

| Смещение от начала GDT | Назначение дескриптора |

| Нулевой | |

| Сегмент кода | |

| Сегмент стека | |

| Сегмент данных |

Размер GDT в данном случае будет равен 32 байтам, следовательно, предельное смещение в таблице будет равно 31 - это и есть предел GDT.

Для загрузки значения в регистр GDTR используется команда LGDT. Операндом этой команды является 48-разрядное значение адреса в памяти, где размещается адрес и предел GDT. Можно также сохранить содержимое GDTR командой SGDT, указав в операнде адрес 48-разрядной переменной в памяти. Следует отметить, что размер GDT желательно не менять в процессе выполнения программ в защищённом режиме. Если программа будет динамически создавать новые дескрипторы, то размер GDT лучше всего заранее задать достаточно большим, например, 64 Кб (максимальный размер). Однако, следует учитывать, что при обращении процессора к несуществующим дескрипторам, его поведение непредсказуемо, хотя оно, скорее всего, закончится зависанием.

Все 32-разрядные процессоры, начиная с Intel 80386, имеют набор системных регистров, предназначенных для использования в защищённом режиме. Среди них есть регистры управления (Control Registers) CR0, CR1, CR2, CR3 и CR4.

Регистры управления, в основном, состоят из флагов. Назначение и использование каждого флага достаточно сложно и требует отдельного рассмотрения. Для начала мы рассмотрим только один бит PE (Protection Enable) регистра CR0, отвечающего за переход процессора в защищённый режим и обратно. Полный список с описаниями регистров управления можно найти, например на www.sasm.narod.ru/docs/pm.

Регистры управления предназначены для считывания и записи информации. Они имеют размер 32 бита и оперировать ими можно только целиком - считывается значение целого регистра, изменяются нужные биты и записывается обратно. Единственная команда, которой позволен доступ к этим регистрам - это MOV, в качестве операнда которой используется 32-разрядный регистр общего назначения.

Если установить бит РЕ в 1,то процессор перейдёт в защищённый режим, если сбросить - то в режим реальных адресов. Процессор после аппаратного сброса переходит в режим реальных адресов и бит PE сброшен.

Ниже приведены примеры использования бита PE:

1. Перевод процессора в защищённый режим.

mov eax,cr0 ; Копируем в EAX содержимое регистра CR0.

or al,1 ; Устанавливаем в копии 0-й бит, который

; соответствует 0-му биту CR0, т.е. биту PE.

mov cr0,eax ; Записываем в CR0 обновлённое значение.

; Процессор перешёл в защищённый режим.

... ; 1-я команда программы, которая выполнится

; в защищённом режиме.

2. Перевод процессора в режим реальных адресов.

mov eax,cr0

and al,0feh ; Сбрасываем бит PE.

mov cr0,eax ; Процессор перешёл в режим реальных адресов.

Если просто выполнить переход в защищённый режим, как показано на приведенном выше примере, то процессор зависнет. Для работы в защищённом режиме процессор использует дескрипторы сегментов, вместо их адресов (которые находятся в сегментных регистрах), поэтому прежде, чем перевести процессор в защищённый режим, нужно провести определенные подготовительные работы. Эти особенности будут рассмотрены в следующем разделе.

Контрольные вопросы

1. Сколько режимов обслуживания прерываний обеспечивает ПКП?

2. В чем заключаются особенности работы ПКП в режиме поллинга и когда его целесообразно использовать?

3. Сколько уровней аппаратных прерываний могут обслужить четыре ПКП и как их следует объединить между собой?

4. Какие параметры передаются контроллеру ПДП при программировании?

5. Перечислите режимы работы контроллера ПДП и объясните особенности использования каждого режима.

6. Сколько каналов включено в ПСТ и в чем заключается основное предназначение каждого канала?

7. Какие регистры содержит каждый канал ПСТ и в чем их предназначение?

8. В чем заключается основное назначение системных регистров ЦП?

9. Опишите формат регистра GDTR и назначение его полей.

10. В чем заключается основное назначение регистров управления ЦП?

11. Сколько уровней прерываний можно обслужить с помощью ПКП?

12. Объясните назначение схемы сравнения приоритетов.

13. Для чего используется сигнал SP/EN?

14. Перечислите последовательность действий при обслуживании прерываний.

15. Объясните назначение режима блочной передачи.

16. Опишите особенности режимов работы системного таймера.

17. Какое число дескрипторов можно определить в GDT?

18. Что означает предел таблицы GDT?

19. Как и для чего используется бит РЕ регистра управления?

20. Опишите основное назначение системных регистров.

Дата добавления: 2018-11-26; просмотров: 1290;