Цифровые синтезаторы частот, построенные на основе импульсных последовательностей.

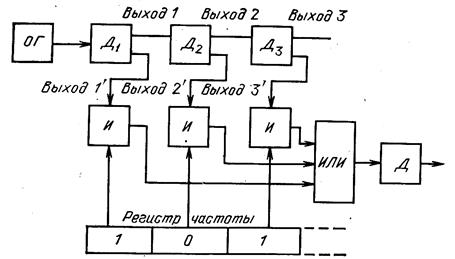

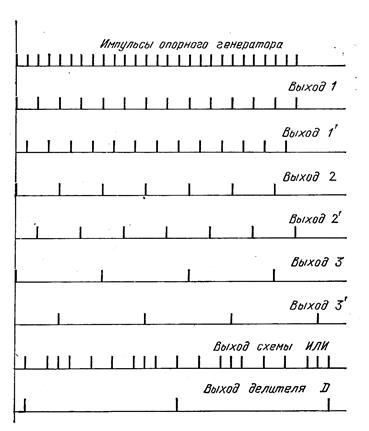

В настоящее время при создании синтезаторов частот, выполненных по принципу прямого синтеза, широко стали применяться цифровые методы. Примером может служить синтезатор частот, построенный на основе суммирования импульсных последовательностей (рисунок 1). Данная схема выполнена полностью на цифровых интегральных микросхемах. Эпюры, соответствующих импульсных последовательностей, показаны на рисунке 2.

Рисунок 1.Цифровой синтезатор частот, построенный на основе импульсных последовательностей.

Рисунок 2.Эпюры импульсных последовательностей.

Сигнал опорного высокостабильного генератора (ОГ) поступает на триггерный счетчик – делитель, состоящий из n двоичных разрядов (на рисунке показаны три разряда). На выходе делителя каждого разряда (D1; D2; D3) получаются по две последовательности импульсов (например, 1 и 1/), сдвинутых на T/2, где Т – период соответствующей импульсной последовательности. Частота импульсной последовательности на выходе каждого делителя D в два раза ниже частоты входной импульсной последовательности.

На схемы «И» поступают с выходов делителей 1/, 2/, 3/ и т.д. импульсные последовательности. На другой вход схемы «И» поступает с регистра частоты «1» или «0». Если в регистре частота записана «1», то соответствующая импульсная последовательность с делителя D1 u D3 проходит в схему «ИЛИ», если же записан «0», то схема «И» закрыта и импульсная последовательность на схему «ИЛИ» не проходит. Следовательно, на выходе схемы «ИЛИ» происходит суммирование соответствующих последовательностей в соответствии с заданным кодом частоты. На выходе схемы «ИЛИ» получается импульсная последовательность с неравномерной расстановкой импульсов. Средняя частота импульсов на выходе схемы «ИЛИ» определяется управляющим кодом, записанным в регистре частоты. Для уменьшения неравномерности импульсов на выходе схемы «ИЛИ» включают делитель частоты с коэффициентом деления N.

На выходе такого делителя импульсная последовательность более равномерная (рисунок 2). Чем выше коэффициент деления, тем больше равномерная выходная импульсная последовательность и тем меньше уровень побочных частот в выходном спектре синтезатора. Но при этом частоты синтезатора при заданной частоте опорного генератора оказываются низкими.

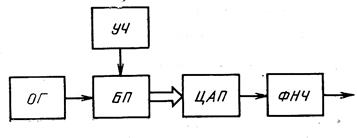

Другой разновидностью синтезатора частот, в котором использован цифровой принцип формирования частот, является синтезатор с цифровым формированием отсчетов синтезируемого колебания (рисунок 3).

Рисунок 3.Синтезатор с цифровым формированием счета.

Здесь в блоке памяти (БП) хранятся отсчеты синусоиды (данные от значения синусоиды при различных фазах). По определенной программе в соответствии с кодом частоты, записаны в блоке установки частоты (УЧ), происходит вычисление текущих значений синусоиды. Частота в импульсной последовательности на выходе ЦАП кратна шагу сетки частот  :

:

.

.

Поскольку на выходе синтезатора необходимо формирование синусоидального колебания, то после блока памяти включается цифроаналоговый преобразователь (ЦАП). Для устранения побочных частот после блока ЦАП включен фильтр нижних частот (ФНЧ). Число отсчетов синусоиды 2N определяется объемом памяти блока вычисления отсчетов. Так если все отсчеты синусоиды считываются с частотой fо.г=1/Tо.г опорного генератора (ОГ), то период импульсной последовательности на выходе блока ЦАП Т=То.г2N, где То.г – период сигнала опорного генератора. Следовательно, минимальная частота импульсной последовательности  . Изменяя число импульсов ОГ, считываемых за период (т.е. число N), можно изменить частоту импульсной последовательности на выходе ЦАП.

. Изменяя число импульсов ОГ, считываемых за период (т.е. число N), можно изменить частоту импульсной последовательности на выходе ЦАП.

Минимальное число ОГ импульсов равно двум; следовательно  . Верхняя частота

. Верхняя частота  определяется граничной частотой цифровых микросхем и блока ЦАП. Т.к. на выходе синтезатора нет деления частоты, то граничная частота синтезатора с отсчетами синтезируемого колебания оказывается выше, чем в синтезаторах, построенных на основе суммирования импульсных последовательностей.

определяется граничной частотой цифровых микросхем и блока ЦАП. Т.к. на выходе синтезатора нет деления частоты, то граничная частота синтезатора с отсчетами синтезируемого колебания оказывается выше, чем в синтезаторах, построенных на основе суммирования импульсных последовательностей.

Дата добавления: 2018-11-26; просмотров: 1318;