Модули обработки информации

В системе «Транслог 2» для обработки сигналов, полученных с модулей ввода информации, их преобразования и формирования имеются следующие модули:

| - | статический триггер | |

| - | логические схемы «ИЛИ» и «ИЛИ -НЕ» | |

| - | логические схемы «И» | |

| - | логические схемы «И» | |

| - | логические схемы «ИЛИ» | |

| - | логическая схема «НЕ» | |

| - | логическая схема равнозначности и неравнозначности | |

| - | динамический триггер | |

| - | дешифратор | |

| - | ждущий мультивибратор | |

| - | ждущий мультивибратор | |

| - | линия задержки | |

| - | неустойчивый мультивибратор | |

| - | модуль сигнализации | |

| - | регистр сдвига | |

| - | счетчик прямого счета | |

| 2027 | - | реверсивный счетчик |

| - | датчик тактовых импульсов |

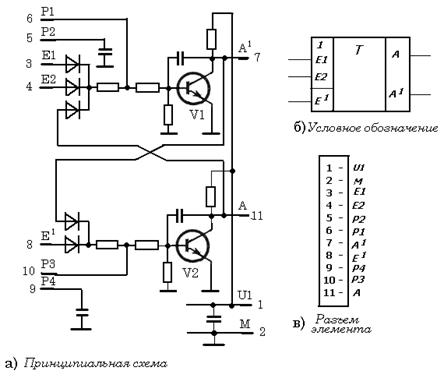

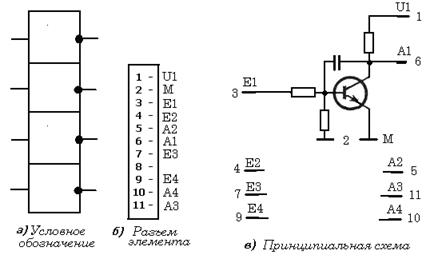

Модуль 2011 представляет собой триггер, собранный на двух схемах «ИЛИ-НЕ» и предназначен для запоминания логических сигналов (рис 6.7.).

Рисунок 6.7 - Логический модуль 2011

Входы Е1 и Е2 служат для. управления работой модуля и реализуют функцию «ИЛИ», на что указывает единичка в обозначении модуля. Вход Е - устанавливающий, он необходим для установки модуля в исходное состояние (на входе А – «0» - сигнал, на А1 – «L» сигнал). Выводы Р1, Р2, РЗ и Р 4 используются для подключения внутренних конденсаторов, улучшающих помехоустойчивость модуля.

Пусть в исходном состоянии на выходе модуля А – «0» - сигнал, а на А1 – «L»- сигнал. Это означает, что транзистор V2 открыт положительным потенциалом за счет обратной связи с выхода закрытого транзистора V1

При подаче на один из входов Е1 или E2 «L» - сигнала транзистор V1 открывается. Потенциал его коллектора уменьшается до нуля и снимает управление со входа транзистора V2 через обратную связь. Последний закрывается и на его выходе появляется «L» - сигнал. Исчезновение сигнала на входе E1(E2 ) не изменит состояние схемы, т.к. за счет обратной связи с выхода транзистора V2 через диод на базу V1 будет подаваться «L» - сигнал. Логика работы модуля показана в таблице истинности.

| А1 или А2 | Е1 | А | А1 | ||

L L

| |||||

| L | |||||

| L | L | ||||

| L | L | ||||

| L | L |

Модуль 2012. Логические модули 2012 имеют несколько разновидностей в зависимости от реализации логической функции и назначения.Различают: пассивный модуль 2012.01 «ИЛИ» 3/4; дополнительный модуль 2012.02 – «ИЛИ» 3/4 и модуль 2012.03 – «ИЛИ-НЕ» 3/4.

.

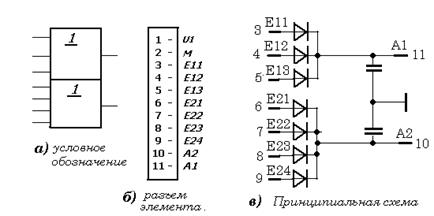

Рисунок 6.8. Логический модуль 2012.1

Модуль 2012.01 предназначен для реализации операции логического сложения и представляет собой собранные в одном корпусе две независимых друг от друга логических схемы «ИЛИ» на 3 и 4 входа. Принципиальная схема, обозначениемодуля показаны на рис. 6.8.

Последовательное включение пассивных схем «ИЛИ» недопустимо, т.к. происходит сильное искажение логической информации. Число входов данного модуля может быть увеличено до 40 с помощью расширителя 2012.02.

Логика работы модуля аналогична логике работы модуля 1DD03 системы "Транслог 1" Модуль 2012.02 предназначен только для увеличения числа входов пассивного модуля 2012.01. На рис.6.9 показана принципиальная схема модуля и клеммная колодка. Подсоединение происходит следующим образом: выход А1(11) или A2(10) присоединяется к одному из входов Е модуля 2012.01

Рисунок 6.9. Логический модуль 2012.2

Модуль 2012.03 предназначен для реализации логической операции «ИЛИ-НЕ» (операции Пирса) и представляет собой собранные в одном модуле две независимые друг от друга схемы «ИЛИ-НЕ» на 3 и 4 входа. Обозначение модуля, принципиальная: схема и клеммная колодка показаны на рис 6.10..

Рисунок 6.10. Логический модуль 2012.03

Логика работы модуля та же, что у модуля 1NN11 системы «Транслог-1» В исходном состоянии при отсутствии входного сигнала транзистор заперт отрицательным смещением от провода М на базу. На выходе А1(11) или А2 (10) «L» - сигнал. При подаче на один из входов Е «L» - сигнала транзистор открывается, на его коллекторе напряжение падает до нуля, и на выходе появляется «0» - сигнал.

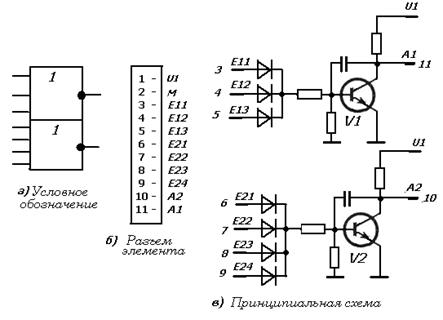

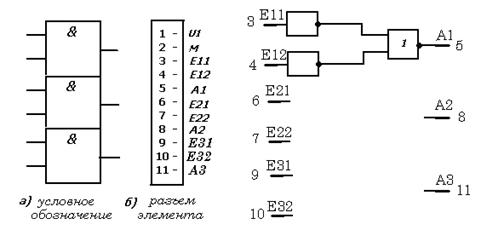

Модуль 2013 предназначен для реализации операции логического умножения и представляет собой собранные в одном корпусе на элементах «НЕ» и «ИЛИ – НE» две независимые друг от друга активные схемы «И» на 3 и 4 входа (рис.6.11 ).

В исходном состоянии при отсутствии хотя бы на одном из входов Е «L» - сигнала на выходе схемы А1(А2) - «0» - сигнал. Только при подаче на все входы одной или второй схемы «L» - сигнала, на выходе А1 или А2 будет тот же сигнал.

Логика работы модуля аналогична работе 1КК01 системы «Транслог 1» ,несмотря на иную реализацию его схемы.

Рисунок 6.11. Логический модуль 2013

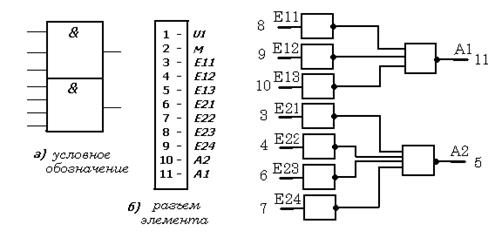

Модуль 2014 предназначен для реализации операции логического умножения и представляет собой собранные в одном корпусе на элементах «ИЛИ» и «НЕ» три независимых друг от друга активные схемы «И» на два входа каждая (рис.13.12). Логика работы модуля, так же как и предыдущего, аналогична логике работы модулей 1КК01, 1KN05, 1KN07 системы «Транслог -1».

Рисунок 6.12 Логический модуль 2014

Модуль 2015предназначен, так же как и 2012.01 для реализации операции логического сложения и представляет собой собранные в одном корпусе две логические схемы «ИЛИ» на 3 и 4 входа.

Выход такой схемы можно использовать. для управления светодиодами. Принципиальная схема, обозначение модуля, распайка клеммных выводов показана на ,рис 6.13. .В отличие от 2012.01 данная схема является активной, а следовательно, не требует последующей установки усилительного элемента для улучшения (регенерации) фронтов и величины выходного сигнала.

Рисунок 6.13 Логический модуль 2015

Модуль 2016 представляет собой собранные в одном корпусе четыре схемы логического отрицания и предназначен для инвертирования входных сигналов.

Обозначение модуля, одна из четырех схем «НЕ» и распайка клеммных выводов показана на рис.6.14. Логика работы и принцип действия аналогичны подобным элементам в системе «Транслог -1» 1KN 05 или 1NN11 при одном рабочем входе.

Рисунок 6.14 Логический модуль 2016

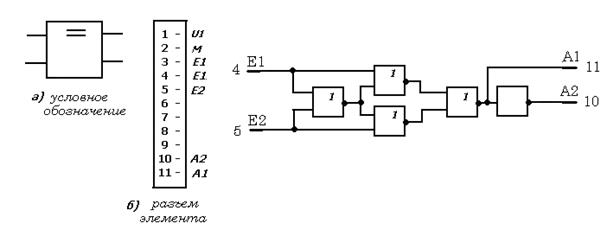

Модуль 2017 представляет собой собранную на элементах «НЕ» и «ИЛИ-НЕ» схему, реализующую логические операции равнозначности и неравнозначности (рис.6.15).

Логическая операция равнозначности реализуется на выходе модуля А1 в том случае, если на его входы Е1 и Е2 приходят одинаковые сигналы, т.е. «0» - сигнал или «L» - сигнал:

. А1 = E1E2 v Ē1Ē2

Рисунок 6.15 Логический модуль 2017

в случае, когда на входы модуля сигнал подан в противофазе, например, на вход Е1 – «0» - сигнал, а на Е2- «L» - сигнал или наоборот, на выходе модуля A2 реализуется логическая операция неравнозначности, т.е.

A2 = E1Ē2 v Ē1E2 .

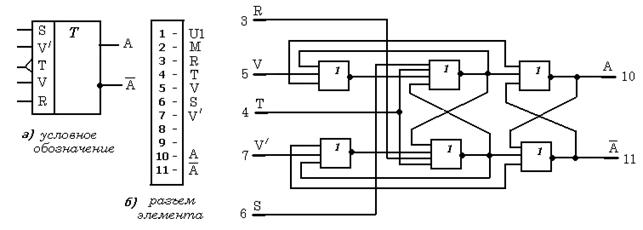

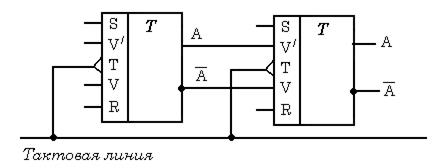

Модуль 2018 представляет собой динамическое запоминающее устройство (триггер), собранное на шести элементах «ИЛИ-НЕ» (рис. 6.16).

Рисунок 6.16 Логический модуль 2018

Модуль предназначен дляпостроения счетных и пересчетных схем, регистров сдвига. кольцевых счетчиков и других последовательностных схем.

Входы R и S – установочные, необходимы для исходной установки триггера. По входу S триггер через 20 мкс устанавливается в единицу (на выходе А – «L» - сигнал), а по входу R через 20 мкс триггер устанавливается в нуль, т.е. .на выходе А – «0» - сигнал.

Входы V и V' - подготовительные, необходимые для обеспечения устойчивой работы триггера. При необходимости они соединяются перемычками с выходами модуля.

Вход Т - тактовый (счетный, динамический), по нему в триггер поступает двоичная информация в виде положительных импульсов с частотой f ≤ 10 кГц или периодом следования ≥100 мкс. Запуск происходит отрицательным (задним) фронтом импульса или перепадом L / 0 и через 40 мкс схема изменяет свое состояние.

Принцип действия модуля 2018 и модуля 1Z33 системы «Транслог-1» аналогичны. На рис. 13.16 показана только логическая схема модуля 2018.

Если модуль 2018 устанавливается в счетных и пересчетных схемах, то на клеммной колодке ставятся перемычки между выводами 10 - 5 и 11 - 7. Таким образом, предотвращается ложное срабатывание триггера, т.к. с подачей сигнала с выходов А и Ā на входы V и V' схема подготавливается к приему информации на входе Т.

Рисунок 6.17. Регистр сдвига на логическом модуле 2018

Для построения регистров сдвига и кольцевых счетчиков выходы первого триггера соединяются с подготовительными входами следующего, как показано на рис. 6.17.

Тактовые входы всех триггеров при этом объединяются тактовой линией, по которой поступает информация от одного источника сигналов.

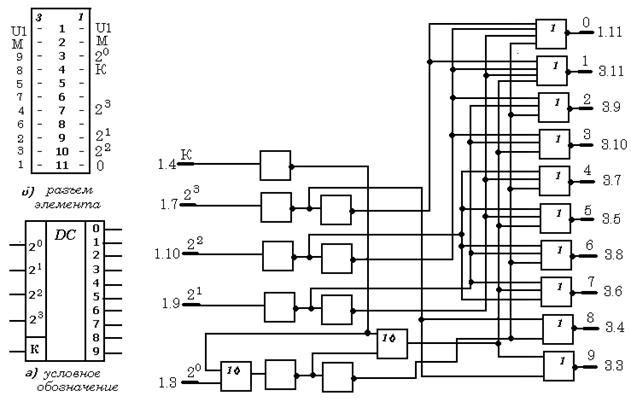

Модуль 2019 представляет собой комбинационную логическую схему, в которой происходит преобразование информации из двоичной системы кодирования в десятичную, и называется дешифратором (декодером или преобразователем кода). Преобразование осуществляется с помощью элементов «НЕ» и «ИЛИ-НЕ» системы «Транслог – 2», соединенных между собой определенным образом (рис.6.18). На входы модуля 20, 21, 22 и 23 подается информация в виде четырехразрядного двоичного числа. Появление «L» - сигнала на любом входе соответствует наличию логической единицы на этом входе. Отсутствие «L» - сигнала соответствует логическому нулю. Вход К предназначен дляустановки дешифратора в исходное состояние, при котором на выходах модуля 0,1,……,9 появляется «0» - сигнал. Установка производится L / 0 перепадом логического сигнала, т.е. его отрицательным фронтом. В рабочем состоянии на входе К должен присутствовать «L» - сигнал.

Рисунок 6.18 Логический модуль 2019

Появление на одном из десяти выходов дешифратора (выводы клеммной колодки 3.3 ÷ 3.11) «L» - сигнала соответствует цифре десятичной системы от 0 до 9. Логика преобразований. происходящих в модуле, наглядно иллюстрируется таблицей истинности (таблица 6.1).

Из таблицы можно сделать очень важный для практики вывод: если на выходах модуля имеется «0» - сигнал, это значит на входе К тоже «0» - сигнал или он оборван. Если на выходах модуля имеется несколько «L» - сигналов одновременно, это значит, что на входы поступила неправильная логическая информация.

Таблица 6.1

| Входы | Выходы | |||||||||||||

| 23 | 22 | 21 | 20 | К | ||||||||||

| L | L | |||||||||||||

| L | L | L | ||||||||||||

| L | L | L | ||||||||||||

| L | L | L | L | |||||||||||

| L | L | L | ||||||||||||

| L | L | L | L | |||||||||||

| L | L | L | L | |||||||||||

| L | L | L | L | L | ||||||||||

| L | L | L | ||||||||||||

| L | L | L | L | |||||||||||

| любой |

Модуль 2020 представляет собой ждущий (моностабильный) мультивибратор, (звено малой выдержки), предназначенный длягенерации импульса положительной полярности. по форме близкой к прямоугольной. Длительность выходного импульса Т может изменяться от 100 мкс до 30 с за счет подключения внешних элементов и дополнительных перемычек. Принципиальная схема, обозначение, клеммная колодка и расположение переменных съемных элементов показаны на . рис. 6.19.

Рисунок 6.19 Логический модуль 2020

Для модуля возможны два режима работы.

1 режим:

В модуле устанавливается перемычка между выходом А и входом E2 (на рисунке показана пунктиром). В этом случае входной сигнал в виде логической единицы подается только на вход Е1, а на выходе А появляется положительный прямоугольный импульс. В исходном состоянии транзистор V1 заперт. а V2 открыт, и работа модуля аналогична npинципу действии модуля 1М20 системы «Транслог – 1». При этом длительность выходного импульса не зависит от продолжительности входного.

Входы P1, Р2, РЗ, Р4 и М предназначены для установки перемычек, обеспечивающих более надежную работу модуля, и непрерывное изменение длительности выходного сигнала. Следует помнить, что для устойчивой работы модуля длительность паузы между входными сигналами должна быть больше установленной длительности выходного сигнала.

Перемычка Р2- U1 устанавливается, когда необходимо длительность входного сигнала (время задержки) уменьшить в 2 раза. Для плавного изменения длительности выходного сигнала вместо перемычки между Р2 и U1 можно поставить внешний потенциометр Rext (см. рис. 13.19).

Перемычка Р1 - М позволяет подключить конденсатор С1 во входную цепь. модуля и тем самым увеличить его помехоустойчивость по входу. При этом длительность входного импульса должна быть увеличена с 20 до 150 мкс, а инерционность схемы при этом увеличивается от 15 до 150 мкс.

Для подключения съемных элементов С2, СЗ и R1 на плате предусмотрены штифты, при этом длительность выходного сигнала находится в следующей зависимости от параметров элементов:

Т ≈ 01 0,36 RC,

где 33 кОм ≤ R ≤ 66 кОм;

5 х 103 пФ ≤ С ≤ 5 х103 мкФ; С = С2 + С3;

R 2 = R 3 = З3 кОм.

2 режим:.

В этом режиме перемычка 1.11 – 1.4 (А - Е2) отсутствует. Поэтому входной сигнал можно подавать как на Е1, так и на Е2. Работа схемы происходит аналогично режиму 1. Однако, отсутствие перемычки позволяет вернуть схему в исходное состояние снятием входного сигнала. В этом случае после исчезновения входного импульса в течение 15 мкс, схема вернется в исходное состояние, т.е. на выходе появится «0» - сигнал. Если в схеме подключен конденсатор С1, то время возвращения увеличивается до З00 мкс.

По выходу R схема может быть возвращена в исходное состояние прежде, чем истекла заданная длительность импульса на входе А . (время задержки модуля). При подаче на вход R1 «L» - сигнала транзистор V3 открывается, и на выходе А «L»- сигнал исчезает в течение 15 мкс. Длительность импульса обратной установки изменяется от З0 до 400 мкс в зависимости от подключения C1.

Если сигнал с модуля далее подается на динамический вход другого, то после модуля 2020 необходимо поставить триггер для восстановления фронта сигнала.

Модуль 2021 предназначен для генерирования сигнала с длительностью от 0,75 до 191,25 с. (звено большой выдержки).

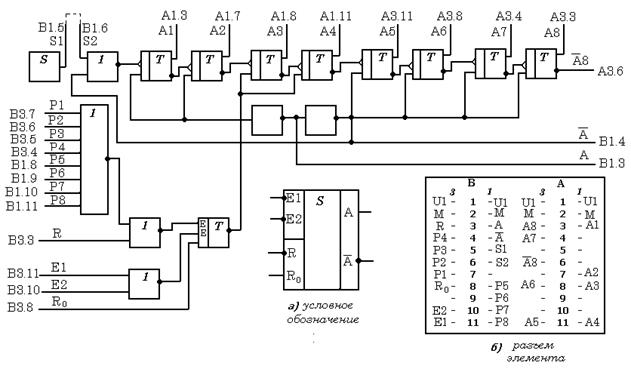

Он содержит генератор тактовых импульсов, восемь триггеров (пересчетных ступеней), набор логических схем «НЕ» и «ИЛИ-НЕ» и триггер с инверсным выходом для управления работой данного модуля (рис. 13.20).

Рисунок 6.20 Логический модуль 2021

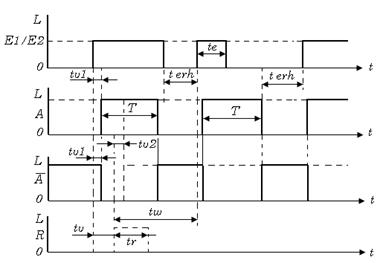

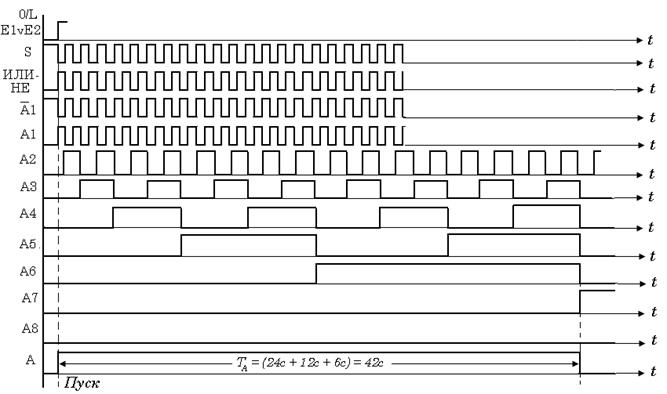

Модуль работает по принципу пересчета импульсов, поступающих с генератора тактовых пульсов с периодом следования Т0 = 0,75 с по перемычке S 1 - S 2 (В 1.5 - В 1.6). На входе модуля А (Ā) появляется «L» - сигнал («0» - сигнал) через tV1 ≤ 30 мкc после подачи «L». - сигнала (длительностью tС ≥ 50 мкс) на входы E1 или Е2 (рис.6.20). с помощью перемычек между выводами Аi. и Pi, можно установить любую из указанных длительностей выходного сигнала:

Таблица 6.2

| Выход | А1 | А2 | А3 | А4 | А5 | А6 | А7 | А8 |

| Т,с | 0,75 | 1,5 | 3,0 | 6,0 |

Продолжительность восстановления модуля составляет terh ≥ 500 мкc. Это означает, что новый запуск модуля возможен только через 500 мкс после возращения его в исходное состояние. .

Установка модуля в исходное состояние осуществляется по входу R0. При этом все элементы памяти (триггера) .переводятся в состояние «0» по выходам А. На выходе А модуля появляется «0» - сигнал, а на инверсном выходе Ā «L» - сигнал. Одновременно «L» - сигнал выхода А блокирует поступление тактовых импульсов на пересчетные ступени через схему «ИЛИ-НЕ».

По входу R происходит преждевременная установка в исходное состояние схемы модуля «L» - сигналом, длительность которого tr ≥ 50 мкс. На выходе А в этом случае «L» - сигнал исчезнет через tV2 ≤ З0 мкс. Следующий запуск модуля при установке по входу R возможен только через tw =200 мкс (см.рис.6.21).

Вместо встроенного в модуль генератора тактовых импульсов S можно использовать внешний генератор для изменения тактовой частоты. При этом максимальная тактовая частота импульсов должна составлять 1 кГц, перемычка S1 – S2 снята. Импульсы с внешнего генератора подаются на вход S2.

Схема модуля собрана таким образом, что при подаче питания все элементы памяти приходят в исходное состояние (на выходах Аi. – «0» - сигнал). Если модуль работает от источников питания, время выхода на режим которых больше 1с, то подачей «L» - сигнала на вход R0 все элементы памяти модуля приводятся в исходное состояние, «L» - сигнал должен существовать на R0 до тех пор, пока напряжение питания станет номинальным.

Управление модулем по входам Е1, Е2, S2, Р1…..,Р8 пассивными "ИЛИ" не допускается. В исходном состоянии все элементы памяти пересчетной цепи находятся в нулевом состоянии по выходам Аi (прямые выходы). Триггер цепи управления на своем инверсном выходе имеет «L» - сигнал, который осуществляет установку триггеров пересчетной цепи, блокирует поступление тактовых импульсов в пересчетную цепь через две схемы «НЕ» и «ИЛИ-НЕ» нa 2 входа, на выходе которой имеется «0» - сигнал. Кроме того, «L» - сигнал триггера цепи управления через схему «НЕ» держит устойчивый «0» - сигнал на выходе модуля А и через 2 схемы «НЕ» «L» - сигнал на Ā. На выходе схемы «ИЛИ-НЕ» (8 входов) присутствует «L» - сигнал , который в исходном состоянии не оказывает влияния на длительность сигнала выхода А модуля. На выходах схем «ИЛИ-НЕ», управляющих работой триггера цепи управления по двум динамическим входам, имеются «0» - сигнал на верхней и «L» - сигнал на нижней.

При запуске модуля по одному из входов Е произойдет опрокидывание триггера цепи управления и на его инверсном выходе появится «0» - сигнал. Это изменение приведет к появлению «L». - сигнала на выходе А модуля (В 1.3), «0» - сигнала на инверсном выходе Ā (В 1.4), снятию сигнала начальной установки по всем триггерам пересчетной ступени и сигнала блокировки на «ИЛИ-НЕ», разрешающего работу тактового генератора S

Рисунок 6.21 Преждевременная установка в исходное состояние модуля 2021

. При этом работа модуля будет происходить в соответствии с развернутой временной диаграммой, показанной на рис. 6.22 «L» - сигнал на выходе А модуля будет существовать до тех пор, пока на выходе «ИЛИ-НЕ» .(8 входов) будет находиться «0» - сигнал. Как только в схеме «ИЛИ-НЕ» на установленных перемычках произойдет одновременная смена сигналов (см. временную диаграмму выхода А ) с уровня «L» на «0», на выходе этой схемы появится «L» - сигнал, который прервет «L» - сигнал на выходе схемы А

Рисунок 6.22 Развернутая временная диаграмма модуля 2021

через триггер цепи управления. Сигнал – «L» триггера цепи управления вновь восстановит исходное состояние модуля. На временной диаграмме (рис.6.22) показана длительность выходного сигнала Т = 42с, полученная с помощью перемычек А4 – Р1; А5 - Р2; А6 – Р3.

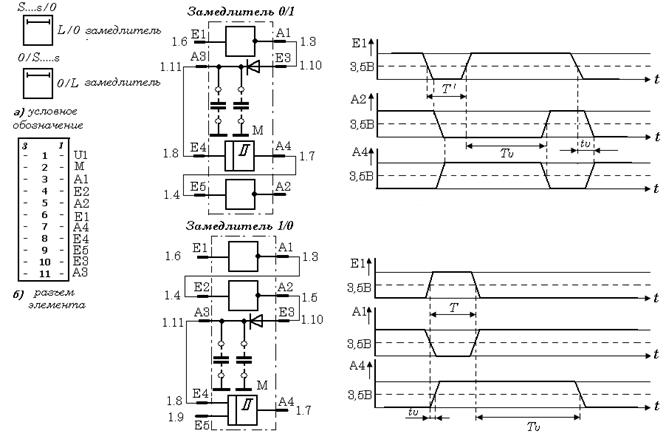

Модуль 2022 предназначен для задержки фронтов сигналов, а также замедления времени притяжения и отпускания контактов от 100 мкс до 50с. Функциональная схема модуля представляет собой набор из элементов «НЕ», триггера Шмидта, конденсаторов и диода. В зависимости от назначения модуля, с помощью перемычек на клеммной колодке, указанные элементы соединяются между собой и образуют схему замедления (линию задержки) 0/L.(положительных) или L/0 (отрицательных) фронтов, подаваемых на вход модуля сигналов (рис. 6.23).

При работе модуля в режиме замедления 0/L фронта должны быть поставлены перемычки А1 - ЕЗ, АЗ - Е4, А4 - Е2. Контактный вывод Е1 в этом случае является входом модуля, на который подается входной сигнал (см. временную диаграмму). В исходном состоянии при наличии «L» - сигнала на Е1 на выходе А2 модуля также присутствует «L» - сигнал. При изменении уровня сигнала на входе L/0 на выходе А1 появляется «L» -сигнал, который через диод запускает триггер Шмидта по выводу Е4. Конденсатор С в это время оказывается заряженным до напряжения U1. На выходе модуля А2 появляется «0» - сигнал как результат срабатывания триггера Шмидта. При появлении на входе Е1 вновь «L» - сигнала, на выводе А1 появится «0», а заряженный конденсатор начнет разрядку через входные резисторы триггера Шмидта на М. При достижении напряжением разряда конденсатора уровня второго порога срабатывания триггера, на его выходе появляется «0» - сигнал, а на выходе модуля А2 «L» - сигнал. Время задержки фронта определяется подбором емкостей Для более точной установки времени задержки (Т) в модуль параллельно входному резистору вывода Е4 триггера Шмидта присоединяется резистор. Для уменьшения ТV вдвое нужно поставить перемычку Е4 - Е5.

Рисунок 6.23 Логический модуль 2022

Работа модуля в режиме задержки L/0 фронта аналогична предыдущему. Для обеспечения этого режима нужно поставить перемычки А1 - Е2, А2 - Е3, А3 - Е4. Управление работой модуля также происходит по входу Е1 подачей на него 0/L- сигнала (см. рис. 6.23).

Модуль 2023 предназначен для генерирования последовательности положи- тельных прямоугольных импульсов с частотой от 0,1 Гц до 10 кГц. В системах судовой автоматики модуль генерирует положительные прямоугольные импульсы с частой ƒи = 10 кГц и применяется как датчик тактовых импульсов и проблесковый датчик частот для блоков сигнализации и оповещения. Принципиальная схема модуля содержит обычный RС - мультивибратор, к выходу которого присоединен элемент «ИЛИ-НЕ» на 2 входа дляусиления, инвертирования и стробирования последовательности выходных импульсов (рис. 6.24).

На этом рисунке также показаны обозначение и распайка клеммных выводов модуля. Работа модуля начинается при подаче питания на соответствующие контакты клеммной колодки... При этом за счет перезарядки конденсаторов коллекторно-базовых цепей транзисторов, подключенных внутри модуля (гнезда 1XL1 - 2ХL1 для С1 и 3XL1 4XL1 для С2) или извне к контактам РЗ - Р4 и Р5 – Р6 попеременно открывается то один, то другой транзистор мультивибратора, и на выходе модуля А появляются инвертированные 0/L прямоугольные импульсы положительной полярности. Частота выходных импульсов регулируется подбором емкостей С1 и С2 и резисторов R1 и R2. Обычно С1 = С2 и R 1= R 2.

Рисунок 6.24 Логический модуль 2023

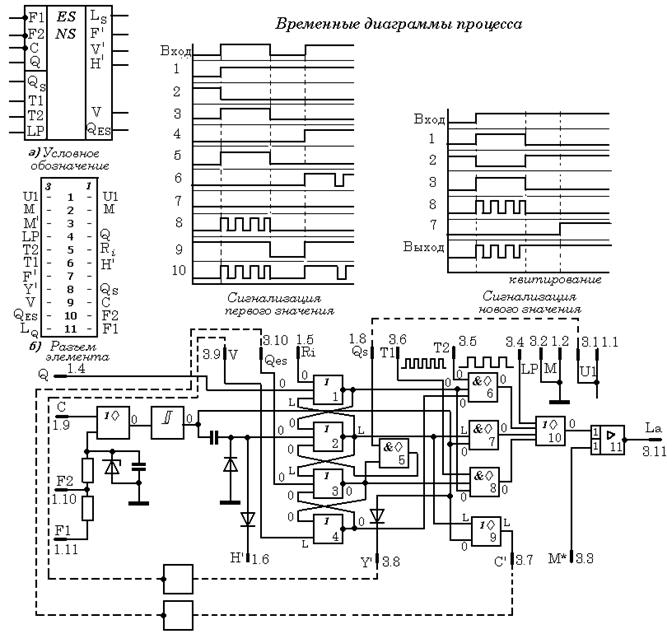

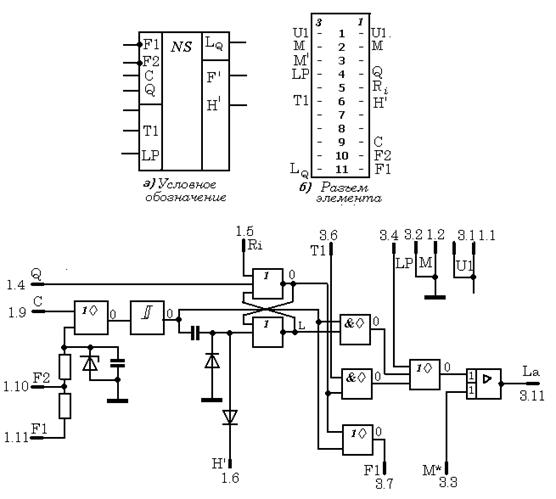

Модуль 2024 имеет две модификации 2024.01 и 2024.02, которые применяются для сигнализации выхода за пределы допусков различных параметров судовых систем.

Модуль 2024.01 - сигнализация "Новое значение/первое значение" служит для контроля за параметрами процесса, а также для оптической и акустической сигнализации превышения предельных значений параметров. С помощью внешних перемычек можно реализовать сигнализацию нового значения и первого значения (рис.6.25) .

Модуль имеет следующие входы:

| F 1 | - | вход ошибки на напряжение до 75 В; |

| F 2 | - | вход ошибки на напряжение до 30 В; |

| С | - | вход контрольной или логической ошибки |

| LP | - | вход для контроля ламп сигнализации и усилителя; |

| Т1 | - | вход для тактовых импульсов с частотой ƒ1 ; |

| Т2 | - | вход для тактовых импульсов с частотой ƒ2 < ƒ1. |

| Q | - | вход для подачи сигналов квитирования; |

Выходы модуля:

| LQ | - | выход к оптической сигнализации; |

| H’ | - | выход к акустической сигнализации (выдает игольчатый импульс на запоминающее устройство с последующим запуском сирены). |

Модуль может работать в двух режимах.

1.Сигнализация первого значения.

Дляработы в режиме сигнализации первого значения необходимо осуществить внешние соединения: вывод U1 с целью блокировки последующей ошибки после инвертирования присоединить к выводу U (см.рис.6.25). Дляблокировки квитирования первого значения вывод F1 после инвертирования присоединить к выводу QES . На вход Т1 подать импульсы с быстрым тактом, на Т2 - импульсы с медленным тактом. Исходное состояние схемы показано на рисунке - на функциональной схеме и временной диаграмме сигнализации первого значения.

Рисунок 6.25 Логический модуль 2024.01

При поступлении первой ошибки на один из входов:

С - уровень порога срабатывания от 2,5 до 5,5 В длительностью не менее 200 мкс,

F1 - уровень порога срабатывания от 2,0 до 4,2 В длительностью не менее 10 мс, или .

F 2 - уровень порога срабатывания от 1,4 до 2,3 В длительностью не менее 10 мс, на выходетриггера Шмидта появляется «L» - сигнал. Фронт 0/L этого сигнала, проходит через конденсатор и запускает схему сирены (вывод Н') и изменяет состояние элемента 2 (ИЛИ-НЕ). Изменение состояния элемента 2 приводит. к изменению состояний элементов 1 и 3 (ИЛИ~НЕ), на выходекоторых появляется «L» - сигнал. Элемент 8 (И),на вход которого поступают эти «L» - сигналы, начинает их пропускать синхронно импульсам быстрого такта входа Т1. Эти сигналы, пройдя через усилитель, вызывают быстрый мигающий свет сигнальной лампы. Если ошибка ненадолго исчезает до момента квитирования, то «0» - сигнал с выхода элемента 9 (ИЛИ) через внешний элемент «НЕ» опрокинет схему элемента 3, «0» -сигнал с выхода которого прекратит работу элемента 8,и мигание прекратится.

При повторном поступлении сигнала ошибки и опрокидывании в единичное состояние триггера Шмидта «L» - сигнал с еговыхода через вывод U1 запустит схему элемента 4 (ИЛИ-НЕ). «L» - сигнал с выхода элемента 4 укрепит нулевое состояние элемента 3 и запустит элемент 6 (И), выходной сигнал которого синхронно с сигналом входа Т2 вызовет медленное мигание сигнальной лампы.

При квитировании (т.е. подаче «L» - сигнала на вход Q или Ri) элемент 1 (ИЛИ-НЕ) своим выходным «0» - сигналом запретит работу элемента 6 (медленное мигание исчезает)и опрокинет в единичное состояние элемент 2. Выходной «L» - сигнал этого элемента даст возможность сработать элементу 7 (И), на второй вход которого поступает еще «L» - сигнал ошибки, что приведет к продолжительному свечению сигнальной лампы. При исчезновении сигнала ошибки схема приходитв исходное состояние, лампа на выходе усилителя гаснет.

2. Сигнализация нового значения.

При работе модуля в этом режиме необходимо осуществить следующие соединения: вывод V на U1 или к «L» - сигналу, вывод Qs на М или к «0» - сигналу, на вывод Т1 подать сигналы с тактового генератора. В этом случае будет работать только часть схемы. Исходное состояние показано на временной диаграмме сигнализации нового значения (рис.13.25).

При поступлении сигнала ошибки на один из входов С, Р1 или F2 триггер Шмидта переходит в единичное состояние, и как в предыдущем режиме, через вывод Н' запускается схема сирены, а на выходе модуля Lа наблюдается быстрый мигающий свет сигнальной лампы. Если сигнал квитирован подачей «L» - сигнала на вход элемента 1, происходит установка в исходное единичное состояние элемента 2, «L» - сигнал, с выхода которого поступает через элемент 7 и включает постоянное свечение сигнальной лампы на выходе модуля La, одновременно прерывая мигание лампочки через элемент 8. При исчезновении сигнала ошибки сигнальная лампа гаснет. Если ошибка исчезла до квитирования, то мигающий свет сохранится до подачи квитирования. С квитированием схема приходит в исходное состояние.

Модуль 2024.02 - сигнализация «Новое значение» - является составной частью модуля 2024.01, а также применяется как самостоятельный для контроля параметров процесса с оптической и акустической сигнализацией. Обозначение модуля, распайка клеммных выводов и логическая схема приведены на рис. 6.26.

Рисунок 6.26 Логический модуль 2024.02

Модуль имеет следующие входы:

| F1 | - | вход ошибки на напряжение до 75 В; |

| F2 | - | вход ошибки на напряжение до 30 В; |

| С | - | вход логической ошибки |

| Q | - | вход для квитирования оптической сигнализации; |

| Т1 | - | вход для подачи импульсов с тактового генератора; |

| LP | - | вход для проверки работы лампочки сигнализации и ееусилителя. |

Выходы:

| LQ | - | выход модуля к оптической сигнализации; |

| F’ | - | выход к независимой оптической сигнализации неисправности; |

| H’ | - | выход к акустической сигнализации (игольчатый импульс для запуска сирены). |

Исходное состояние схемы при отсутствии ошибки на входах показана на рис. 13.26. При появлении постоянного сигнала ошибки хотя бы на одном из обозначенных входов триггер Шмидта изменяет свое состояние и фронтом 0/L через вывод Н' запускает схему сирены. «L» - сигнал, снимаемый с верхней схемы «ИЛИ-НЕ», разрешает прохождение импульсов с тактового генератора (вывод T1) через элемент «И». Это приводит к появлению на выходе модуля мигающего света лампочки сигнализации. При нажатии кнопки квитирования (импульс «L» на вывод Q или R1 ) элементы «ИЛИ-НЕ» возвращаются в исходное состояние. Это позволяет «L» - сигналу с нижней схемы «ИЛИ-НЕ» пройти через верхнюю схему «И» (на втором ее входе имеется «L»..сигнал ошибки) и дать возможность лампочке сигнализации светить постоянно. При исчезновении сигнала ошибки лампочка гаснет. Схема возвращается в исходное состояние. Очевидно, что работа этого модуля аналогична работе модуля 2А80 системы «Транслог – 1».

Модуль 2025 представляет собой регистр сдвига, в основе которого используются триггеры, соединенные между собой так, что в каждый из них можно записать информационный сигнал, который представляет собой набор логических нулей и единиц, и осуществлять передвижение записанной информации слева направо по триггерам (рис.6.27).

Рисунок 6.27 Логический модуль 2025

Регистры предназначены для приема, хранения и передачи двоичной информации. Каждому разряду числа соответствует разряд (триггер) регистра. Регистры позволяют производить сдвиг числа на определенное количество разрядов, а также преобразование параллельного кода в последовательный и наоборот. .

Данный регистр сдвига содержит 4 разряда (по числу триггеров), по которым передвигается записанная по входу Еs или Si. двоичная информации слева направо по триггерам. Передвижение осуществляется параллельным управлением работой всех триггеров по входу Т (.рис. 6.27).

Модуль применяется для построения. кольцевых счетчиков, цепей сдвига, а также для реализации последовательно-параллельных и параллельно-последовательных преобразователей цифровой информации и имеет следующие входы:

| R1÷R4 | - | установки модуля в нулевое состояние по выходам Ai ; |

| S1÷S4 | - | установки модуля в единичное состояние по выходам А i; |

| T | - | тактовый; |

| ES | - | предварительной установки (для записи логической единицы в первый триггер). |

При последовательном включении нескольких модулей 2025 выход А4 соединяется со входом ЕS последующего модуля и все тактовые входы соединяются.

Работа регистра сдвига происходит следующим образом. В исходном состоянии осуществляется общая установка модуля в нулевое состояние по всем выходам Аi. . Затем по входу ЕS производится запись логической единицы в первый триггер (верхний вход). В таком состоянии схема ждет управления по входу Т для передвижения записанной в первый триггер логической един

Дата добавления: 2020-02-05; просмотров: 1272;