Организацияпроцессоров

Процессором называется устройство, непосредственно осуществляющее процесс обработки цифровой информации в ВМ и программное управление этим процессом.

Процессоры современных ВМ в большинстве случаев реализуют на одном кристалле. Соответствующую интегральную схему называют микропроцессором.

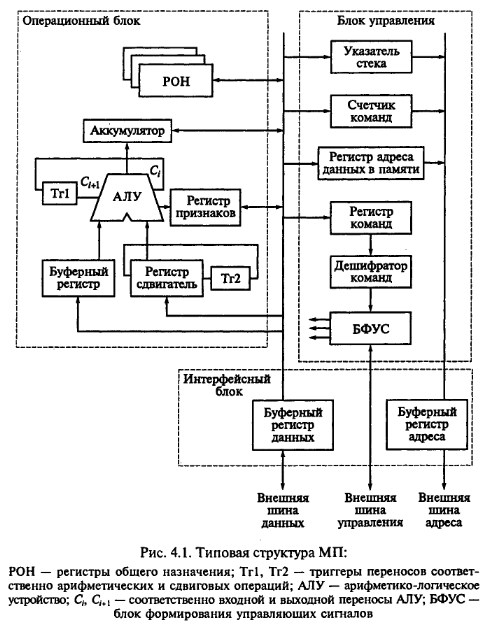

В самом общем случае функциональную схему МП можно представить в виде композиции трех функциональных блоков: операционного блока (ОБ), блока управления и интерфейсного блока (рис. 4.1). Кроме них в состав микропроцессора могут входить и некоторые другие блоки, участвующие в организации вычислительного процесса, например, блок прерывания, блок защиты памяти, блоки контроля, диагностики и др.

Операционныйблок(ОБ).Предназначен для выполнения некоторого функционально полного набора логических и арифметических операций. Как правило, в его состав входят АЛУ, буферные регистры операндов, регистр результата (аккумулятор), регистр признаков и блок регистров общего назначения (РОН).

В АЛУ выполняются несколько простейших арифметических (сложение, вычитание) и поразрядных логических (И, ИЛИ, НЕ и др.) операций. Операции по обработке данных, для которых в ОБ отсутствуют аппаратные средства, выполняют программно с помощью процедур. Такие процедуры реализуются в виде последовательности простых операций ОБ, т.е. выполняются на более высоком уровне организации вычислительного процесса.

Кроме универсального АЛУ МП может содержать одно или несколько специализированных АЛУ. В качестве последних обычно используют блоки аппаратного умножения и деления, а также блоки для выполнения операций с плавающей точкой.

Важной составляющей ОБ современных МП является блок внутренней памяти, реализованный в виде набора программно доступных регистров, называемых регистрами общего назначения (РОН).

Время обращения к РОН меньше, чем к любым другим устройствам памяти, поэтому память на РОН называется сверхоперативной, а устройство, в виде которого она реализована, — сверхоперативным запоминающим устройством (СОЗУ).

Число, назначение и разрядность регистров блока РОН в различных МП могут существенно отличаться. В использовании РОН имеются два крайних подхода. При первом подходе, реализуемом в МП компании Motorola, почти все регистры МП выполняют абсолютно одинаковые функции, т.е. являются универсальными и взаимозаменяемыми. При втором подходе, характерном для МП компании Intel, многие регистры наряду с возможностью использования в качестве универсальных в некоторых командах могут выполнять специфические функции, закрепленные за этими регистрами.

В большинстве ранних моделей МП один из общих регистров выделялся в качестве главного регистра. Наделение главного регистра, называемого аккумулятором, или регистром результата, особыми функциями позволяло реализовать ОБ в виде одноадресного устройства. В таком ОБ один из исходных операндов арифметических и логических операций обязательно должен размешаться в аккумуляторе и в него же помешается результат. Другой операнд названных операций может находиться в памяти или РОН. Входные данные поступают в аккумулятор с внутренней шины МП, а аккумулятор, в свою очередь, может посылать данные на эту шину.

Функциональные возможности ОБ, содержащего аккумулятор, достаточно широки. С его помощью можно реализовать различные операции. Рассмотрим основные микрооперации, с использованием которых реализуется выполнение операций (команд).

• Содержимое любого РОН или ячейки памяти по внутренней шине данных может быть передано через аккумулятор в буферный регистр или напрямую в регистрсдвигатель.

• АЛУ обеспечивает выполнение арифметических и логических операций над содержимым регистра-сдвигателя и буферного регистра с записью результата в аккумулятор, а признаков — в регистр признаков.

• Из аккумулятора результат операции может быть передан в любой РОН или ячейку памяти.

• Операция сдвига содержимого любого РОН выполняется последовательно передачей слова из РОН в сдвигающийрегистр, сдвига этого слова и последующей записи преобразованного слова в тот же регистр РОН.

• Операции над словами с повышенной разрядностью реализуются путем программно последовательной обработки отдельных частей многоразрядных слов. Для обеспечения возможности обработки данных с разрядностью, превышающей разрядность АЛУ и регистров, в структуре ОБ, предусмотрены два дополнительных триггера: Trl и Тг2. С их помощью осуществляется запоминание сигналов арифметического переноса из АЛУ и выходного бита переноса регистра сдвига. Например, с помощью 8-разрядного МП сравнительно просто осуществляется арифметическая обработка 24-разрядных слов. Для этого выполняют три цикла обработки 8-разрядных частей этих слов.

• Признаки операций АЛУ (флаги), характеризующие результаты вычислений, запоминаются в одноименных флагахрегистра признаков. Типичными признаками являются: нулевой результат, наличие переноса, переполнение, четность, знак и некоторые другие.

Блокуправления. В процессе выполнения программы блок управления (см. рис. 4.1) координирует работу всех блоков МП и микропроцессорной системы в целом. С помощью блока управления формируются управляющие сигналы, необходимые для организации обмена информацией с внешними устройствами, и обеспечивается выборка команд программы из памяти. В целом блок управления выполняет следующие действия:

• считывает и запоминает текущую команду;

• формирует адрес следующей команды;

• реализует выполнение по тактам алгоритма поступившей команды;

• управляет обменом информацией с внешними устройствами по системной шине.

Блок управления состоит из регистра команд (РгК), дешифратора команд (ДшК) и блока формирования управляющих сигналов (БФУС). Управляющие сигналы с выходов БФУС поступают на управляющие входы других блоков МП, настраивая их на выполнение определенных микроопераций. В состав блока управления также включают программно доступные счетчик команд Instruction Pointer — указатель команд IP и указатель стека SP (Stack Pointer).

Выполнение любой команды реализуется как последовательность трех фаз: выборка, декодирование и выполнение.

Фазавыборки обеспечивает считывание очередной команды из памяти и пересылку ее в МП. Адрес считываемой команды определяется содержимым программного счетчика PC.

Код операции текущей команды запоминается в РгК. В фазедекодирования содержимое РгК с помощью ДшК преобразуется в управляющее слово. Схема синхронизации, используя это слово, вырабатывает совокупность сигналов, управляющих внутренними операциями МП и обменом информацией между МП и внешними устройствами.

После выборки и дешифрирования команды ОБ в декодированном виде получает информацию о том, какую операцию он должен выполнить, где в памяти расположены данные, куда следует направить результат операции и где расположена следующая команда. В фазевыполненияБФУС вырабатывает последовательности управляющих сигналов, обеспечивающих выполнение операции, заданной в команде.

Каждый блок за один такт может выполнить простейшую операцию (для регистра — это запись кода или выдача хранимого кода на выходы, для счетчика — запись кода в счетчик, прибавление или вычитание единицы, выдача хранимого кода, для мультиплексора — передача на выход сигнала с входа, определяемого управляющим кодом, для АЛУ — одна из простейших операций, которая выполняется на уровне регистровых передач: сложение, вычитание, сдвиг, реализация одной из поразрядных логических операций).

Элементарное действие, выполняемое в одном из узлов ОБ в течение одного такта, называется микрооперацией. В некоторые такты в различных узлах ОБ (регистрах, мультиплексорах, счетчиках и др.) одновременно могут выполняться несколько микроопераций. Настройка ОБ на выполнение одной из возможных микроопераций осуществляется с помощью сигналов, поступающих на его управляющие входы. Набор этих сигналов (вектор сигналов управления) вырабатывается БФУС.

Совокупность одновременно выполняемых микроопераций соответствует микрокоманде.

Команда в общем случае состоит из нескольких простейших действий и обычно выполняется за несколько тактов, т.е. требует для своего выполнения нескольких микрокоманд. Последовательность микрокоманд, обеспечивающая выполнение команды, называется микропрограммойкоманды.

Управляющий автомат, формирующий наборы управляющих сигналов для микропрограммой команды, называют микропрограммным автоматом (МПА). МПА подразделяют на аппарат с «жесткой» логикой управления и с «мягкой» логикой управления.

МПА с «жесткой» логикой управления представляется в виде конечного автомата (в сложных случаях используется сеть конечных автоматов). Алгоритм команды в МП с подобным МПА задан жестко соединениями схемы, поэтому список операций (система команд) МП является неизменным, и это не позволяет вносить какие-либо изменения в систему команд МП после его изготовления. Основным достоинством МПА с «жесткой» логикой управления является его высокое быстродействие. Такие устройства управления используются в большинстве однокристальных МП, отличительной характеристикой которых является то, что все элементы структуры МП выполнены на одном кристалле.

При реализации МПА с «мягкой» логикой управления используется типовая структура автомата с блоком памяти микропрограмм, который, как и основная память, имеет линейно-адресную организацию. В целом разработка УА МПА с «мягкой» логикой управления в значительной мере определяется разработкой микропрограмм команд.

В современных МП в зависимости от системы команд и сложности алгоритмов микропрограмм команд используются оба подхода при построении МПА. На уровне регистровых передач с помощью МПА независимо от типа управления непосредственно осуществляется интерпретация машинных команд программы и их выполнение. Именно поэтому уровень регистровых передач также называют микропрограммным уровнем организации вычислительных процессов ВМ.

Интерфейсныйблок. Предназначен для организации взаимодействия МП с памятью и устройствами ввода-вывода, расположенными на системной шине процессора, а также для обмена данными между ОБ и внутренними устройствами МП. Непосредственное подсоединение устройств ввода-вывода к МП осуществляется с помощью специальных схем сопряжения, которые называются интерфейсомвводавывода. В общем случае интерфейсный блок процессора должен выполнять следующие функции:

• формировать выходные сигналы на шинах адреса, данных и управления в режиме вывода;

• формировать выходные сигналы адреса и управления и считывать (воспринимать) сигналы с шины данных в режиме ввода;

• синхронизировать процессы внутри процессора и на системной шине;

• реализовывать стандартный для системной шины протокол обмена.

Системная шина объединяет сигналы шин данных, адреса и управления. Протокол обмена информацией по СШ определяет последовательности сигналов (временную диаграмму сигналов в шине), обеспечивающих правильную передачу информации между устройствами микропроцессорной системы. Взаимодействие по шине осуществляется за цикл шины. Длительность цикла шины может изменяться в зависимости от быстродействия внешних устройств.

Для согласования по быстродействию взаимодействующих при обмене по шине устройств используется принципквитирования - процессор, управляющий обменом, в каждом цикле ждет уведомления (квитанции) о том, что устройство на шине выполнило операции, связанные с обменом, т.е. выставило на шину данные при вводе либо восприняло данные с шины при выводе.

Программнаямодельмикропроцессора.Регистрыпроцессора

Итак, на ассемблере пишут:

• все, чтотребуетмаксимальнойскоростивыполнения: основные компоненты компьютерных игр, ядра операционных систем реального времени и просто критические участки программ;

• все, чтовзаимодействуетсвнешнимиустройствами: драйверы, программы, работающие напрямую с портами, звуковыми и видеоплатами;

• все, чтоиспользуетполностьювозможностипроцессора: ядра многозадачных операционных систем, DPMI-серверы и вообще любые программы, переводящие процессор в защищенный режим;

• все, чтополностьюиспользуетвозможностиоперационнойсистемы: вирусы и антивирусы, защиты от несанкционированного доступа, программы, обходящие эти защиты, и программы, защищающиеся от этих программ;

• имногоедругое.

Программная модель компьютера- часть компьютера оставлена видимой и доступной для программирования на этом языке, частью ПМ которой является программнаямодельмикропроцессора, которая содержит 32 регистра в той или иной мере доступных для использования программистом.

Регистры можно разделить на две большие группы: 16 пользовательских регистров; 16 системных регистров.

В программах на языке ассемблера регистры используются очень интенсивно. Большинство регистров имеют определенное функциональное назначение.

Пользовательскиерегистры

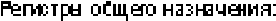

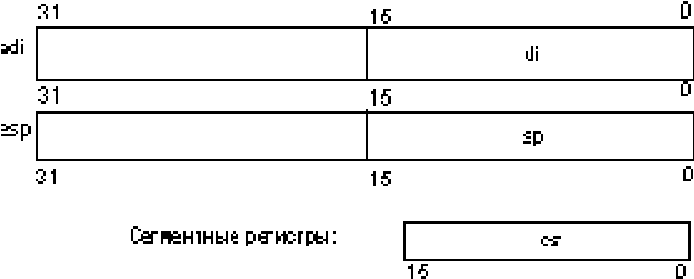

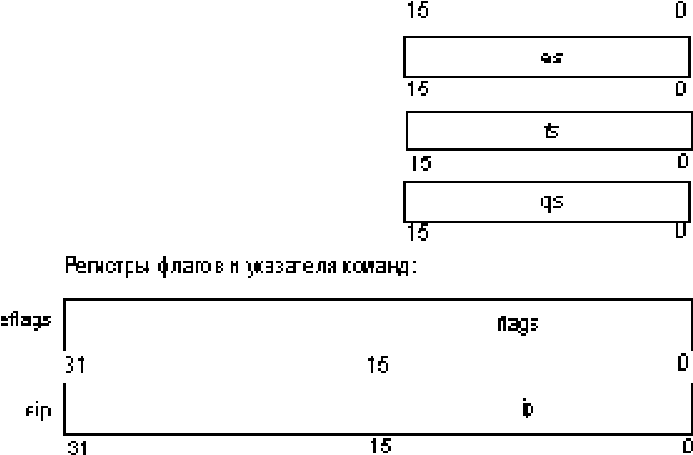

Как следует из названия, пользовательскими регистры называются потому, что программист может использовать их при написании своих программ. К этим регистрам относятся (рис. 1):

• восемь 32-битных регистров, которые могут использоваться программистами для хранения данных и адресов (их еще называют регистрами общего назначения (РОН)):

o eax/ax/ah/al; o ebx/bx/bh/bl; o edx/dx/dh/dl; o ecx/cx/ch/cl; o ebp/bp; o esi/si; o edi/di; o esp/sp.

• шесть регистров сегментов: cs, ds, ss, es, fs, gs; • регистры состояния и управления:

o регистр флагов eflags/flags; o регистр указателя команды eip/ip.

|

|

|

Рис. 1.Пользовательскиерегистрымикропроцессоров i486 и Pentium

Почему многие из этих регистров приведены с наклонной разделительной чертой? Нет, это не разные регистры — это части одного большого 32-разрядного регистра. Их можно использовать в программе как отдельные объекты. Так сделано для обеспечения работоспособности программ, написанных для младших 16-разрядных моделей микропроцессоров фирмы Intel, начиная с i8086. Микропроцессоры i486 и Pentium имеют в основном 32-разрядные регистры. Их количество, за исключением сегментных регистров, такое же, как и у i8086, но размерность больше, что и отражено в их обозначениях — они имеют приставку e (Extended).

Разберемся подробнее с составом и назначением пользовательских регистров.

Регистрыобщегоназначения

Все регистры этой группы позволяют обращаться к своим “младшим” частям (см. рис. 1). Рассматривая этот рисунок, заметьте, что использовать для самостоятельной адресации можно только младшие 16 и 8-битные части этих регистров. Старшие 16 бит этих регистров как самостоятельные объекты недоступны. Это сделано, как мы отметили выше, для совместимости с младшими 16-разрядными моделями микропроцессоров фирмы Intel.

Перечислим регистры, относящиеся к группе регистров общего назначения. Так как эти регистры физически находятся в микропроцессоре внутри арифметико-логического устройства (АЛУ), то их еще называют регистрамиАЛУ:

• eax/ax/ah/al (Accumulator register) — аккумулятор. Применяется для хранения промежуточных данных. В некоторых командах использование этого регистра обязательно;

• ebx/bx/bh/bl (Base register) — базовый регистр. Применяется для хранения базового адреса некоторого объекта в памяти;

• ecx/cx/ch/cl (Count register) — регистр-счетчик. Применяется в командах, производящих некоторые повторяющиеся действия. Его использование зачастую неявно и скрыто в алгоритме работы соответствующей команды.

К примеру, команда организации цикла loop кроме передачи управления команде, находящейся по некоторому адресу, анализирует и уменьшает на единицу значение регистра ecx/cx;

• edx/dx/dh/dl (Data register) — регистр данных. Так же, как и регистр eax/ax/ah/al, он хранит промежуточные данные. В некоторых командах его использование обязательно; для некоторых команд это происходит неявно.

Следующие два регистра используются для поддержки так называемых цепочечных операций, то есть операций, производящих последовательную обработку цепочек элементов, каждый из которых может иметь длину 32, 16 или 8 бит:

• esi/si (Source Index register) — индексисточника. Этот регистр в цепочечных операциях содержит текущий адрес элемента в цепочке-источнике;

• edi/di (Destination Index register) — индексприемника (получателя). Этот регистр в цепочечных операциях содержит текущий адрес в цепочке-приемнике.

В архитектуре микропроцессора на программно-аппаратном уровне поддерживается такая структура данных, как стек. Для работы со стеком в системе команд микропроцессора есть специальные команды, а в программной модели микропроцессора для этого существуют специальные регистры:

• esp/sp (Stack Pointer register) — регистр указателястека.

Содержит указатель вершины стека в текущем сегменте стека.

• ebp/bp (Base Pointer register) — регистр указателябазыкадрастека.

Предназначен для организации произвольного доступа к данным внутри стека.

Не спешите пугаться столь жесткого функционального назначения регистров АЛУ. На самом деле, большинство из них могут использоваться при программировании для хранения операндов практически в любых сочетаниях. Но, как мы отметили выше, некоторые команды используют фиксированные регистры для выполнения своих действий. Это нужно обязательно учитывать. Использование жесткого закрепления регистров для некоторых команд позволяет более компактно кодировать их машинное представление. Знание этих особенностей позволит вам при необходимости хотя бы на несколько байт сэкономить память, занимаемую кодом программы.

Сегментныерегистры

В программной модели микропроцессора имеется шесть сегментных регистров: cs, ss, ds, es, gs, fs.

Их существование обусловлено спецификой организации и использования оперативной памяти микропроцессорами Intel. Она заключается в том, что микропроцессор аппаратно поддерживает структурную организацию программы в виде трех частей, называемых сегментами. Соответственно, такая организация памяти называется сегментной.

Для того чтобы указать на сегменты, к которым программа имеет доступ в конкретный момент времени, и предназначены сегментныерегистры. Фактически, с небольшой поправкой, как мы увидим далее, в этих регистрах содержатся адреса памяти с которых начинаются соответствующие сегменты. Логика обработки машинной команды построена так, что при выборке команды, доступе к данным программы или к стеку неявно используются адреса во вполне определенных сегментных регистрах. Микропроцессор поддерживает следующие типы сегментов:

1. Сегменткода. Содержит команды программы. Для доступа к этому сегменту служит регистр cs (code segment register) — сегментныйрегистркода. Он содержит адрес сегмента с машинными командами, к которому имеет доступ микропроцессор (то есть эти команды загружаются в конвейер микропроцессора).

2. Сегментданных. Содержит обрабатываемые программой данные. Для доступа к этому сегменту служит регистр ds (data segment register) — сегментныйрегистрданных, который хранит адрес сегмента данных текущей программы.

3. Сегментстека. Этот сегмент представляет собой область памяти, называемую стеком. Работу со стеком микропроцессор организует по следующему принципу: последнийзаписанныйвэтуобластьэлементвыбираетсяпервым. Для доступа к этому сегменту служит регистр ss (stack segment register) — сегментныйрегистрстека, содержащий адрес сегмента стека.

4. Дополнительныйсегментданных. Неявно алгоритмы выполнения большинства машинных команд предполагают, что обрабатываемые ими данные расположены в сегменте данных, адрес которого находится в сегментном регистре ds. Если программе недостаточно одного сегмента данных, то она имеет возможность использовать еще три дополнительных сегмента данных. Но в отличие от основного сегмента данных, адрес которого содержится в сегментном регистре ds, при использовании дополнительных сегментов данных их адреса требуется указывать явно с помощью специальных префиксовпереопределениясегментов в команде. Адреса дополнительных сегментов данных должны содержаться в регистрах es, gs, fs (extension data segment registers).

Регистрысостоянияиуправления

В микропроцессор включены несколько регистров (см. рис. 1), которые постоянно содержат информацию о состоянии как самого микропроцессора, так и программы, команды которой в данный момент загружены на конвейер. К этим регистрам относятся:

• регистр флагов eflags/flags; • регистр указателя команды eip/ip.

Используя эти регистры, можно получать информацию о результатах выполнения команд и влиять на состояние самого микропроцессора. Рассмотрим подробнее назначение и содержимое этих регистров:

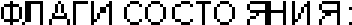

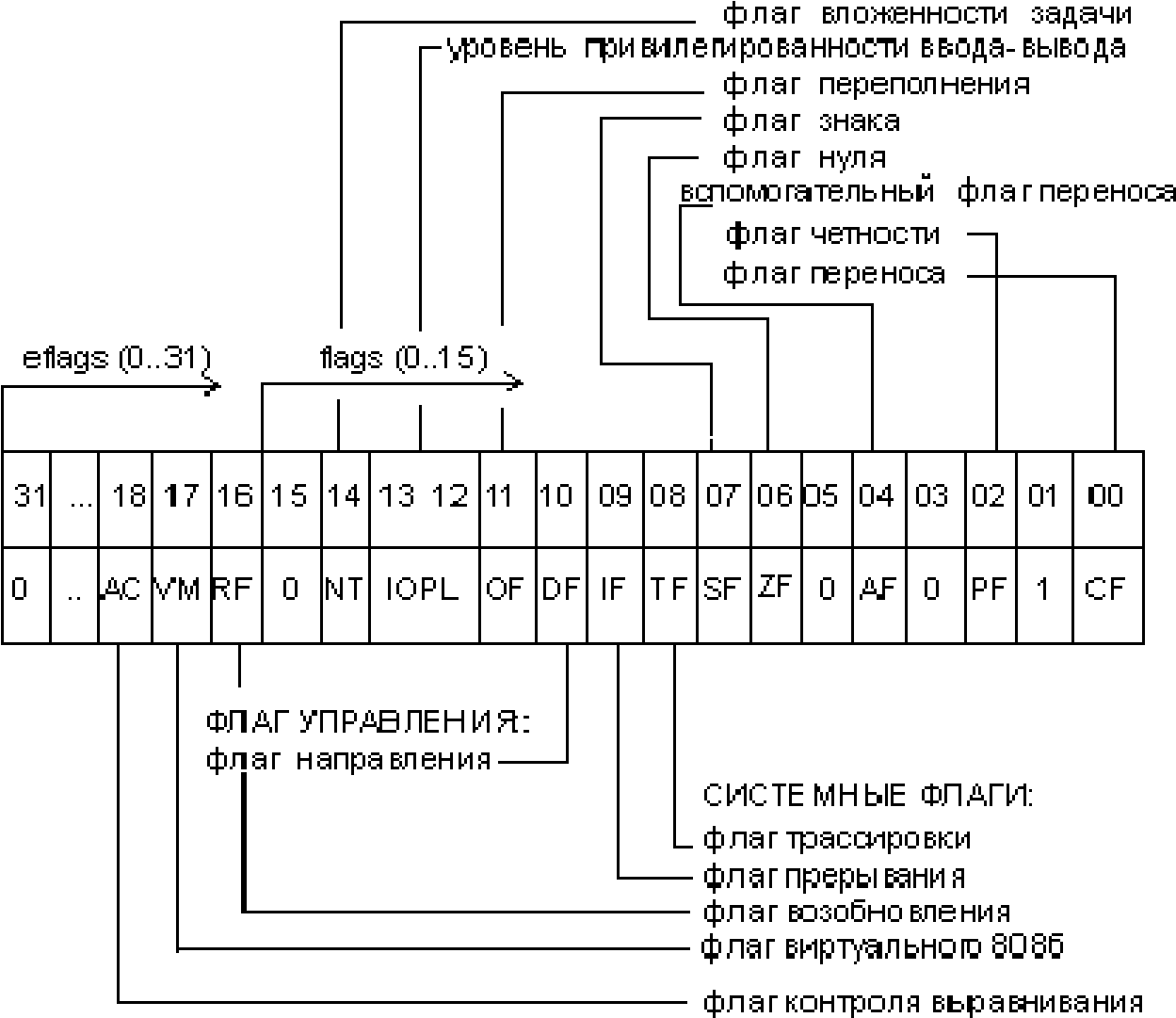

eflags/flags (flag register) — регистр флагов. Разрядность eflags/flags — 32/16 бит. Отдельные биты данного регистра имеют определенное функциональное назначение и называются флагами. Младшая часть этого регистра полностью аналогична регистру flags для i8086. На рис. 2 показано содержимое регистра eflags.

Рис. 2.Содержимоерегистра eflags

Исходя из особенностей использования, флаги регистра eflags/flags можно разделить на три группы:

• 8 флаговсостояния. Эти флаги могут изменяться после выполнения машинных команд. Флагисостояниярегистра eflags отражают особенности результата исполнения арифметических или логических операций. Это дает возможность анализировать состояние вычислительного процесса и реагировать на него с помощью команд условных переходов и вызовов подпрограмм. В табл. 1 приведены флаги состояния и указано их назначение;

• 1 флагуправления. Обозначается df (Directory Flag). Он находится в 10-м бите регистра eflags и используется цепочечными командами. Значение флага df определяет направление поэлементной обработки в этих операциях: от начала строки к концу (df = 0) либо наоборот, от конца строки к ее началу (df = 1). Для работы с флагом df существуют специальные команды: cld (снять флаг df) и std (установить флаг df). Применение этих команд позволяет привести флаг df в соответствие с алгоритмом и обеспечить автоматическое увеличение или уменьшение счетчиков при выполнении операций со строками;

• 5 системныхфлагов, управляющих вводом/выводом, маскируемыми прерываниями, отладкой, переключением между задачами и виртуальным режимом 8086. Прикладным программам не рекомендуется модифицировать без необходимости эти флаги, так как в большинстве случаев это приведет к прерыванию работы программы. В табл. 2 перечислены системные флаги, их назначение.

Таблица1.Флагисостояния

| Мнемоника Номер бита Флаг Содержание и назначение флага в eflags | |||

| cf | Флаг переноса (Carry Flag) | 1 — арифметическая операция произвела перенос из старшего бита результата. Старшим является 7, 15 или 31-й бит в | |

| зависимости от размерности операнда; 0 — переноса не было | |||

| Флаг паритета pf (Parity Flag) | 1 — 8 младших разрядов (этот флаг — только для 8 младших разрядов операнда любого размера) результата содержат четное 2 число единиц; 0 — 8 младших разрядов результата содержат нечетное число единиц | ||

| af | Вспомогательный флаг переноса (Auxiliary carry Flag) | Только для команд работающих с BCDчислами. Фиксирует факт заема из младшей тетрады результата: 1 — в результате операции сложения был произведен перенос из разряда 3 в старший разряд или при вычитании был заем в разряд 3 младшей тетрады из значения в старшей тетраде; 0 — переносов и заемов в(из) 3 разряд(а) младшей тетрады результата не было | |

| Флаг нуля (Zero zf Flag) | 1 — результат нулевой; 6 0 — результат ненулевой | ||

| Флаг знака sf (Sign Flag) | Отражает состояние старшего бита результата (биты 7, 15 или 31 для 8, 16 или 7 32-разрядных операндов соответственно): 1 — старший бит результата равен 1; 0 — старший бит результата равен 0 | ||

| of | Флаг переполнения (Overflow Flag) | Флаг of используется для фиксирования факта потери значащего бита при арифметических операциях: 1 — в результате операции происходит перенос (заем) в(из) старшего, знакового бита результата (биты 7, 15 или 31 для 8, 16 или 32-разрядных операндов соответственно); 0 — в результате операции не происходит переноса (заема) в(из) старшего, знакового бита результата | |

| Уровень Привилегий iopl ввода-вывода (Input/Output Privilege Level) | Используется в защищенном режиме работы микропроцессора для контроля доступа к 12, 13 командам ввода-вывода в зависимости от привилегированности задачи | ||

| флажок вложенности nt задачи (Nested Task) | Используется в защищенном режиме работы 14 микропроцессора для фиксации того факта, что одна задача вложена в другую |

Таблица2.Системныефлаги

| Номер Мнемоника Флаг бита в Содержание и назначение флага eflags | |||

| tf | Флаг трассировки | Предназначен для организации пошаговой работы микропроцессора. | |

| (Trace Flag) 1 — микропроцессор генерирует прерывание с номером 1 после выполнения каждой машинной команды. Может использоваться при отладке программ, в частности отладчиками; 0 — обычная работа | |||

| Предназначен для разрешения или запрещения Флаг (маскирования) аппаратных прерываний прерывания if 9 (прерываний по входу INTR). (Interrupt enable 1 — аппаратные прерывания разрешены; Flag) 0 — аппаратные прерывания запрещены | |||

| Флаг Используется при обработке прерываний от rf возобновления 16 регистров отладки. (Resume Flag) | |||

| Признак работы микропроцессора в режиме Флаг виртуального 8086. виртуального 1 — процессор работает в режиме виртуального vm 17 (Virtual 8086 8086; Mode) 0 — процессор работает в реальном или защищенном режиме | |||

| Предназначен для разрешения контроля выравнивания при обращениях к памяти. Используется совместно с битом am в системном Флаг контроля регистре cr0. К примеру, Pentium разрешает выравнивания размещать команды и данные с любого адреса. ac 18 (Alignment Если требуется контролировать выравнивание Check) данных и команд по адресам кратным 2 или 4, то установка данных битов приведет к тому, что все обращения по некратным адресам будут возбуждать исключительную ситуацию |

eip/ip (Instraction Pointer register) — регистр-указателькоманд. Регистр eip/ip имеет разрядность 32/16 бит и содержит смещение следующей подлежащей выполнению команды относительно содержимого сегментного регистра cs в текущем сегменте команд. Этот регистр непосредственно недоступен программисту, но загрузка и изменение его значения производятся различными командами управления, к которым относятся команды условных и безусловных переходов, вызова процедур и возврата из процедур. Возникновение прерываний также приводит к модификации регистра eip/ip.

Системакоманд

Система команд является одной из важнейших архитектурных характеристик процессора и ВМ в целом. Она определяет совокупность операций, реализуемых процессором. В понятие система команд входят:

• форматы команд и обрабатываемых данных; • список команд, их функциональное назначение;

• способы адресации данных.

У современных мощных процессоров количество команд достигает нескольких сотен. В то же время существуют процессоры с сокращенным набором команд (так называемые RISC-процессоры), в которых за счет максимального сокращения количества команд достигается увеличение эффективности и скорости их выполнения.

Первые RISС-процессоры были разработаны в начале 1980-х годов в

Стэнфордском и Калифорнийском университетах США. Они выполняли небольшой (50 − 100) набор команд, тогда как обычные CISC (Сomplex Instruction Set computer) выполняли 100—200.

Частотаиспользованиянаиболееупотребляемыхсемействах8бкомандМПсемействах86

| Команда | Доля (частота) использования при целочисленных вычислениях, % |

| I. Загрузка | |

| 2. Условные переходы | |

| 3. Сравнение | |

| 4. Запоминание | |

| 5. Сложение | |

| 6. Логическое И | |

| 7. Вычитание | |

| 8. Пересылки регистр-регистр | |

| 9. Вызов подпрограмм | |

| 10. Возврат из подпрограмм | |

| Всего |

Данные табл. 4.1 наглядно иллюстрируют неравномерность использования различных команд в типовых программах. Это свойство системы команд было предпосылкой для развития МП с RISC-архитектурой (Reduced Instruction Set Computer — компьютер с сокращенным набором команд). Идея заключалась в упрощении блока управления за счет сокращения списка команд и использовании освобождающихся при этом ресурсов кристалла МП для организации более быстрого исполнения оставшихся команд. МП с расширенным списком команд соответственно относят к CISC-архитектуре (Complex Instruction Set Computer — компьютер со сложной системой команд).

CISC- и RISC-процессоры характеризуются различными показателями производительности. Оба типа процессоров обеспечивают достижение максимальных показателей производительности, используя для этого особенности собственной системы команд. Для повышения производительности (уменьшения числа тактов затрачиваемых на выполнение программы), необходимо уменьшать либо число команд в программе, либо среднее время выполнения команды (число тактов). Первая возможность наиболее полно используется в CISC-архитектуре процессоров, а вторая в RISC-архитектуре.

CISC (англ. Complex Instruction Set Computing) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

− Нефиксированным значением длины команды.

− Арифметические действия, кодируется в одной инструкции.

− Небольшим числом регистров, каждый из которых выполняет строго определённую функцию.

Типичными представителями являются процессоры на основе x86 команд (исключая современные Intel Pentium 4, Pentium D, Core, AMD Athlon, Phenom которые являются гибридными).

Формально, все х86-процессоры являлись CISC-процессорами, однако новые процессоры, начиная с Intel486DX, являются CISC-процессорами с RISC-ядром. Они непосредственно перед исполнением преобразуют CISC-инструкции процессоров x86 в более простой набор внутренних инструкций RISC.

RISC (англ. Reduced Instruction Set Computing) — вычисления с сокращённым набором команд.

Это концепция проектирования процессоров, которая во главу ставит более компактные и простые инструкции выполняются быстрее. Простая архитектура позволяет удешевить процессор, поднять тактовую частоту, а также распараллелить исполнение команд между несколькими блоками исполнения (т.н. суперскалярные архитектуры процессоров).

1. Одинаковая длина команд. Это облегчает их выборку из памяти. В отличие от CISC-процессоров RISC-процессоры не требуют выборки дополнительных слов команды. Все команды считы-ваются за один такт. В современных RISC-процессорах длина команды равна 32 бит.

2. Сокращен набор действий над операндами, размещенными в памяти. В RISCпроцессорах не используются сложные адресные вычисления и множественные ссылки. Простые способы адресации памяти обеспечивают быстрый доступ к операндам в памяти. Обработка данных, реализуемая при выполнении команд RISC, никогда не совмещается с операциями чтения (записи) памяти подобно тому, как это делается во многих командах CISC. Обмен операндами между памятью и регистрами выполняется специальными командами загрузки и запоминания. Большое число регистров блока РОН позволяет уменьшить число обращений к памяти.

3. Все вычислительные операции выполняются над данными, находящимися только в РОН. Так как регистров много, то все скалярные переменные и даже небольшие массивы переменных чаще всего размещаются в регистрах. Арифметические и логические команды являются трехадресными. Формат этих команд включает код операции и адреса регистров источников и приемника. Использование простых команд упрощает реализацию их конвейерной обработки. В среднем команды RISC выполняются за один такт.

4. Относительно простые схемы управления. Отсутствие микропрограмм внутри самого процессора. То, что в CISC процессоре исполняется микропрограммами, в RISC процессоре исполняется как обыкновенный (хотя и помещенный в специальное хранилище) машинной код, не отличающийся принципиально от кода ядра ОС и приложений.

В RISC-процессорах повышение производительности достигалось за счет аппаратных решений, обеспечивающих снижение числа обращений к оперативной памяти. Отличительной особенностью этих процессоров является большой набор РОН. С их помощью делается попытка свести все пересылки к типу регистр-регистр.

Группыкоманд

В общем случае система команд процессора включает в себя следующие четыре основные группы команд:

− командыпересылки данных;

− арифметическиекоманды;

− логическиекоманды;

− командыпереходов.

Командыпересылки данных не требуют выполнения никаких операций над операндами. Операнды просто пересылаются (точнее, копируются) из источника (Source) в приемник (Destination). Источником и приемником могут быть внутренние регистры процессора, ячейки памяти или устройства ввода/вывода. АЛУ в данном случае не используется.

Арифметическиекоманды выполняют операции сложения, вычитания, умножения, деления, увеличения на единицу (инкрементирования), уменьшения н

Дата добавления: 2016-06-15; просмотров: 3605;