АЦП последовательного счета.

АЦП последователного счета осуществляют сравнение входной аналоговой величины с суммой значений нескольких одинаковых мер. Момент равенства этих величин фиксируется безгистерезисным компаратором. Схема одного из вариантов такого АЦП, получившего название развертывающего или циклического, представлена на рис. 10.5,а. На вход компаратора DA1 поступают два аналоговых сигнала – входное напряжение Uвх схемы и выходное напряжение Uвых.ЦАП с ЦАП DА2 в виде нормированных квантованных уровней. Компаратор устанавливает соотношение мгновенных амплитуд этих напряжений. Если Uвх>Uвых.ЦАП, на выходе компаратора устанавливается уровень напряжения логической единицы, если Uвх£Uвых.ЦАП, то на выходе компаратора устанавливается напряжение логического нуля. Единичный уровень сигнала с выхода компаратора, поступая на вход вентиля И DD1, разрешает передачу на счетный вход счетчика DD2 тактовых импульсов с генератора GN. В противном случае, если на выходе компаратора логический нуль, счетные импульсы на вход счетчика не проходят. Таким образом, подсчет импульсов осуществляется только при условии Uвх>Uвых.ЦАП.

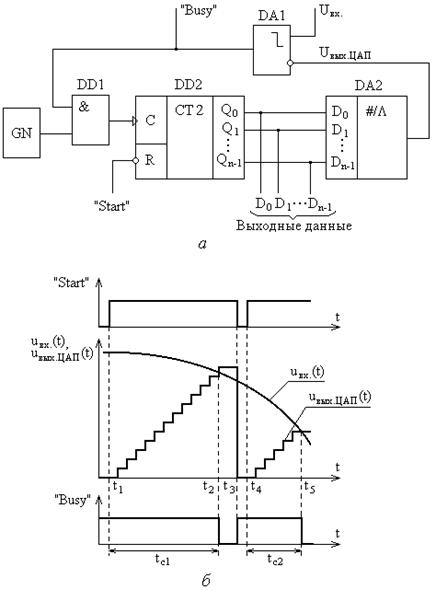

Рис. 10.5. Схема (а) и временная диаграмма работы (б) развертывающего АЦП.

В исходном состоянии на входе «Start» схемы присутствует уровень логического нуля (рис.10.5,б). Данный уровень является активным для входа R установки счетчика в нулевое состояние. В результате нулевой двоичный код с выхода счетчика поступает на вход ЦАП, на выходе которого устанавливается нулевое напряжение Uвых.ЦАП. Если входное напряжение Uвх схемы больше нуля, то выполняется условие Uвх>Uвых.ЦАП и счетные импульсы проходят на вход счетчика. При этом счетчик удерживается в нулевом состоянии нулевым значением сигнала «Start». Для запуска преобразования в момент времени t1 на вход «Start» подается уровень логической единицы. Начинается подсчет импульсов с тактового генератора. С каждым текущим импульсом на выходе ЦАП будет формироваться потенциал следующего квантованного уровня. Как только выходное напряжение ЦАП достигнет или превысит амплитуду входного аналогового сигнала схемы, т.е. выполнится условие Uвх£Uвых.ЦАП, компаратор переключится в нулевое состояние, элемент И закроется и подсчет тактовых импульсов прекратится. На выходе счетчика зафиксируется выходной код, соответствующий величине Uвх. На временной диаграмме этому соответствует момент времени t2. Время преобразования tc1=t2-t1.

Для приведения АЦП в исходное состояние необходимо счетчик DD2 нулевым сигналом «Start» сбросить в нуль (момент времени t3). На выходе ЦАП сформируется нулевое выходное напряжение, выполнится условие Uвх>Uвых.ЦАП, но под действием нулевого уровня сигнала «Start» на выходе счетчика будет сохраняться нулевой двоичный код. Для запуска следующего преобразования на вход «Start» необходимо снова подать уровень логической единицы (момент времени t4). Процесс преобразования повторится. Как только в очередной раз выполнится условие Uвх£Uвых.ЦАП (момент времени t5), преобразование завершится. Время преобразования в этом случае tc2=t5-t4.

Из временной диаграммы очевидно, что время преобразования tc1 и tc2 различно и зависит от частоты следования тактирующих импульсов и формы входного аналогового сигнала. Поэтому для синхронизации работы АЦП с другими устройствами выход компаратора используется еще и как управляющий сигнал «Busy». Этот сигнал является признаком завершения преобразования. Пока сигнал «Busy» имеет единичный уровень, АЦП выполняет преобразование, на выходах D0…Dn-1 присутствуют промежуточные некорректные коды. Считывание информации с этих выходов следует производить только после того, как сигнал «Busy» примет нулевое значение, т.е. после завершения преобразования.

Недостаток развертывающего АЦП заключается в его низком быстродействии, поскольку в процессе каждого преобразования суммирование нормированных мер начинается с нулевого значения. Этого недостатка лишены следящие или нециклические АЦП. Принцип их работы основан на том, что суммирование мер с нулевого значения осуществляется только при первом преобразовании. В дальнейшем следящий АЦП лишь корректирует выходной код в зависимости от входного аналогового сигнала. Схема следящего АЦП приведена на рис. 10.6,а.

Рис. 10.6. Схема (а) и временная диаграмма работы (б) следящего АЦП.

Особенностью схемы является использование реверсивного счетчика DD4. Счетные импульсы на вход счетчика подаются через ключевые вентили И DD1 и DD2. Если выполняется условие Uвх>Uвых.ЦАП, то единичным сигналом с выхода компаратора элемент DD1 пропускает счетные импульсы на вход «+1» счетчика. На вход элемента DD2 в этом случае через инвертор DD3 подается логический ноль, в результате чего на выходе DD2 также формируется логический ноль, который подается на вход «-1» счетчика. Счетчик осуществляет положительный счет. Если же выполняется условие Uвх£Uвых.ЦАП, то закрывается элемент DD1, инвертором DD3 открывается элемент DD2, через который счетные импульсы подаются на вход «-1» счетчика, и счетчик начинает выполнять операцию отрицательного счета.

Пока на входе «Start» присутствует нулевой уровень сигнала, также как и в случае с развертывающим АЦП, на выходе ЦАП DA2 удерживается нулевой потенциал (рис.10.6,б). При этом выполняется условие Uвх>Uвых.ЦАП и счетные импульсы подаются на вход «+1» счетчика. Как только на вход «Start» поступает логическая единица, разрешается положительный счет (момент времени t1). Счет будет продолжаться до тех пор, пока выходное напряжение с ЦАП, пропорциональное коду подсчитанных импульсов, не достигнет значения амплитуды входного аналогового сигнала (момент времени t2). При этом выполнится условие Uвх£Uвых.ЦАП и счетчик начнет операцию отрицательного счета. Отрицательный счет будет продолжаться, пока вновь не выполнится условие Uвх>Uвых.ЦАП и счетчик не вернется к положительному счету. Таким образом, схема АЦП будет постоянно отслеживать амплитуду входного аналогового сигнала и пропорционально ей формировать выходной код D0…Dn-1.

Врем преобразования tc=t2-t1 обусловлено процессом только самого первого развертывающего преобразования и зависит от амплитуды входного сигнала. Для возможности синхронизации с другими устройствами в схеме следящего АЦП также предусмотрен управляющий сигнал «Busy». Сигнал с выхода компаратора в зависимости от направления счета постоянно будет менять свое значение с единицы на ноль. Для фиксации момента окончания первого следящего преобразования (момент времени t2) в виде нулевого значения сигнала «Busy» и удержания его в дальнейшем в схеме АЦП предусмотрен D-триггер DD5 с динамическим управлением и статическими входами асинхронной установки в ноль и единицу. Для формирования единичного уровня сигнала «Busy» в момент начала преобразования в D-триггер по переднему фронту сигнала «Start» записывается логическая единица с входа D. Эта единица будет сохраняться до тех пор, пока на выходе компаратора не сформируется нулевой потенциал, являющийся признаком завершения первого развертывающего преобразования. Этот ноль поступит на инверсный асинхронный вход сброса  триггера и установит его в нулевое состояние. На выходе триггера сформируется нулевой уровень сигнала «Busy». В дальнейшем это состояние триггера будет оставаться неизменным по причине отсутствия каких-либо воздействий, устанавливающих его в единичное состояние. Таким образом, сигнал «Busy» будет выполнять функцию признака завершения первого развертывающего преобразования.

триггера и установит его в нулевое состояние. На выходе триггера сформируется нулевой уровень сигнала «Busy». В дальнейшем это состояние триггера будет оставаться неизменным по причине отсутствия каких-либо воздействий, устанавливающих его в единичное состояние. Таким образом, сигнал «Busy» будет выполнять функцию признака завершения первого развертывающего преобразования.

Если счетчик находится в режиме отрицательного счета, то на входе  D-триггера будет присутсвовать активный нулевой потенциал. Если теперь подать на вход «Start» нулевое значение сигнала для приведения схемы АЦП в исходное состояние, этот нулевой сигнал сброса с входа

D-триггера будет присутсвовать активный нулевой потенциал. Если теперь подать на вход «Start» нулевое значение сигнала для приведения схемы АЦП в исходное состояние, этот нулевой сигнал сброса с входа  D-триггера снимется с некоторой задержкой, обусловленной временем срабатывания элементов (в порядке очередности их срабатывания) DD4, DA2 и DA1. Поэтому сигнал «Start» на динамический вход C D-триггера для установки на его выходе сигнала «Busy» необходимо подавать после того, как будет снят логический ноль со статического входа

D-триггера снимется с некоторой задержкой, обусловленной временем срабатывания элементов (в порядке очередности их срабатывания) DD4, DA2 и DA1. Поэтому сигнал «Start» на динамический вход C D-триггера для установки на его выходе сигнала «Busy» необходимо подавать после того, как будет снят логический ноль со статического входа  этого триггера, т.е. с некоторой задержкой. Для этих целей служит схема задержки DL, реализовать которую можно на интегрирующей RC-цепи с постоянной времени, равной суммарному времени задержки указанных выше элементов.

этого триггера, т.е. с некоторой задержкой. Для этих целей служит схема задержки DL, реализовать которую можно на интегрирующей RC-цепи с постоянной времени, равной суммарному времени задержки указанных выше элементов.

Важно отметить, что скорость изменения входного аналогового сигнала, подаваемого на следящий АЦП, не должна превышать некоторого предельного значения, обусловленного быстродействием АЦП и частотой следования тактовых импульсов с выхода генератора GN. В противном случае АЦП не будет успевать отслеживать изменение входного сигнала.

Интегрирующие АЦП.

В основу метода интегрирующего преобразования положен принцип сравнения значений интегралов амплитуд входного аналогового сигнала uвх(t) в определенных пределах и опорного напряжения UREF в тех пределах, при которых разница этих двух интегралов дает нулевой результат. Нахождение каждого такого интеграла реализуется за один такт преобразования, т.е. за два такта в сумме для обоих интегралов. Поэтому такой метод преобразования часто называют методом двухтактного интегрирования. В качестве результата аналого-цифрового преобразования принимается двоичный код X, пропорциональный пределам интегрирования опорного напряжения. Математически это можно записать:

.

.

Двоичный код может быть получен путем заполнения интервала Dtинт тактовыми импульсами и подсчета их двоичным счетчиком. Для определенности пределов интегрирования такими же импульсами заполняется и интервал времени t2-t1. Этот интервал должен быть одинаковым при каждом преобразовании и обычно выбирается соответствующим модулю счета Kсч используемого двоичного счетчика.

Вариант схемы АЦП с двухтактным интегрированием представлена на рис. 10.7,а. Можно отметить отсутствие в приведенной схеме ЦАП, поскольку обе сравниваемые величины uвх(t) и UREF представлены в аналоговой форме. Компаратор DA3 выполнен так, что когда выходное напряжение с интегратора, реализованного на операционном усилителе DA2, резисторе R и конденсаторе C, равно нулю, т.е. когда Uвых.DA2=0, то на его выходе устанавливается уровень логического нуля. Если выходное напряжение интегратора меньше нуля Uвых.DA2<0, то на выходе компаратора устанавливается логическая единица.

В исходном состоянии триггеры DD1 и DD2 сброшены в ноль и ключи SW1 и SW2 разомкнуты. На выходе вентиля ИЛИ DD4 формируется ноль, который инвертируется в единицу инвертором DD5, замыкая тем самым ключ SW3. Это обеспечивает нулевое начальное напряжение на конденсаторе C и нулевое напряжение на выходе интегратора. Выполняется условие Uвых.DA2=0, на выходе компаратора формируется нулевой логический уровень, который закрывает стробирующий вентиль И DD6, в результате чего импульсы с выхода генератора GN на счетчик DD2 на проходят. Преобразование начинается с подачи на вход «Start» схемы короткого единичного импульса (момент времени t1) (рис.10.7,б). По этому импульсу триггер DD1 устанавливается в единицу и замыкается ключ SW2. На выходе вентиля ИЛИ DD4 также формируется единица, которая инвертируется инвертором DD5 в ноль и размыкается ключ SW3. В результате на вход интегратора подается амплитуда входного напряжения. Если изменение входного напряжения uвх(t) отсутствует или происходит со временем, значительно превышающим постоянную времени t=RC, то можно считать входное напряжения постоянным в масштабе периода интегрирования. В этом случае на выходе интегратора напряжение начинает линейно убывать. Выполняется условие Uвых.DA2<0, на выходе компаратора формируется логическая единица, которая открывает элемент И DD6. Тактовые импульсы с выхода генератора GN начинают поступать на счетчик DD7.

После того, как будут подсчитаны Ксч импульсов, на выходе счетчика сформируется единичный уровень сигнала переноса P, который сбросит триггер DD1 в ноль и установит триггер DD2 в еднинцу. В результате ключ SW2 закроется, а SW1 откроется (момент времени t2). На выходе вентиля ИЛИ DD4 будет сохраняться единица, на выходе инвертора DD5 - ноль, и ключ SW3 будет оставаться размкнутым. Напряжение на выходе интегратора в момент времени t2 определяется из формулы:

.

.

Поскольку интегрирование входного напряжения прекращается сигналом переноса P счетчика, то время интегрирования Тинт получается постоянным, независящим от амплитуды входного напряжения, а зависящим только от частоты следования тактовых импульсов и Ксч счетчика.

Рис. 10.7. Схема (а) и временная диаграмма работы (б) двухтактного интегрирующего АЦП.

С открытием ключа SW1 на вход схемы начинает подаваться опорное напряжение UREF через аналоговый инвертор DA1, т.е. на вход интегратора оно поступает с отрицательной полярностью. Напряжение UREF можно формировать изначально отрицательной полярности, тогда необходимость в инверторе DA1 отпадет. Напряжение на выходе интегратора не может измениться скачком, поэтому оно начинает линейно возрастать. В момент времени t3 оно достигнет нулевого уровня Uвых.DA2=0, на выходе компаратора DA3 сформируется уровень логического нуля, который закроет элемент И DD6, подача счетных импульсов на счетчик прекратится. Одновременно через инвертор DD3 сбросится в ноль триггер DD2 и закроется ключ SW1. На выходах обоих триггеров будут присутствовать нули, которые поступят на входы вентиля ИЛИ DD4, в результате чего на его выходе сформируется ноль. Этот ноль проинвертируется инвертором DD5 и откроется ключ SW3 для разряда конденсатора и приведения его в исходное состояние. На выходе счетчика зафиксируется двоичный код, пропорциональный входному напряжению. Для выходного напряжения интегратора в момент времени t3 можно записать:

или

откуда

.

.

Таким образом, количество подсчитанных двоичным счетчиком тактовых импульсов в период  и сформированный цифровой код Х прямо пропорционален входному аналоговому напряжению. Для облегчения синхронизации работы с другими устройствами в схеме рассмотренного АЦП также предусмотрен управляющий выходной сигнал «Busy». Поскольку весь процесс двухтактного преобразования сопровождается логическим нулем на выходе вентиля ИЛИ DD4, его выход можно использовать и как цепь сигнала «Busy».

и сформированный цифровой код Х прямо пропорционален входному аналоговому напряжению. Для облегчения синхронизации работы с другими устройствами в схеме рассмотренного АЦП также предусмотрен управляющий выходной сигнал «Busy». Поскольку весь процесс двухтактного преобразования сопровождается логическим нулем на выходе вентиля ИЛИ DD4, его выход можно использовать и как цепь сигнала «Busy».

Ключ SW2 коммутирует только положительный потенциал входного напряжения Uвх. Поэтому его можно реализовать на основе n-канального полевого транзистора с индуцированным каналом, как это делалось в схемах ЦАП. Ключи SW1 и SW3 коммутируют отрицательные потенциалы (-UREF и -Uвых.DA2). Для реализации этих ключей необходимо использовать аналогичные транзисторы, но с каналом p-типа. Для управления такими транзисторами на их затворы необходимо подавать сигналы логических единиц с отрицательными потенциалами. Для формирования отрицательных уровней напряжения в схеме можно использовать двуполярный источник питания и инверторы полярности напряжений.

АЦП двухтактного интегрирования, также как и АЦП последовательного счета, обладает не высоким быстродействием, поскольку выходной код формируется процессом подсчета тактовых импульсов, длительность которого зависит от амплитуды входного аналогового сигнала. Часто интегрирующие АЦП по этой причине относят к АЦП последовательного счета. Между тем двухтактный интегрирующий АЦП обладает существенным достоинством. По причине интегрирования входного сигнала осуществляется фильтрация высокочастотных помех. Кроме того, период интегрирования Tинт входного напряжения можно выбрать таким, чтобы почти полностью исключить помехи с частотами, кратными 1/Tинт. Для исключения помех, вызванных наводками бытовой сети с частотой 50 Гц, период интегрирования должен выбираться кратным значению 1/50 с. Отсюда следует, что интегрирующие АЦП целесообразно применять для оцифровки аналоговых сигналов, характеризующихся сверхнизкими частотами.

Дата добавления: 2022-02-05; просмотров: 725;