АЦП многотактного интегрирования

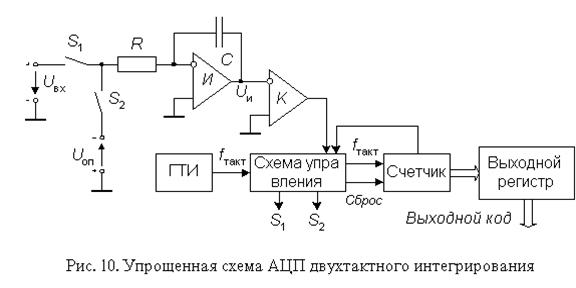

Упрощенная схема АЦП, работающего в два основных такта (АЦП двухтактного интегрирования), приведена на рис. 10.

Рисунок 5.18. Упрощенная схема АЦП двухкратного интегрирования.

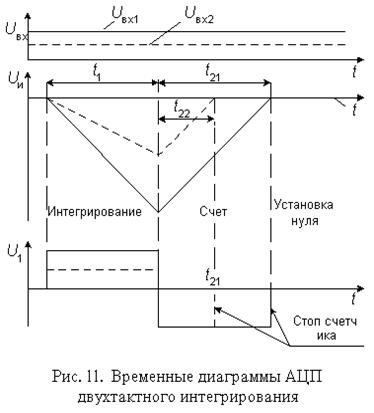

Преобразование проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ S1 замкнут, а ключ S2 разомкнут. Интегратор И интегрирует входное напряжение Uвх. Время интегрирования входного напряжения t1 постоянно; в качестве таймера используется счетчик с коэффициентом пересчета Kсч, так что

(6)

(6)

К моменту окончания интегрирования выходное напряжение интегратора составляет

(7)

(7)

где Uвх.ср. - среднее за время t1 входное напряжение. После окончания стадии интегрирования ключ S1 размыкается, а ключ S2 замыкается и опорное напряжение Uоп поступает на вход интегратора. При этом выбирается опорное напряжение, противоположное по знаку входному напряжению. На стадии счета выходное напряжение интегратора линейно уменьшается по абсолютной величине, как показано на рис. 11.

Рисунок 5.19. Временные диаграммы АЦП двухтактного интегрирования.

Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. При этом компаратор К переключается и счет останавливается. Интервал времени, в котором проходит стадия счета, определяется уравнением

(8)

(8)

Подставив значение Uи(t1) из (7) в (8) с учетом того, что

(9)

(9)

где n2 - содержимое счетчика после окончания стадии счета, получим результат

(10)

(10)

Из этой формулы следует, что отличительной особенностью метода многотактного интегрирования является то, что ни тактовая частота, ни постоянная интегрирования RC не влияют на результат. Необходимо только потребовать, чтобы тактовая частота в течение времени t1+t2 оставалась постоянной. Это можно обеспечить при использовании простого тактового генератора, поскольку существенные временные или температурные дрейфы частоты происходят за время несопоставимо большее, чем время преобразования.

При выводе выражений (6)...(10) мы видели, что в окончательный результат входят не мгновенные значения преобразуемого напряжения, а только значения, усредненные за время t1. Поэтому переменное напряжение ослабляется тем сильнее, чем выше его частота.

Сигма-дельта АЦП

АЦП многотактного интегрирования имеют ряд недостатков. Во-первых, нелинейность переходной статической характеристики операционного усилителя, на котором выполняют интегратор, заметным образом сказывается на интегральной нелинейности характеристики преобразования АЦП высокого разрешения. Для уменьшения влияния этого фактора АЦП изготавливают многотактными. Например, 13-разрядный AD7550 выполняет преобразование в четыре такта. Другим недостатком этих АЦП является то обстоятельство, что интегрирование входного сигнала занимает в цикле преобразования только приблизительно третью часть. Две трети цикла преобразователь не принимает входной сигнал. Это ухудшает помехоподавляющие свойства интегрирующего АЦП. В-третьих, АЦП многотактного интегрирования должен быть снабжен довольно большим количеством внешних резисторов и конденсаторов с высококачественным диэлектриком, что значительно увеличивает место, занимаемое преобразователем на плате и, как следствие, усиливает влияние помех.

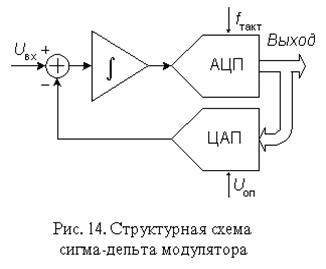

Эти недостатки во многом устранены в конструкции сигма-дельта АЦП (в ранней литературе эти преобразователи назывались АЦП с уравновешиванием или балансом зарядов). Своим названием эти преобразователи обязаны наличием в них двух блоков: сумматора (обозначение операции - S) иинтегратора (обозначение операции - D ). Один из принципов, заложенных в такого рода преобразователях, позволяющий уменьшить погрешность, вносимую шумами, а следовательно увеличить разрешающую способность - это усреднение результатов измерения на большом интервале времени.

Рисунок 5.20. Структурная схема сигма – дельта модулятора

Основные узлы АЦП - это сигма-дельта модулятор и цифровой фильтр. Схема n-разрядного сигма-дельта модулятора первого порядка приведена на рис. 14. Работа этой схемы основана на вычитании из входного сигнала Uвх(t) величины сигнала на выходе ЦАП, полученной на предыдущем такте работы схемы. Полученная разность интегрируется, а затем преобразуется в код параллельным АЦП невысокой разрядности. Последовательность кодов поступает на цифровой фильтр нижних частот.

Порядок модулятора определяется численностью интеграторов и сумматоров в его схеме. Сигма-дельта модуляторы N-го порядка содержат N сумматоров и N интеграторов и обеспечивают большее соотношение сигнал/шум при той же частоте отсчетов, чем модуляторы первого порядка. Примерами сигма-дельта модуляторов высокого порядка являются одноканальный AD7720 седьмого порядка и двухканальный ADMOD79 пятого порядка.

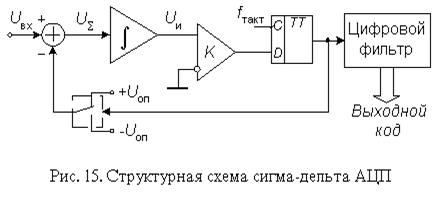

Рисунок 5.21. Структурная схема сигма-дельта АЦП

Наиболее широко в составе ИМС используются однобитные сигма-дельта модуляторы, в которых в качестве АЦП используется компаратор, а в качестве ЦАП - аналоговый комутатор (рис. 15). Принцип действия пояснен в табл. 2 на примере преобразования входного сигнала, равного 0,6 В, при Uоп=1 В. Пусть постоянная времени интегрирования интегратора численно равна периоду тактовых импульсов. В нулевом периоде выходное напряжение интегратора сбрасывается в нуль. На выходе ЦАП также устанавливается нулевое напряжение. Затем схема проходит через показанную в табл. 9 последовательность состояний.

Таблица 2

| Uвх=0,6 В | Uвх=0 В | ||||||||

| N такта | US, В | Uи, В | Uк, бит | UЦАП, В | N такта | US, В | Uи ,В | Uк, бит | UЦАП, В |

| 0,6 | 0,6 | ||||||||

| -0,4 | 0,2 | -1 | -1 | -1 | |||||

| -0,4 | -0,2 | -1 | |||||||

| 1,6 | 1,4 | -1 | -1 | ||||||

| -0,4 | 1,0 | ||||||||

| -0,4 | 0,6 | -1 | -1 | ||||||

| -0,4 | 0,2 | ||||||||

| -0,4 | -0,2 | -1 | -1 | -1 | |||||

| 1,6 | 1,4 | ||||||||

| -0,4 | 1,0 | -1 | -1 | ||||||

| -0,4 | 0,6 | ||||||||

| -0,4 | 0,2 | -1 | -1 | ||||||

| -0,4 | -0,2 | -1 | |||||||

| 1,6 | 1,4 | -1 | -1 | ||||||

| -0,4 | 1,0 | ||||||||

| -0,4 | 0,6 | -1 | -1 |

В тактовые периоды 2 и 7 состояния системы идентичны, так как при неизменном входном сигнале Uвх=0,6 В цикл работы занимает пять тактовых периодов. Усреднение выходного сигнала ЦАП за цикл действительно дает величину напряжения 0,6 В:

(1-1+1+1+1)/5=0,6.

Для формирования выходного кода такого преобразователя необходимо каким-либо образом преобразовать последовательность бит на выходе компаратора в виде унитарного кода в последовательный или параллельный двоичный позиционный код. В простейшем случае это можно сделать с помощью двоичного счетчика. Возьмем в нашем примере 4-разрядный счетчик. Подсчет бит на выходе компаратора за 16-ти тактный цикл дает число 13. Несложно увидеть, что при Uвх=1 В на выходе компаратора всегда будет единица, что дает за цикл число 16, т.е. переполнение счетчика. Напротив, при Uвх=-1 В на выходе компаратора всегда будет нуль, что дает равное нулю содержимое счетчика в конце цикла. В случае, если Uвх=0 то, как это видно из табл. 2, результат счета за цикл составит 810 или 10002. Это значит, что выходное число АЦП представляется в смещенном коде. В рассмотренном примере верхняя граница полной шкалы составит 11112 или +710, а нижняя- 00002 или -810. При Uвх=0,6 В, как это видно из левой половины табл. 2, содержимое счетчика составит 1310 в смещенном коде, что соответствует +5. Учитывая, что +8 соответствует Uвх=1 В, найдем

5*1/8=0,625 > 0,6 В.

Дата добавления: 2021-09-07; просмотров: 791;