Управляющие биты Биты режима работы

Флаг проверки выравнивания

(Alignment check — AC)

Флаг устанавливается при адресации одинарного или двойного слова, не выровненного на границу слова или двойного слова.

Флаг идентификации

(Identification flag — IF)

Если процессор в состоянии устанавливать и сбрасывать этот флаг, то данный

Биты режима работы

Флаг вложенной задачи

(Nested task flag — NT)

Указывает на то, что текущее задание вложено в другое задание при работе в защищенном режиме

Флаг режима виртуального 8086

(Virtual 8086 mode — VM)

Позволяет программисту включать и

выключать режим виртуального 8086

процессор поддерживает команду CPUID. При выполнении данной команды выдается информация об изготовителе, серии и модели процессора

Флаг возобновления(Resume flag - RF)

Дает возможность программисту отменить отладочные исключения, так что команда после отладочного исключения может быть перезапущена без генерации другого исключения

Уровень привилегий ввода-вывода

(I/O privilege level — IOPL)

Определяет уровень привилегий ввода-вывода выполняющего процесса.

При установленном флаге (низкий уровень привилегий) при каждом доступе к устройствам ввода-вывода генерируются исключения.

Флаг направления(Direction flag — DP)

Задает порядок изменения (увеличение или уменьшение) содержимого 16-битовых полу регистров SI и DI (для работы в 16-битовом режиме) или 32-битовых регистров ESI и EDI (для работы в 32-битовом режиме), использующихся в командах обработки строк.

Флаг разрешения прерываний

(Interrupt enable flag —- IF)

Если этот флаг установлен, процессор реагирует на внешние прерывания.

Флаг ловушки (Trap flag — TF)

Если флаг установлен, то после выполнения каждой команды генерируется прерывание. Этот режим используется для отладки.

Флаг ожидания виртуального прерывания.

(Virtual interrupt pending - VIP)

Используется в режиме виртуального 8086, чтобы указать, что одно или несколько прерываний ожидают обслуживания.

Флаг виртуального прерывания.

(Virtual interrupt flag - VIP)

В режиме виртуального 8086 используется вместо флага IF.

Коды условий

Флаг коррекции, или вспомогательного переноса(Auxiliary carry flaf - AF)

Если данный флаг установлен, то это означает, что произошел перенос или заем единицы из одного полубайта в другой при выполнении операций с 8-битовыми арифметическими или логическими объектами с использованием регистра AL

Флаг переноса(Carry flag — CF)

Используется для индикации переноса единицы в старший разряд или займа единицы из этого разряда при арифметических операциях. Его содержимое также изменяется при некоторых операциях циклического сдвига

Флаг переполнения(Overflow flag — OF)

Указывает на переполнение результатов при сложении или вычитании

Флаг четности(Parity flag — PF)

Четность результата арифметической или логической операции. 1 указывает, что результат четный, а 0 — что результат нечетный

Флаг знака(Sign flag — SF)

Указывает знак результата арифметической или логической операции

Флаг нуля(Zero flag — ZF)

Указывает, равен ли нулю результат арифметической или логической операции

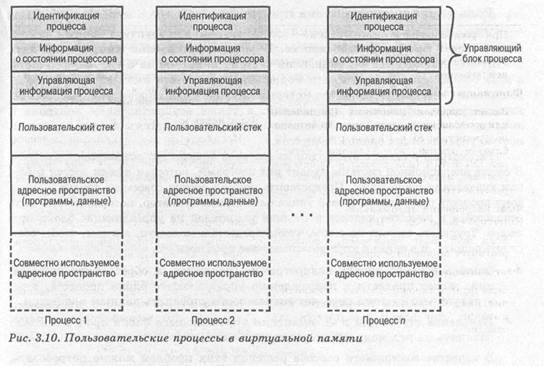

На рис. 3.10 предложена возможная структура образов процессов в виртуальной памяти. Каждый образ процесса состоит из управляющего блока процесса, стека пользователя, закрытого адресного пространства процесса и всех других адресных пространств, которые данный процесс использует совместно с другими процессами. На рисунке каждый образ процесса изображен в виде области непрерывных адресов, но в реальной реализации это может быть не так; размещение образа процесса в памяти зависит от схемы управления памятью и от способа организации управляющих структур в операционной системе.

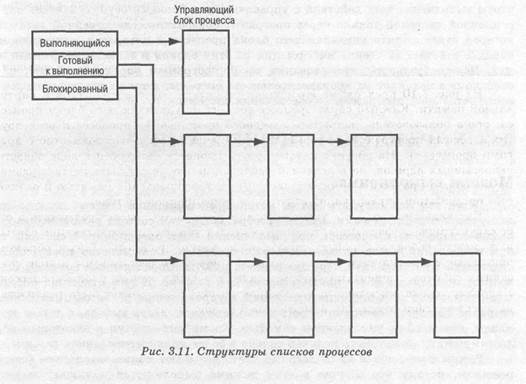

Как видно из табл. 3.5, управляющий блок процесса может содержать в себе структурную информацию, в которую входят указатели, позволяющие связывать между собой различные управляющие блоки процессов. Таким образом, описанные в предыдущем разделе очереди могут быть реализованы в виде связанных списков, элементами которых являются управляющие блоки процессов. Например, схема очередности, показанная на рис. 3.5,а, может быть реализована в соответствии со схемой, изображенной на рис. 3.11.

|

Дата добавления: 2016-06-05; просмотров: 2133;