ПЛМ комбинационной логики.

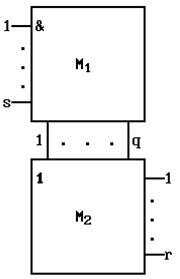

Рис. 4 Двухуровневая ПЛМ комбинационного типа

Рис. 4 Двухуровневая ПЛМ комбинационного типа

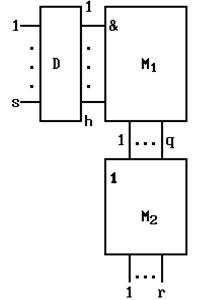

|  Рис. 5 ПЛМ комбинационного типа

Рис. 5 ПЛМ комбинационного типа

|

Двухуровневые ПЛМ комбинационного типа (Рис. 4), (состоят из двух матриц М1 и М2, образующих соответственно первый и второй уровни схемы. Матрица М1 имеет s входов и q выходов. Она позволяет реализовать q конъюнкций р1,…, рq от переменных х1,…,хs, поступающих на ее входы. Матрица М2 имеет q входов и r выходов. Она позволяет реализовать r дизъюнкций y1,…yr переменных р1,…,рq, поступающих на ее входы с выходов матрицы М1. ПЛМ с s входами, r выходами и q промежуточными шинами обозначается как ПЛМ (s,r,q) (Рис. 2). К выходам матрицы М2 часто подключается слой программируемых инверторов. Аналогичные инверторы иногда включаются между матрицами М1 и М2).

Разновидностью ПЛМ (s,r,q) является их усовершенствованный вариант: ПЛМ (z,q). В ПЛМ (z,q) фиксируется лишь два параметра: суммарное число входов и выходов z=s+r и число промежуточных шин q. Конкретные значения s и r могут выбираться произвольно при настройке ПЛМ (z,q). Например, ПЛМ (6,10) путем соответствующей настройки может быть использована как ПЛМ (3,3,10); ПЛМ (5,1,10) и так далее.

Трехуровневые ПЛМ комбинационного типа (Рис. 5) (содержат дополнительный s-входовый блок D. Число выходов блока D равно числу горизонтальных шин h в матрице М1 и каждый i-ый выход блока D соединен с i-ой горизонтальной шиной этой матрицы (i=1,2,…,h).

Блок D может иметь самую различную структуру. Например, он может представлять собой матрицу М0, настроенную на реализацию функций дешифратора на s входов с инверсными выходами. Наиболее часто блок D состоит из набора s/2 двухвходовых полных дешифраторов с инверсными выходами. Трехуровневую ПЛМ с s входами, q промежуточными шинами и r выходами, первый уровень которой образует блок из двухвходовых дешифраторов, как правило обозначают как ПЛМД (s,r,q). Для ПЛМД (s,r,q) блок D имеет s входов и 2s выходов (h=2s), а число горизонтальных шин матрицы М1 кратно четырем. Четыре выхода каждого дешифратора DCj (j=1, s/2) соединены с соответствующими четырьмя горизонтальными шинами j-ой группы матрицы М1. Использование ПЛМД позволяет по сравнению с ПЛМ сократить число требуемых промежуточных шин для реализации заданной системы булевых функций и реализовывать более сложные системы двоичных функций.

ПЛМ с памятью.

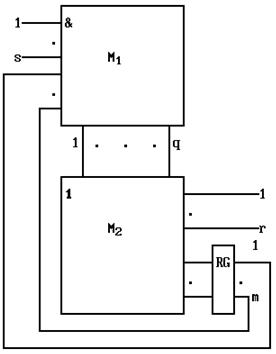

Рис. 6 Двухуровневая ПЛМ с памятью

Рис. 6 Двухуровневая ПЛМ с памятью

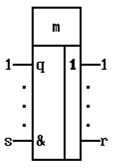

|  Рис. 7 Функциональное изображение двухуровневой ПЛМ с памятью

Рис. 7 Функциональное изображение двухуровневой ПЛМ с памятью

|

Двухуровневая ПЛМ с памятью (Рис. 6), в отличие от двухуровневой ПЛМ комбинационного типа, содержит внутренний m-разрядный регистр. Входы регистра соединены с выходными шинами матрицы М2, а выходы - с входными шинами матрицы М1. Двухуровневую ПЛМ с памятью, имеющую s внешних входов, r внешних выходов, q промежуточных шин и m внутренних элементов памяти, будем называть ПЛМ (s,r,q,m). Функциональное изображение такой ПЛМ показано на Рис. 7. Разновидностью ПЛМ (s,r,q,m) являются матричные БИС, у которых включение элементов памяти в обратную связь задается на этапе настройки. По аналогии с термином "программируемый инвертор" здесь целесообразно использовать термин "программируемый элемент памяти" (триггер), поскольку он либо включается в обратную связь с выхода М2 на вход М1, либо нет. В последнем случае выход М2 будет непосредственно соединен с входом М1, в результате на соответствующей ПЛМ может быть реализована система булевых функций, представленная в форме, отличной от ДНФ.

Трехуровневые ПЛМ с памятью строятся по тому же принципу, что и трехуровневые ПЛМ комбинационного типа.

Примером ПЛМ комбинационного типа является БИС 556РТ1 с параметрами s=16, r=8, q=48, а примером ПЛМ с памятью-БИС КР556РТ3 с параметрами s=16, r=8, q=48, m=6.

В выпускаемых ПЛМ число входов может достигать 24, число выходов — 16, число цепей конъюнкций — 96. Структуры с программированием на заводе—изготовителе широко используются при выпуске БИС.

Вывод.

Таким образом, ПЛМ является универсальным цифровым устройством, позволяющим реализовать логические функции различной сложности.

2. Программируемые логические интегральные схемы (ПЛИС)

ПЛИС — это матричные большие интегральные схемы.

Назначение.

ПЛИС позволяют программно скомпоновать в одном корпусе электронную схему, эквивалентную схеме, включающей от нескольких десятков до нескольких сотен ИС стандартной логики.

Классификация.

1. По типу программируемых элементов:

- однократно программируемые (транзисторы с перемычками типа antifuse, с программированием плавающих затворов);

- репрограммируемые

а) с ультрафиолетовым стиранием (EPROM),

б) с электрическим стиранием (EEPROM, FLASH),

в) с триггерной памятью конфигурации (SRAM-based)).

2. По архитектуре.

- микросхемы с архитектурой EPLD (EPROM technology bazed complex Programmable Logic Device) — многократно программируемые;

- микросхемы с архитектурой FPGA (Field Programmable Gate Array) — многократно реконфигурируемые.

В настоящее время на мировом рынке можно отметить несколько основных компаний-производителей ПЛИС — XILINX, ALTERA, LATTICE, AT&T, INTEL, выпускающих микросхемы с указанной архитектурой.

Устройство (особенности конструкции).

Микросхема ПЛИС имеет в своём составе

- память для хранения конфигурации;

- поля логических блоков;

- поля блоков ввода/вывода;

- коммутационные блоки.

В качестве памяти для хранения конфигурации в ПЛИС EPLD используется ППЗУ с ультрафиолетовым стиранием, а у ПЛИС FPGA — статическое ОЗУ.

Логические блоки, блоки ввода/вывода и коммутационные поля конфигурируются при загрузке в ПЛИС битовой последовательности, полученной в результате разработки схемы.

В зависимости от семейства ПЛИС перечисленные блоки имеют разную степень сложности и обладают разными функциональными возможностями. Так, например, в ПЛИС архитектуры FPGA семейств XILINX, ХС2000, ХСЗ000, ХСЗ100, ХС4000 поля логических блоков и блоков ввода-вывода, связываются между собой посредством коммутационных блоков.

Схема ПЛИС

Рассмотрим более подробно конструкцию основных узлов ПЛИС.

Логический блок — один из базовых элементов архитектуры ПЛИС FPGA, может выполнять любую логическую функцию в соответствии с заданной битовой последовательностью (Рис. 8). Изменять выполняемую функцию можно неограниченное количество раз путем загрузки другой битовой последовательности.

В состав данного блока входят логические элементы (транзисторные пары, простые логические вентили И-НЕ, ИЛИ-НЕ, и т.п. Их ещё называют SLC – Simple Logic Cells), реализующие любые логические функции, табличные преобразователи, триггеры, коммутационные узлы – мультиплексоры, программируемые мультиплексоры.

Рис. 8 Логический блок ПЛИС

Блок ввода/вывода (Рис. 9) так же, как и логический блок, может быть настроен на выполнение любого электрического соединения реализованной внутри ПЛИС схемы с внешним миром через соответствующий контакт микросхемы.

Блок содержит программно-доступные ячейки памяти, логические элементы, реализующие любые логические функции, триггеры, программируемы мультиплексоры.

Блок имеет два канала – для ввода сигналов и для вывода. В каждом канале сигналы могут передаваться прямым путём или фиксироваться в триггерах в зависимости от программирования мультиплексора.

Работа ПЛИС.

Рассмотрим, для примера, микросхему FPGA.

Данная архитектура представляет собой матрицу логических ячеек, соединенных между собой логическими ключами. Содержащаяся в микросхемах FPGA статическая память, заполнена определенной битовой последовательностью. Она воздействует на логические ячейки и соединяющие их ключи и позволяет получить требуемые электрические схемы (регистры, счетчики, логические схемы и т.д., соединенные друг с другом в требуемом порядке). Каждая микросхема FPGA имеет также вход для записи битовой последовательности, заполняющей статическую память, а также элементы "вход/выход" для связи с другими микросхемами.

При создании систем на основе ПЛИС все этапы проектирования выполняются разработчиком на одном рабочем месте с использованием систем автоматизированного проектирования (САПР). Каждая компания — производитель ПЛИС разрабатывает и выпускает свою САПР, обеспечивающую реализацию всех этапов проектирования для каждого типа программируемой логики.

Рис. 9 Блок ввода/вывода ПЛИС

Так же, как и при создании программ для универсального процессора, для программирования ПЛИС необходимы инструментальные средства (языки программирования, трансляторы, оптимизаторы и т.д.), конечным результатом работы которых является битовая последовательность, заполняющая статическую память микросхемы FPGA. Системы автоматизированного проектирования позволяют разработчику, пользуясь стандартными элементами библиотек, создавать на рабочих станциях логические схемы, реализующие заданные алгоритмы, проводить моделирование с анализом функциональных и временных характеристик, осуществлять оптимизацию разработанных схем по оборудованию и времени выполнения задачи и транслировать разработанные схемы в битовые последовательности, определяющие логику работы процессора. Например, компания XILINX поставляет полное математическое обеспечение для разработки и применения устройств на базе FPGA и EPLD. Для разработки используются схемотехнические редакторы и системы моделирования, входящие в состав наиболее популярных САПР: VIEWLOGIC и MENTOR GRAPHICS, функционирующих на PC и рабочих станциях SUN и HP соответственно.

В настоящее время компания XILINX производит микросхемы следующих типов:

· серии ХС7200 и ХС7300 — типа EPLD. Содержат от 18 до 144 многовходовых макроячеек, представляющих собой программируемое 1-разрядное АЛУ со встроенным триггером-защелкой. Ячейки объединяются матричным коммутатором. ИС могут быть использованы для нестандартных АЛУ, дешифраторов, счетчиков и т. п.;

· серии ХС2000, ХСЗ000 — типа FPGA. Содержат от 2000 до 9000 эквивалентных вентилей. Включают до 320 конфигурируемых логических блоков (КЛБ);

· серии ХСЗ000А, ХСЗ100А, ХС4000, ХС5000 — типа FPGA. Включают от 2000 до 25000 вентилей. Содержат до 1024 КЛБ, выполняющих логическую функцию от 5, 9 или 20 переменных со временем выполнения до 2 нс и до 2560 триггеров. Имеется возможность реализации встроенного ЗУ до 32 Кбит (серия ХС4000);

· серия ХС4000Е — типа FPGA. Разработана на основе серии ХС4000 по улучшенной 0.5 мкм технологии с тремя слоями металлизации. Обеспечивает в 1,5 раза более высокую частоту переключения триггеров, на 60% более высокую эффективность выполнения арифметических операций. Имеет более низкую относительную стоимость. Новая функция конфигурации встроенного ОЗУ позволяет реализовать синхронный/ асинхронный, одно/ двухпортовый режимы обмена;

· серия ХС6200 — типа FPGA. Создана специально для построения сопроцессоров. Имеет встроенный 8/16/32-разрядный программируемый (FastMAP) интерфейс, предназначенный для организации непосредственного обмена с шиной основного процессора. Повышенная скорость конфигурации (в 1000 раз по сравнению с предыдущими сериями) допускает частичную реконфигурацию FPGA в процессе выполнения текущей задачи. Встроенное ОЗУ (36К-256К) доступно через FPGA логику, через FastMAP интерфейс либо обоими способами;

· серия ХС8100 — однократно программируемые FPGA. Выполнена на основе Micro Via antifuse КМОП технологии с тремя слоями металлизации. Технология обеспечивает более высокую плотность упаковки логических элементов и малое потребление;

· серия ХС9500 — типа CPLD. Многократно перепрограммируемые (до 10000 раз) непосредственно на рабочем устройстве микросхемы. Содержат от 800 до 6400 рабочих ячеек или от 36 до 288 макроячеек, аналогичных серии ХС7300. Рабочая частота — до 150 МГц. Все серии компании XILINX имеют высочайшую степень защиты от копирования.

Выводы:

1. Технология ПЛИС обеспечивает рекордно короткий проектно-технологический цикл (от нескольких часов до нескольких дней), минимальные затраты на проектирование, максимальную гибкость при необходимости модификации аппаратуры.

2. На основе одной или нескольких микросхем FPGA можно создать реконфигурируемый процессор, обладающий преимуществами спецпроцессора на "жесткой" логике, но способного путем изменения содержимого статической памяти решать любые задачи, подобно универсальному процессору.

3. Методика и средства проектирования ЦУ

Общие сведения

Проектирование — разработка технической документации, позволяющей изготовить заданное устройство в заданных условиях.

Стратегия проектирования — функциональная декомпозиция. Для системы в целом и ее блоков используется концепция "черного ящика". Для "черного ящика" разрабатывается функциональная спецификация, включающая внешнее описание блока (входы и выходы) и внутреннее описание — функцию или алгоритм работы: F= Ф (X, t), где Х — вектор входных величин; F — вектор выходных величин; t — время. При декомпозиции функция Ф разбивается на более простые функции Ф1-.Фк, между которыми должны быть установлены определенные связи, соответствующие принятому алгоритму реализации функции Ф. В результате разбиения в конечном счете получается структура. Переход от функции к структуре называется синтез.

Выбор наилучшего варианта при синтезе осуществляется по результатам анализа, когда проверяется правильность работы и некоторые показатели, характеризующие устройство.

Декомпозиция функций блоков выполняется до тех пор, пока не получатся типовые функции, каждая из которых может быть реализована той или иной микросхемой.

Процесс проектирования — многошаговый и итерационный, с возвратами назад и пересмотром ранее принятых решений.

Декомпозиция заканчивается при получении типовых функций, которые соответствуют тем или иным микросхемам или элементам функциональных библиотек программируемых БИС/СБИС.

Характер проектирования существенно зависит от вида применяемой элементной базы.

Классификация цифровых ИС с точки зрения методов проектирования

Классификация цифровых ИС по признакам, связанным с методами их проектирования, приведена на Рис. 10.

Рис. 10 Классификация цифровых ИМС по признаку методов проектироания

К стандартным микросхемам отнесены схемы малой и средней степени интеграции МИС и СИС. Эти микросхемы производятся массовыми тиражами и реализуют стандартные элементы и узлы, функционирование которых никак не определяется конкретными потребителями. К стандартным схемам высокого уровня интеграции (БИС и СБИС) относятся микропроцессоры МП, микроконтроллеры МК и запоминающие устройства ЗУ, остающиеся неизменными после изготовления независимо от устройств и систем, в которых они используются. Стандартные ИС имеют обширный рынок, что благоприятно для снижения их стоимости.

К специализированным ИС (СпИС) относятся все микросхемы, структура которых в отличие от структур стандартных ИС массового производства каким-либо способом приспосабливается к конкретным требованиям того или иного проекта. В английской терминологии СпИС именуются АSIСs (Application Specific Integrated Circuits). Среди СпИС различают классы полузаказных и заказных. Разновидностями заказных микросхем являются полностью заказные и спроектированные методом "на стандартных ячейках".

Полностью заказные схемы целиком проектируются по требованиям конкретного заказчика. Проектировщик имеет полную свободу действий, определяя схему по своему усмотрению вплоть до уровня схемных компонентов (отдельных транзисторов и т. п.). Для изготовления схемы требуется разработка всего комплекта фотошаблонов, верификация и отладка всех схемных фрагментов. Такие схемы очень дороги и имеют длительные циклы проектирования.

Схемы на стандартных ячейках отличаются от полностью заказных тем, что их фрагменты берутся из заранее разработанной библиотеки схемных решений. Такие фрагменты уже хорошо отработаны, стоимость и длительность проектирования при этом снижаются. Для производства схем тоже требуется изготовление полного комплекта фотошаблонов, но разработка их облегчена. Потери сравнительно с полностью заказными ИС состоят в том, что проектировщик имеет меньше свободы в построении схемы, т. е. результаты оптимизации ее по критериям площади кристалла, быстродействию и т.д. менее эффективны. Наивысших технических параметров добиваются от полностью заказных схем, однако метод стандартных ячеек популярен, т. к при небольших потерях в технических характеристиках, с его помощью можно заметно упростить проектирование схемы. Полностью заказные схемы разрабатываются за время, превышающее время разработки методом стандартных ячеек приблизительно в два раза.

К полузаказным схемам относятся базовые матричные кристаллы БМК (в английской терминологии МРGА, Маsk Programmamble Gate Arrays). В этом случае имеется стандартный полуфабрикат, который доводится до готового изделия с помощью индивидуальных межсоединений. Реализация требует изготовления лишь малого числа фотошаблонов. Стоимость и длительность проектирования в сравнении с полностью заказными схемами сокращаются в 3...4 раза, но результат еще дальше от оптимального, поскольку в матричных БИС (МАБИС) менее рационально используется площадь кристалла (на кристалле остаются неиспользованные элементы и т. п.), длины связей не минимальны и быстродействие не максимально.

Сходство методов проектирования на БМК и стандартных ячейках состоит в использовании библиотек функциональных элементов. Различие в том, что для схем, проектируемых по методу стандартных ячеек, библиотечный набор элементов имеет более выраженную топологическую свободу. Например, стандартизируется только высота ячеек, а их длины могут быть различными. При проектировании вначале из набора библиотечных элементов подбираются необходимые функциональные блоки, а затем решаются задачи их размещения и трассировки.

САПР для проектирования по методу стандартных ячеек более сложны, чем для проектирования на основе БМК, которому свойственны более жесткие топологические ограничения. Ограничения вводятся и для метода стандартных ячеек (постоянство высоты ячеек, предопределенность геометрических размеров и положения шин питания, тактирования и др.). По мере применения более мощных САПР ограничения ослабляются.

Длительность изготовления БИС/СБИС методом стандартных ячеек превышает этот же показатель для МАБИС на основе БМК в 1,3... 1,8 раз.

Особое место в классификации занимают БИС/СБИС ПЛ. С одной стороны, они относятся к СпИС, т. к. в конечном счете приспосабливаются к требованиям конкретного проекта. В то же время этот процесс (конфигурация схемы) не затрагивает изготовителя, для которого схемы являются стандартным продуктом со всеми вытекающими из этого выгодами

Дата добавления: 2017-11-21; просмотров: 2608;