Оперативное запоминающее устройство (ОЗУ).

ОЗУ называют энергозависимую память. Вся информация пропадает из такой памяти вскоре после снятия напряжения питания. При этом данная память гораздо быстрее, чем ПЗУ и может использоваться для временного хранения данных, к которым нужен быстрый доступ. К этим данным, как правило, относятся переменные.

ОЗУ делится на два вида: динамическую (DRAM)и статическую (SRAM).

DRAM.

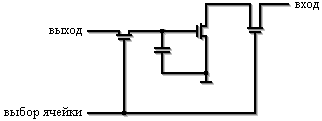

Динамическая память — DRAM (Dynamic Random Access Memory) — получила свое название от принципа действия ее запоминающих ячеек, которые выполнены в виде конденсаторов, образованных элементами полупроводниковых микросхем(рис 8.2). При отсутствии обращения к ячейке со временем, за счет токов утечки, конденсатор разряжается и информация теряется.Поэтому такая память требует периодической подзарядки конденсаторов (обращения к каждой ячейке) — память может работать только в динамическом режиме.

Рис 8.4

Каждая ячейка способна хранить только один бит. Если конденсатор ячейки заряжен, то это означает, что бит включен, если разряжен – выключен. Если необходимо запомнить один байт данных, то понадобится 8 ячеек (1 байт = 8 битам). Ячейки расположены в матрицах и каждая из них имеет свой адрес, состоящий из номера строки и номера столбца.

При чтении данных их памяти сначала на все входы подается сигнал RAS (Row Address Strobe) – это адрес строки. После этого, все данные из этой строки записываются в буфер. Затем на регистр подается сигнал CAS (Column Address Strobe) – это сигнал столбца и происходит выбор бита с соответствующим адресом. Этот бит и подается на выход. Но во время считывания данные в ячейках считанной строки разрушаются и их необходимо перезаписать взяв из буфера.

При записи подается сигнал WR (Write) и информация поступает на шину столбца не из регистра, а с информационного входа памяти через коммутатор, определенный адресом столбца. Таким образом, прохождение данных при записи определяется комбинацией сигналов адреса столбца и строки и разрешения записи данных в память. При записи данные из регистра строки на выход не поступают.

Обычно в микросхеме имеется несколько матриц. Адреса ячеек этих матриц совпадают. В итоге одновременно считываются не один бит, а сразу несколько. Количество этих матриц называют разрядностью памяти.

SynchronousDynamicRandomAccessMemory (SDRAM)

Чтение из микросхем памяти DRAM могло осуществляться в любой момент времени. При этом время чтения данных могло быть различным. Для завершения цикла чтения-записи в заданное время была создана синхронная DRAM. Работа это микросхемы памяти была синхронизирована с интерфейсом памяти посредством подачи на микросхему синхросигнала. Чтение и запись могли производиться только по фронту или по срезу этого сигнала. В микросхемах DDRSDRAM(DoubleDataRate SDRAM) чтение производится одновременно и по фронту и по спаду, что позволило увеличить в два раза скорость работы памяти по сравнению с обычной SDRAM.

Существенная отличительная особенность микросхем SDRAM от микросхем более ранних типов DRAM заключается в разбиении массива данных на несколько логических банков (как минимум — 2, обычно — 4). Разбиение массива памяти SDRAM на банки было введено, главным образом, для минимизации задержек поступления данных в систему. После осуществления любой операции со строкой памяти, требуется определенное время для осуществления ее «подзарядки». И преимущество «многобанковых» микросхем SDRAM заключается в том, что можно обращаться к строке одного банка, пока строка другого банка находится на «подзарядке». Можно расположить данные в памяти и организовать к ним доступ таким образом, что далее будут запрашиваться данные из второго банка, пока первый находится на «подзарядке». Такая схема доступа к памяти называется «доступом с чередованием банков» (Bank Interleave).

Дата добавления: 2017-01-16; просмотров: 1596;