Назначение и принцип работы микросхем преобразователей кодов и шифраторов

Операция изменения кода числа называется его перекодированием. Интегральные микросхемы, выполняющие эти операции, называются преобразователями кодов. Преобразователи кодов бывают простые и сложные. К простым относятся преобразователи, которые выполняют стандартные операции изменения кода чисел, например, преобразований двоичного кода в одинарный и обратную операцию. Сложные преобразователи кодов выполняют нестандартные преобразования кодов и их схемы приходится разрабатывать каждый раз с помощью алгебры логики.

Будем считать, что преобразователи кодов имеют n входов и k выходов. Соотношения между n и k могут быть любыми: n = k, n < k, n > k. При преобразовании кода чисел с ним могут выполняться различные дополнительные операции, например, умножение на весовые коэффициенты. Примером невесового преобразования является преобразование двоично-десятичного кода в двоичный. Весовые преобразователи кодов используются при преобразовании числовой информации.

Интегральные микросхемы преобразователей кодов выпускаются только для наиболее распространенных операций:

преобразователи двоично-десятичного кода в двоичный код;

преобразователи двоичного кода в двоично-десятичный;

преобразование двоичного кода в код Грея;

преобразование двоичного кода в код управления сегментными индикаторами;

преобразователи двоичного или двоично-десятичного кода в код управления шкальными или матричными индикаторами.

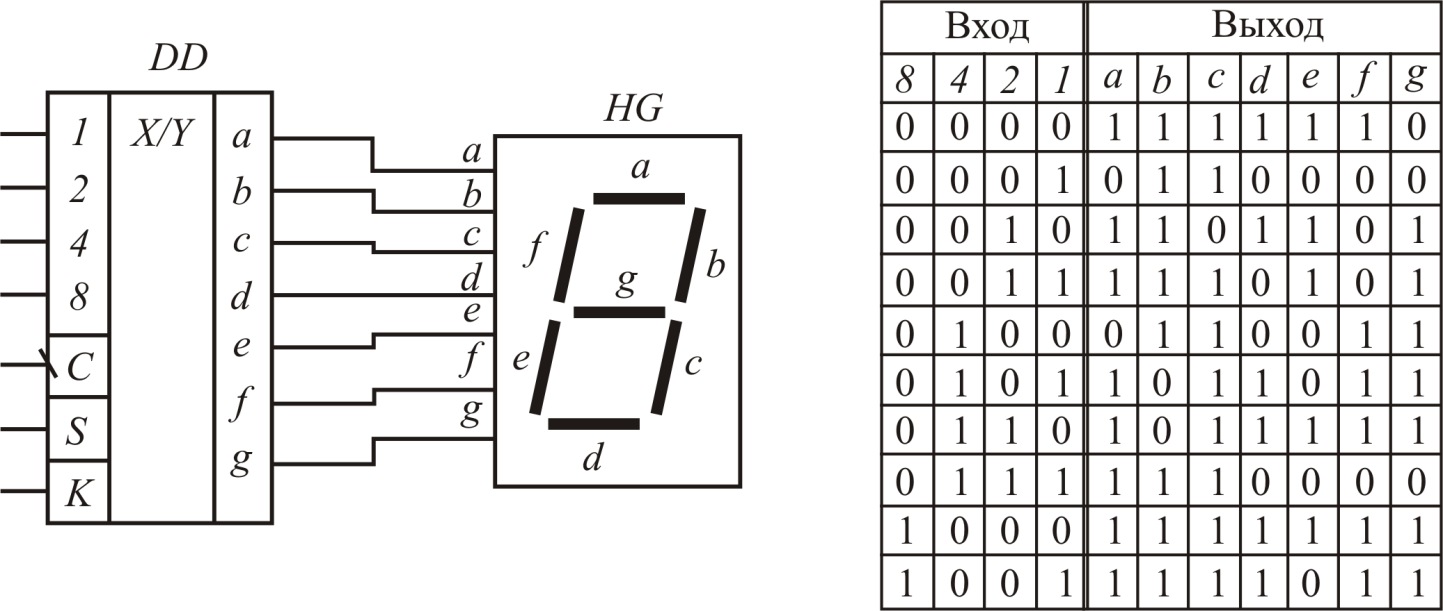

В качестве примера рассмотрим микросхему преобразователя двоичного кода в код управления семисегментным цифровым индикатором, приведенную на рисунке 11.

Рисунок 11 – Схема преобразователя кода для семисегментного индикатора и таблица истинности

Представленная на рисунке 11 микросхема преобразователя кодов имеет возможность запоминать сигналы входного кода. Она имеет четыре информационных входа для подачи сигналов в коде 1-2-4-8 и три управляющих входа S, K, C. Вход S определяет полярность выходных сигналов: при уровне «1» на этом входе для зажигания сегментов используют уровень «0» на выходах, а при уровне «0» – уровень «1», что соответствует рисунку 11. Уровень «1» на входе К гасит индуцируемый знак индикатора, а уровень «0» разрешает индикацию. Вход С управляет режимом памяти микросхемы. При уровне «1» входной сигнал вызывает изменение индикации прибора HG, при «0» происходит запоминание сигналов на входе, после чего микросхема на другие изменения входных сигналов не реагирует.

Шифратором (coder) называют кодовый преобразователь, который имеет n входов и k выходов, и при подаче сигнала на один из входов (обязательно только на один), на выводах появляется двоичный код возбужденного входа. Шифраторы выполняют функцию обратную дешифраторам, т.е. преобразуют унитарный код в двоичный или двоично-десятичный. Очевидно, что число выходов и входов в полном шифраторе связано соотношением:

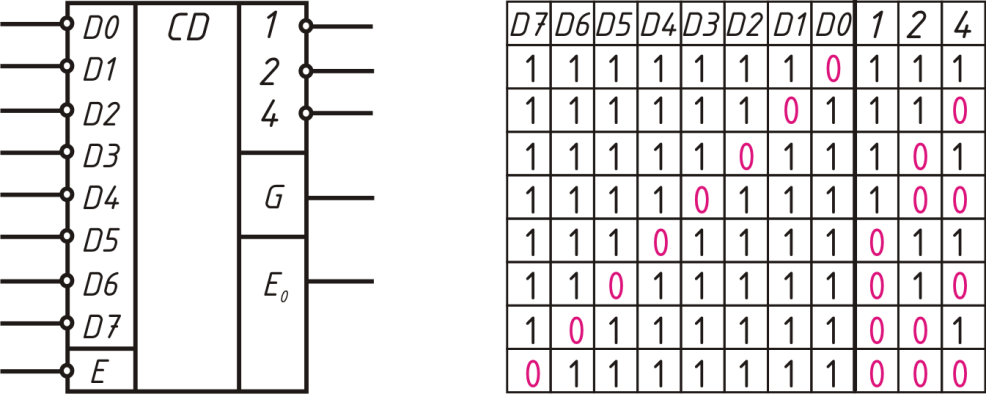

Рассмотрим принцип функционирования шифратора на примере преобразования 8 разрядного единичного кода в трехразрядный двоичный код. Условное графическое обозначение такого шифратора и таблица соответствия сигналов на входе и выходе приведены на рисунке 12.

Рисунок 12 – Условное графическое обозначение шифратора и его таблица истинности

Как следует из анализа рисунка 12 при помощи шифратора можно сократить (сжать) информацию для передачи ее по меньшему числу линий связи, так как k < n. Обратное преобразование, то есть восстановление информации в первоначальном виде можно выполнить с помощью дешифратора. Очевидно, что максимальное число входов шифратора не может превышать количество возможных комбинаций выходных сигналов, то есть необходимо выполнение условия n £ 2k.

В цифровых системах с помощью шифраторов обеспечивается связь между различными устройствами посредством ограниченного числа линий связи. Так, например, в кнопочных пультах управления ввод числовых данных обычно выполняется в унитарном коде посредством нажатия одной из десяти кнопок, а ввод данных в микропроцессор выполняется в двоичном коде.

Помимо уже известных входных (D0–D7) и выходных (1–2–4) сигналов, рассматриваемый (рисунок 12) шифратор имеет входной сигнал включения – E («0» – включен, «1» – выключен). Сигналы на выходе: G – сигнал, свидетельствующий о наличии хотя бы одного возбужденного входа D0–D7 при включенном состоянии шифратора, например, G = 0 при D2 = 0 при E = 0; Е0 – сигнал разрешения, свидетельствующий об отсутствии возбужденных входов D0–D7 при включенном состоянии шифратора (E0 = 0 при Е = 1 и D0 = D1 = … = D7 = 1). Таким образом, трехразрядный двоичный код можно считывать с выхода шифратора только при условии, что G = 1. В свою очередь, сигнал E0 может использоваться для каскадного включения шифраторов и тем самым для увеличения количества входных и выходных сигналов.

В наименовании микросхем шифраторов их функциональное назначение обозначается буквами ИВ.

4.4 Назначение и принцип работы схем сравнения, выполненных в

интегральном исполнении

Многоразрядные схемы сравнения используются для сравнения и определения идентичности двух или нескольких n- разрядных двоичных слов.

Принципы построения и способы технической реализации многоразрядных схем сравнения рассмотрим на примере.

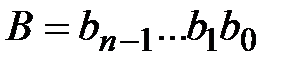

Пусть на п выходах каких-то двух устройств формируются два п - разрядные слова

и

и  .

.

Требуется зарегистрировать совпадение (идентичность) этих слов.

Для решения поставленной задачи необходимо иметь п- разрядную схему сравнения, которая путем поразрядного сравнения элементов  и

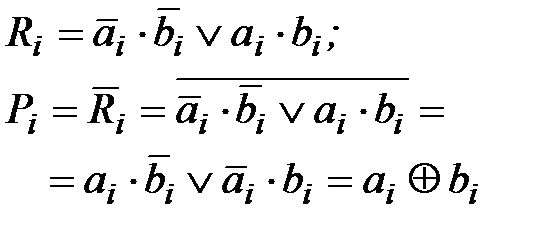

и  определяет соответствие слов А и В. Поразрядное сравнение может быть произведено одноразрядной схемой сравнения. Таблица истинности и переключательная функция одноразрядной схемы сравнения приведены на рисунке 13.

определяет соответствие слов А и В. Поразрядное сравнение может быть произведено одноразрядной схемой сравнения. Таблица истинности и переключательная функция одноразрядной схемы сравнения приведены на рисунке 13.

| a |

|

| Ri (a+b) |

(a¹b) | |

Рисунок 13 - Таблица истинности и переключательная функция

одноразрядной схемы сравнения

Для обнаружения совпадения  и

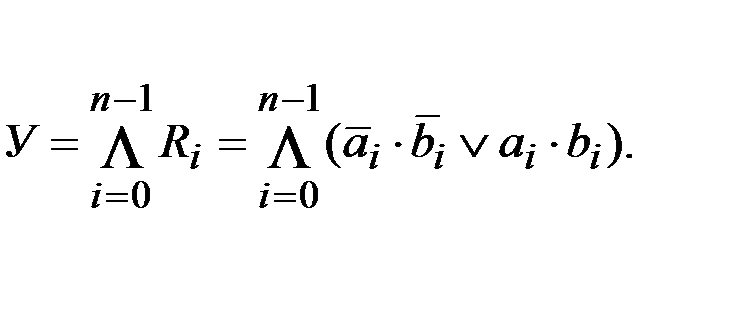

и  во всех разрядах слов А и В необходимо образовать конъюнкцию п - переменных Ri . Таким образом, переключательная функция многоразрядной схемы сравнения описывается выражением:

во всех разрядах слов А и В необходимо образовать конъюнкцию п - переменных Ri . Таким образом, переключательная функция многоразрядной схемы сравнения описывается выражением:

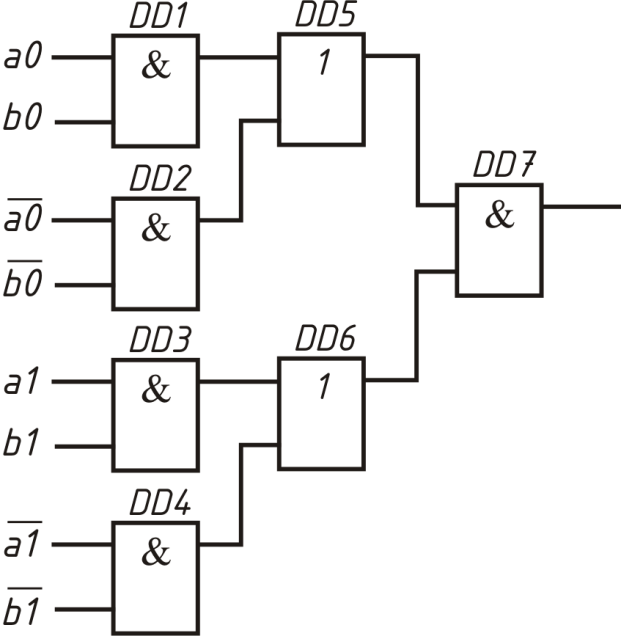

Функциональная схема устройства, удовлетворяющего этому выражению, показана на рисунке 14. Входной сигнал подается парафазным способом (в прямом и инверсном виде).

Рисунок 14- Функциональная схема устройства обнаружения совпадения  и

и  во всех разрядах слов А и В

во всех разрядах слов А и В

ИЛИ-НЕ (стрелка Пирса), И-НЕ (штрих Шефера)

Дата добавления: 2016-11-26; просмотров: 8592;