Основные логические операции и их реализации

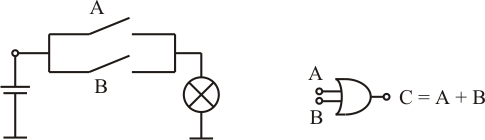

Элемент ИЛИ реализуется схемой с параллельными ветвями (дизъюнкция)

| A | B | C |

|

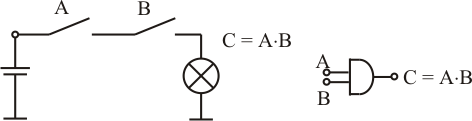

Элемент И, реализуется последовательной схемой (конъюнкция)

| A | B | C |

|

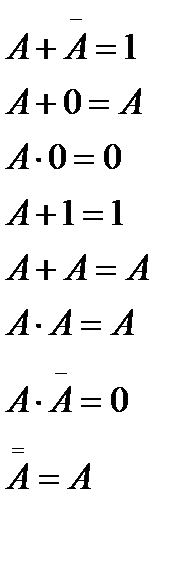

Тождества, связывающие логические переменные

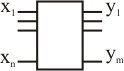

На основе простейших логических устройств можно строить более сложные комбинационные логические схемы – преобразователей совокупности входных логических уровней (входного слова или кода) в выходное слово (выходной код) без запоминания.

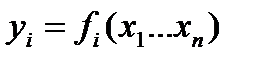

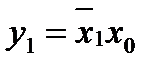

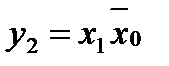

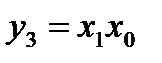

Запись логических функций осуществляется в совершенной нормальной дизъюнктивной форме, при которой функция записывается в виде дизъюнкции слагаемых, каждое из которых есть конъюнкция всех аргументов или их инверсий. Например, И-НЕ записывается в виде:

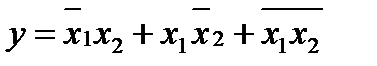

её можно преобразовать

её можно преобразовать

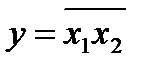

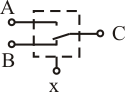

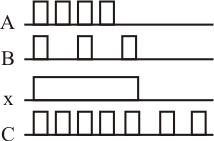

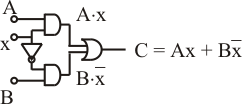

Пример: Пусть имеем двухпозиционный переключатель, с помощью которого цифровые данные из каналов А и В направляются в канал С, переключение осуществлялось с помощью переменной x, таким образом, что код х = 1, данные поступают из канала А, а код х = 0 (  = 1) – из канала В.

= 1) – из канала В.

Это можно записать в виде:

Рассмотрим подробнее некоторые комбинационные схемы

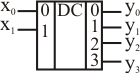

Дешифратор – это комбинационная схема, у которой логическая единица на одном из выходов при 0 на остальных выходах соответствует определенному коду на входе.

Если DC имеет n входов, то max число входов ровно m = 2n

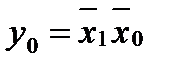

,

,  ,

,  ,

,  ,

,

т.е. DC преобразовывает каждое двоичное слово (число) в одну и только одну логическую единицу на соответствующем выходе, помеченном десятичным числом. Такие дешифраторы используют для вывода двоичного числа в десятичном виде, для определения адресной шины в микросхемах памяти и т.п.

Функциональная схема DC представлена на рис.

Шифратор – цифровое устройство выполняющие логические операции обратные дешифратору. Он преобразует одну или несколько логических единицу, поступивших на входы, в двоичный код на выходе, используются в устройствах ввода десятичных чисел.

Мультиплексор (см. выше) – комбинационная схема предназначенная для преобразования нескольких информационных каналов последовательно в один информационный канал. Переключение каналов происходит под действием управляющего сигнала

Обратную задачу выполняет демультиплексор. С его помощью осуществляется разделение на отдельные составляющие сложного информационного сигнала, полученного с помощью мультиплексора.

Мультиплексоры и демультиплексоры широко используются в системах связи (телефакс) когда по одной линии передачи необходимо передавать информацию от нескольких источников.

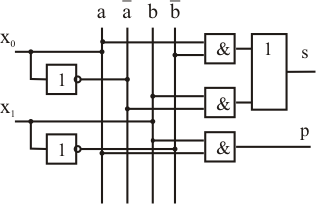

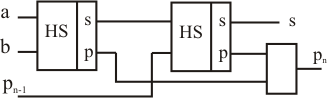

Сумматор выполняет арифметическое сложение двух двоичных чисел. Это важнейшая часть арифметического-логического блока микропроцессора. Различают полусумматор и полный сумматор. Полный сумматор отличается тем, что на его дополнительный вход поступает сигнал переноса от предыдущей схемы суммирования. Такого входа у полусумматора нет. Сумматоры характеризуются разрядностью. Различают одно- и многоразрядные сумматоры. Многоразрядные сумматоры строятся на основе одноразрядных.

Здесь a и b – входные двоичные числа, s – сумма a и b, p, p1 – сигналы переноса, pn-1 – входной сигнал переноса

| Вх | Вых | ||

| а | в | s | P |

Полный сумматор строится на основе двух полусумматоров

Сигнал на выходе комбинационных устройств могут появляться не одновременно. Например, в полном сумматоре выходной сигнал переноса, как правило, появляется быстрее, чем сигнал суммы. Объясняется это тем, что сигналы проходят разное число ступеней обработки. Кроме того, в импульсном сигнале есть временной интервал, когда значение логического сигнала не определено. Все это может вызывать появление логичных сигналов. Такие нарушения в работе цифровых устройств называют «состязаниями». Для их устранения осуществляют синхронизацию всех элементов цифрового устройства с помощью дополнительных схем И, ИЛИ, НЕ, которые позволяют всем информационным сигналам появляться только в момент передачи короткого импульсного сигнала синхронизации.

Дата добавления: 2020-10-14; просмотров: 521;