Краткое теоретическое введение

Оперативные запоминающие устройства (ОЗУ) являются неотъемленной частью микропроцессорных систем различного назначения; они делятся на статические и динамические. В статических ОЗУ запоминание информации производится на триггерах, а в динамических — на конденсаторах емкостью 0,5 пФ. Длительность хранения информации в статических ОЗУ не ограничена, тогда как в динамических она ограничена временем саморазряда конденсатора, что требует специальных средств регенерации и дополнительных затрат времени на этот процесс (около 5...12% времени работы системы).

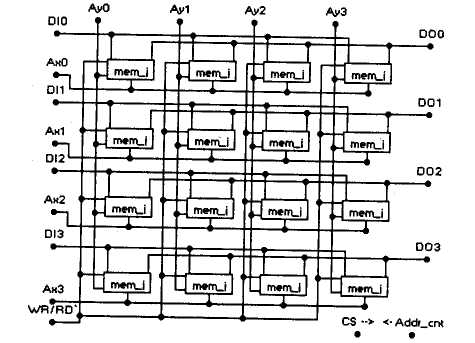

Эволюция микросхем динамического ОЗУ вплотную связана с эволюцией ПК. В первых IBM PC ОЗУ было выполнено на микросхемах емкостью 16 Кбит каждая. Спустя год после представления IBM PC/XT (первого ПК) появились микросхемы емкостью 64 Кбит, причем одна такая микросхема была дешевле чем 4 по 16 Кбит. В 1984г. был сделан еще один шаг по увеличению объема памяти в одном корпусе — появились 256-килобитные микросхемы, которые были установлены на первых IBM РС/АТ. Затем были разработаны микросхемы емкостью 1 Мбит, в дальнейшем начали появляться компоненты динамических ОЗУ в других конструктивных исполнениях и с непрерывной тенденцией увеличения емкости. Конструктивно любое ОЗУ состоит из двух блоков — матрицы запоминающих элементов и дешифратора адреса. По технологическим соображениям матрица чаще имеет двухкоординатную дешифрацию адреса — по строкам и столбцам. На рис. 9.45 показана матрица 16-битного статического ОЗУ: она состоит из 16 ячеек памяти mem_i, схема которой приведена на рис. 9.46. Каждая ячейка памяти адресуется по входам X, Y путем выбора дешифраторами адресных линий по строкам Ах0…Ах3 и по столбцам Ау0...Ау03З (см. рис. 9.45) и подачи по выбранным линиям сигнала логической единицы. При этом в выбранной ячейке памяти срабатывает двухвходовой элемент И (U1), подготавливая цепи чтения-записи информации на входных DI0...DI3 или выходных DO0...DO3 разрядных шинах. Разрешающим сигналом для выдачи адреса является CS (chip select — выбор кристалла), который подается на вход разрешения счетчика адреса (Addr_cnt) или такой же вход дешифраторов, подключенных к выходам счетчика.

рис.9.45. Матрица 16-битного ОЗУ

Современные запоминающие устройства статического типа с произвольным доступом (Static Random Access Memory — SRAM) отличаются высоким быстродействием и в микропроцессорных системах используются ограниченно из-за сравнительно высокой стоимости. В таких системах они используются только в качестве так называемой кэш-памяти. Cache (запас) обозначает быстродействующую буферную память между процессором и основной памятью, служащую для частичной компенсации разницы в скорости процессора и основной памяти: в нее заносятся наиболее часто используемые данные. Когда процессор первый раз обращается к ячейке памяти, ее содержимое параллельно копируется в кэш, и в случаё повторного обращения может быть с гораздо большей скоростью из нее извлечено, в память информация попадает в кэш и одновременно копируется в память (схема Write Through — прямая или сквозная запись) или копируется через некоторое время (схема Write Back — обратная запись). При обратной записи, называемой буферизованной сквозной записью, информация копируется в память в первом же свободном такте, а при отложенной (Delayed Write) — когда для помещения в кэш нового значения не оказывается свободной области; при этом в основное ОЗУ вытесняются сравнительно редко используемые данные. Вторая схема более эффективно и более сложна за счет необходимости поддержания соответствия содержимого кэша и основной памяти.

Кэш-память состоит из области данных, разбитой на блоки (строки), которые являются элементарными единицами информации при работе кэша, и области признаков (tag), описывающей состояние строк (свободна, занята, помечена для дозаписи и т.п.). В основном используются две схемы организации КЭШа: с прямым отображением (direct mapped), когда каждый адрес памяти может кэшироваться только одной строкой (в этом случае номер строки определяется младшими разрядами адреса), и n-связный ассоциативный (n-way associative), когда каждый адрес может кэшироваться несколькими строками. Ассоциативный кэш более сложен, однако позволяет более гибко кэшировать данные; наиболее распространены четырехсвязные системы кэширования.

Микропроцессоры 486 и выше имеют также внутренний (Internal) кэш объем 8…16 Кбайт. Он также обозначается как Primary (первичный) или L1 (Level 1 — первый уровень) в отличие от внешнего (External), расположенного на плате и обозначаемого Secondary (вторичный) или L2. В большинстве процессоров внутренний кэш работает по схеме с прямой записью, а в 486 (процессор Intel P24D и последние DX4-100, AMD DX4-120, 5x86) и Pentium он может работать и с отложенной записью. Последнее требует специальной поддержки со стороны системной платы, чтобы при обмене по DMA (прямое обращение к памяти устройств ввода-вывода) можно было поддерживать согласованность данных в памяти и внутреннем кэше. Процессоры Pentium Pro имеют также встроенный кэш второго уровня объемом 256, 512 или 1024Кбайт с собственным контроллером и локальной 64-разрядной шиной данных, работающей на внутренней частоте МП; использована дополнительная внутренняя оптимизация, ускорена работа конвейера и степень параллелизма, улучшена система предсказания переходов (Dynamic & Speculative Execution).

В микропроцессорных системах в качестве ОЗУ чаще всего используются динамические ОЗУ с запоминающим конденсатором, которые отличаются большим многообразием. Приведем данные по наиболее распространенным типам таких ОЗУ [22].

В динамической памяти (Dynamic Random Access Memory — DRAM) ячейки выполнены на основе областей с накоплением зарядов, занимающих гораздо меньшую площадь, нежели триггеры, и практически не потребляющих энергии при хранении информации. При записи бита в такую ячейку в ней формируется электрический заряд, который сохраняется в течение нескольких миллисекунд; для постоянного сохранения заряда ячейки необходимо регенерировать (перезаписывать) ее содержимое. Ячейки микросхем динамической памяти также организованы в виде прямоугольной матрицы: при обращении к микросхеме на ее входы вначале подается адрес строки матрицы, сопровождаемый сигналом RAS (Row Address Strobe — строб адреса строки), затем, через некоторое время — адрес столбца, сопровождаемый сигналом CAS (Column Address Strobe — строб адреса столбца). При каждом обращении к отдельной ячейке регенерируются все ячейки выбранной строки, поэтому для полной регенерации матрицы достаточно перебрать адреса строк. Ячейки динамической памяти имеют сравнительно малое быстродействие (десятки — сотни наносекунд), но большую удельную плотность (порядка несколько мегабайт на корпус) и меньшее энергопотребление.

Обычные ОЗУ называют часто асинхронными, так как установка адреса и подача управляющих сигналов могут выполняться в произвольные моменты времени, необходимо только соблюдение временных соотношений между этими сигналами. В них включены так называемые охранные интервалы, необходимые для установления сигналов. Существуют также синхронные виды памяти, получающие внешний синхросигнал, к импульсам которого жестко привязаны моменты подачи адресов и обмена данными: они позволяют более полно использовать внутреннюю конвейеризацию и блочный доступ.

FPM DRAM (Fast Page Mode DRAM — динамическая память с быстрым страничным доступом) отличается от обычной динамической памяти тем, что после выбора строки матрицы и удержания сигнала RAS допускает многократную установку адреса столбца, стробируемого сигналом CAS, а также быструю регенерацию по схеме "CAS прежде RAS". Первое позволяет ускорить блочные передачи, когда весь блок данных или его часть находятся внутри одной строки матрицы, называемой в этой системе странице, а второе — снизить затраты времени на регенерацию памяти.

EDO (Extended Data Out — расширенное время удержания данных на выходе) фактически представляют собой обычные микросхемы FPM, на выходе которых установлены регистры-защелки данных. При страничном обмене такие микросхемы работают в режиме простого конвейера: удерживают на выходах данных содержимое последней выбранной ячейки, в то время как на их входы уже подается адрес следующей выбираемой ячейки. Это позволяет примерно на 15% по сравнению с FPM ускорить процесс считывания последовательных массивов данных. При случайной адресации такая память ничем не отличается от обычной.

BEDO (Burst EDO — EDO с блочным доступом) — память на основе EDO, работающая не одиночными, а пакетными циклами чтения/записи. Современные процессоры благодаря внутреннему и внешнему кэшированию команд и данных обмениваются с основной памятью преимущественно блоками слов максимальной ширины. При наличии памяти BEDO отпадает необходимость постоянной подачи последовательных адресов на входы микросхем с соблюдением необходимых временных задержек, достаточно стробировать переход к очередному слову отдельным сигналом.

SDRAM (Synchronous DRAM — синхронная динамическая память) — память с синхронным доступом, работающая быстрее обычной асинхронной (FPM/EDО/ВЕDО). Кроме синхронного доступа, SDRAM использует внутреннее разделение массива памяти на два независимых банка, что позволяет совмещать выборку из одного банка с установкой адреса в другом. SDRAM также поддерживает блочный обмен. Основное преимущество SDRAM состоит в поддержке последовательного доступа в синхронном режиме, где не требуется дополнительных тактов ожидания. При случайной доступе SDRAM работает практически с той же скоростью, что и FPM/EDO.

РВ SRAM (Pipelined Burst SRAM — статическая память с блочным конвейерном доступом) — разновидность синхронных SRAM с внутренней конвейеризации, за счет которой примерно вдвое повышается скорость обмена блоками данных.

DR DRAM (Direct Rambus DRAM) — разновидность синхронной памяти; снабжена специальным интерфейсом фирмы Rambus [84]; для связи с контроллером памяти используется специальная быстродействующая шина Rambus Channel, допускающая использование тактовой частоты 400 МГц и обмен по обоим фронтам импульсов, т. е. обмен с частотой 800 МГц, что соответствует пропускной способ 1,6 Гбит/с; при максимально возможном количестве каналов 4 пропускная способность возрастает до 6,4 Гбит/с.

Кроме основного ОЗУ, устройством памяти снабжается и устройство отображения информации — видеодисплейная система. Такая память называется видеопамятью и располагается на плате видеоадаптера.

Видеопамять служит для хранения изображения. От ее объема зависит максимально возможное разрешение видеокарты — АхВхС, где А — количество точек по горизонтали, В — по вертикали, С — количество возможных цветов каждой точки.

Например, для разрешения 640x480x16 достаточно иметь видеопамять 256 Кбайт, для 800x600x256 — 512 КБ, для 1024x768x65536 (другое обозначение 1024х768х64к) — 2 Мбайт и т.д. Поскольку для хранения цветов отводится целое число разрядов, количество цветов всегда является целой степенью 2 (16 цветов-4 разряда, 256 — 8 разрядов, 64k — 16 и т.д.).

В видеоадаптерах используются следующие типы видеопамяти [22]:

FPM DRAM (Fast Page Mode Dynamic RAM — динамическое ОЗУ с быстрым страничным доступом) — основной тип видеопамяти, идентичный используемой в системных платах. Активно применялась до 1996 г. Наиболее распространенные схемы FPM DRAM — четырехразрядные DIP и SOJ, а также шестнадцатиразрядные SOJ.

(Video RAM — видео-ОЗУ) — так называемая двухпортовая DRAM с поддержкой одновременного доступа со стороны видеопроцессора и центрального процессора компьютера. Позволяет совмещать во времени вывод изображения на экран и его обработку в видеопамяти, что сокращает задержки и увеличивает скорость работы.

ЕDО RAM (Extended Data Out DRAM — динамическое ОЗУ с расширенным временем удержания данных на выходе) — память с элементами конвейеризации, позволяющей несколько ускорить обмен блоками данных с видеопамятью.

SGRAM (Synchronous Graphics RAM — синхронное графическое ОЗУ) — вариант DRAM с синхронным доступом, когда все управляющие сигналы изменяются одновременно с системным тактовым синхросигналом, что позволяет уменьшить временные задержки.

WRAM (Window RAM — оконное ОЗУ) — EDO VRAM, в котором окно, через который обращается видеоконтроллер, сделано меньшим, чем окно для центрального процессора.

МDRAМ (Multibank DRAM — многобанковое ОЗУ) — вариант DRAM, организованный в виде множества независимых банков объемом по 32 Кбайт каждый, работающий в конвейерном режиме.

Увеличение скорости обращения видеопроцессора к видеопамяти, кроме повышения пропускной способности адаптера, позволяет повысить максимальную частоту регенерации изображения, что снижает утомляемость глаз оператора.

Микросхемы памяти имеют четыре основные характеристики — тип, объем, структуру и время доступа. Тип обозначает статическую или динамическую память, объем показывает общую емкость памяти, а структура — количество ячеек памяти и разрядность каждой ячейки. Например, 28/32-выводные DIP-микросхеме SRAM имеют 8-разрядную структуру (8кх8, 16кх8, 32кх8, 64кх8, 128кх8), кэш объемом 256 Кбайт состоит из восьми микросхем 32кх8 или четырех микросхем 64кх8 (речь идет об области данных, дополнительные микросхемы для хранения признаков могут иметь другую структуру). Две микросхемы по 128кх8 поставить уже нельзя, так как нужна 32-разрядная шина данных, что могут обеспечить только четыре микросхемы. Распространенные РВ SRAM в 100-выводных корпусах РQFP имеют 32-разрядную структуру 32кх32 или 64кх32 и используются по две или четыре в платах для Pentium.

30-контактные SIMM имеют 8-разрядную структуру и используются с процессорами 286, 386SX и 486SLC по две, а с 386DX, 486DLC и обычными 486DX — по четыре. 72-контактные SIMM имеют 32-разрядную структуру и могут использоваться с 486 DX по одной, а с Pentium и Pentium Pro — по две. 168-контактные DIMM имеют 64-разрядную структуры и используются в Pentium и Pentium Pro по одной. Установка модулей памяти или микросхем кэша в количестве больше минимального для данной системной (материнской) платы позволяет ускорить работу с ними, используя принцип чередования (Interleave).

Время доступа характеризует скорость работы микросхемы и обычно указывается в наносекундах после тире в конце наименования. На более медленных микросхемах могут указываться только первые цифры (-7 вместо -70, -15 вместо -150), на более быстрых статических "-15" или "-20" обозначает реальное время доступа к ячейке. Часто на микросхемах указывается минимальное из всех возможных времен доступа, например, распространена маркировка 50 EDO DRAM вместо 70, или 45 вместо 60, хотя такой цикл достижим только в блочном режиме, а в одиночном режиме микросхема по-прежнему имеет время доступа 70 или 60 нс. Аналогичная ситуация имеет место и в маркировке РВ SRAM: 6 вместо 12 и 7 вместо 15. Микросхема SDRAM обычно маркируются временем доступа в блочном режиме (10 или 12нс).

ИМС памяти реализуются в корпусах следующих типов:

DIP (Dual In line Package — корпус с двумя рядами выводов) — классические микросхемы, применявшиеся в блоках основной памяти IBM PC/XT и ранних РС/АТ, сейчас применяются в блоках кэш-памяти.

SIP (Single In line Package — корпус с одним рядом выводов) — микросхема с одним рядом выводов, устанавливаемая вертикально.

SIPP (Single In line Pinned Package — модуль с одним рядом игольчатых выводов) - модуль памяти, вставляемый в панель наподобие микросхем DIP/SIP; применялся в ранних IBM PC/AT.

SIMM (Single In line Memory Module — модуль памяти с одним рядом контактов) - модуль памяти, вставляемый в зажимный разъем; применяется во всех современных платах, а также во многих адаптерах, принтерах и прочих устройствах. SIMM имеет контакты с двух сторон модуля, но все они соединены между собой, образуя как бы один ряд контактов. На SIMM в настоящее время устанавливаются преимущественно микросхемы FPM/EDO/BEDO.

DIMM (Dual In line Memory Module — модуль памяти с двумя рядами контактов)- модуль памяти, похожий на SIMM, но с раздельными контактами (обычно 2х84), за счет чего увеличивается разрядность или число банков памяти в модуле. Применяется в основном в компьютерах Apple и новых платах Р5 и Р6. На DIMМ устанавливаются микросхемы EDO/BEDO/SDRAM.

CELP (Card Egde Low Profile — невысокая карта с ножевым разъемом на краю) - модуль внешней кэш-памяти, собранный на микросхемах SRAM (асинхронный) или РВ SRAM (синхронный). По внешнему виду похож на 72-контактный SIMM, имеет емкость 256 или 512 Кбайт. Другое название — COAST (Cache On A STick - буквально "кэш на палочке").

Модули динамической памяти кроме основных ячеек памяти, могут иметь дополнительные ячейки для хранения битов четности (Parity) для байтов данных; такие SIMM иногда называют 9- и 36-разрядными модулями (по одному биту четности на байт данных). Биты четности служат для контроля правильности считывания данных из модуля, позволяя обнаружить часть ошибок (см. разд. 9.7). Модули с битами четности имеет смысл применять лишь там, где требуется повышенная надежность. Для обычных применений подходят и тщательно проверенные модули без битов четности, однако при условии, что системная плата поддерживает такие типы модулей.

Проще всего определить тип модуля по маркировке и количеству микросхем памяти на нем: например, если на 30-контактном SIMM две микросхемы одного типа и еще одна — другого, то две первых являются основными (каждая по четыре разряда), а третья предназначена для хранения битов четности (она одноразрядная). В 72-контактном SIMM с двенадцатью микросхемами восемь из них хранят данные, а четыре — биты четности. Модули с количеством микросхем 2, 4 или 8 не имеют памяти для хранения битов четности.

Иногда на модули ставится так называемый имитатор четности — микросхема-сумматор, выдающая при считывании ячейки всегда правильный бит четности; предназначена для установки в платы, где проверка четности не отключается.

72-контактные SIMM имеют четыре специальные линии PD (Presence t — обнаружение наличия), на которых при помощи перемычек может быть установлено до 16 комбинаций сигналов. Линии PD используются в некоторых материнских платах для определения наличия модулей памяти в разъемах и их параметров (объема и быстродействия). В большинстве универсальных плат производства "третьих фирм", как и выпускаемые ими SIMM, линии PD не используются.

В модулях DIMM в соответствии со спецификацией JEDEC технология PD реализуется при помощи перезаписываемого ПЗУ с последовательным доступом (Serial EEPROM) и носит название Serial Presence Detect (SPD). ПЗУ представляет собой 8-выводную микросхему, размещенную в углу платы DIMM, а его содержимое описывает конфигурацию и параметры модуля. Системные платы с набором микросхем (чипсетами) 440LX/BX могут использовать SPD для настройки системы управления памятью. Некоторые системные платы могут обходиться без SPD, определяя конфигурацию модулей обычным путем.

Лекция 21

Постоянная память

«Постоянное запоминающее устройства»

Цель:исследования и получение таблицы истинности ПЗУ с помощью Electronics Workbench.

Дата добавления: 2016-07-05; просмотров: 2178;